設(shè)計了一組基于CPLD的PLC背板總線協(xié)議接口芯片,協(xié)議芯片可以區(qū)分PLC的背板總線的周期性數(shù)據(jù)和非周期性數(shù)據(jù)。詳細(xì)介紹了通過Verilog HDL語言設(shè)計狀態(tài)機、協(xié)議幀控制器、FIFO控制器的過程,25MHz下背板總線工作穩(wěn)定的試驗結(jié)果驗證了協(xié)議芯片設(shè)計的可行性。

可編程邏輯控制器(PLC)主機是通過背板總線支持?jǐn)U展模塊的連接, 背板總線是PLC 主機同I/O擴展模塊之間的高速數(shù)據(jù)通路,支持主機和擴展模塊之間的I/O 數(shù)據(jù)刷新。背板總線的技術(shù)水平?jīng)Q定了PLC 產(chǎn)品的I/O 擴展能力,是PLC 設(shè)計制造的核心技術(shù)。目前,PLC 大多采用串行通信技術(shù)實現(xiàn)背板總線,串行總線引線少、硬件成本低,跟并行總線相比不容易受干擾,串行總線可以提高在惡劣的工廠和工業(yè)環(huán)境下自動化設(shè)備的可靠性。用于串行通信技術(shù)的可選類型包括I2C、UART、SPI、USB 和以太網(wǎng)等,一般來說,很多作為PLC 主芯片的單片機自身都集成了這些外設(shè)部件。但是單片機內(nèi)部集成的I2C、UART、SPI 外設(shè)通信速率太慢,根本不能滿足底板總線的通信速度要求。USB 和以太網(wǎng)的通信速度雖然很快但由于它們都是通用的接口,在通信協(xié)議處理時需要單片機的干預(yù), 單片機處理數(shù)據(jù)速度較慢,因此整體通信速度仍然很慢。一臺大型的PLC 采集上千點I/O 數(shù)據(jù)的時間一般不到1ms,要滿足如此高速的通信要求必須設(shè)計專門的背板總線。

1 背板總線工作原理

如圖1 所示,基于背板總線的數(shù)據(jù)通信流程如下:

(1)PLC 主機的命令通過主機協(xié)議芯片發(fā)送到背板總線;(2)從機協(xié)議芯片把接收到的命令給擴展模塊的單片機, 某一個擴展模塊的單片機做出應(yīng)答,通過從機協(xié)議芯片把應(yīng)答數(shù)據(jù)送往背板總線;(3)主機協(xié)議芯片收到應(yīng)答數(shù)據(jù),并送往PLC主機的單片機。

圖1 背板總線通信框圖

PLC 主機發(fā)往背板總線的數(shù)據(jù)可以分成兩類:一類是I/O 刷新數(shù)據(jù),具有周期性,數(shù)據(jù)交換非常頻繁;另一類是診斷性數(shù)據(jù),具有非周期性,出現(xiàn)機會較少。

2 協(xié)議芯片設(shè)計

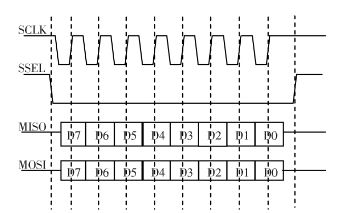

本設(shè)計定義背板總線采用類似SPI 串行通信的規(guī)格,用于通信的引線共4 根,包括時鐘信號SCLK、片選信號SSEL、寫數(shù)據(jù)引線MISO 和讀數(shù)據(jù)引線MOSI;支持主機和從機同時收發(fā)數(shù)據(jù),數(shù)據(jù)位格式如圖2 所示,數(shù)據(jù)幀在SSEL 信號為低電平時傳輸。

圖2 背板總線數(shù)據(jù)規(guī)格

主機和從機協(xié)議芯片的內(nèi)部結(jié)構(gòu)框圖相同,如圖3 所示。

協(xié)議芯片內(nèi)部有狀態(tài)機控制器、幀控制器、移位寄存器、接收/發(fā)送FIFO 和讀寫緩存。單片機發(fā)送的周期性、非周期性數(shù)據(jù)幀,首先都寫到寫緩存,在發(fā)送FIFO 中進(jìn)行排隊發(fā)送,在SPI 時鐘SCLK 的驅(qū)動下數(shù)據(jù)幀被轉(zhuǎn)換為串行數(shù)據(jù)發(fā)送到背板總線;在SPI 時鐘的作用下, 接收來自背板總線上的串行數(shù)據(jù);在狀態(tài)機和幀控制器的協(xié)調(diào)下,接收FIFO 中的有效數(shù)據(jù)幀被提取并放進(jìn)讀緩存區(qū),等待單片機來讀取,如果是非周期性數(shù)據(jù)則發(fā)中斷信號通知單片機來取數(shù)據(jù)。讀緩存中的周期性數(shù)據(jù)是可以覆蓋的,新接收到的周期性數(shù)據(jù)直接覆蓋舊的周期性數(shù)據(jù),而非周期性數(shù)據(jù)是單獨存放的,不能覆蓋,由單片機讀取并清除。

圖3 協(xié)議芯片內(nèi)部結(jié)構(gòu)框圖

協(xié)議芯片使得外接的單片機可以在空閑的情況下訪問讀緩存和寫緩存,單片機不必頻繁地通過中斷技術(shù)處理周期性數(shù)據(jù),也使得PLC 主機可以無等待地訪問從機的周期性數(shù)據(jù)。

3 基于CPLD 的協(xié)議芯片實現(xiàn)

3.1 CPLD 芯片選型。

本設(shè)計選用lattice 公司的MachXO 系列芯片,該系列CPLD 集成了部分FPGA 的功能, 除了內(nèi)置豐富的LUT 資源以外,還有大量分布式的SRAM 位和嵌入式的專用于FIFO 設(shè)計的SRAM 塊, 并有模擬鎖相環(huán)(PLL)支持時鐘信號的倍頻、分頻等,I/O引腳可配置成1.2/1.5/1.8/3.3V 電平兼容。

3.2 基于Verilog HDL 語言的硬件程序設(shè)計

本設(shè)計采用Verilog HDL 語言進(jìn)行協(xié)議芯片的程序設(shè)計,Verilog HDL 語言是一種硬件描述語言,設(shè)計數(shù)字芯片時可以按照層次描述,并可以進(jìn)行時序建模。本設(shè)計采用混合設(shè)計模式,主要設(shè)計的模塊有狀態(tài)機、協(xié)議幀檢測、FIFO 控制器設(shè)計等。

1)狀態(tài)機設(shè)計。

協(xié)議芯片的頂層模塊是狀態(tài)控制器部分,協(xié)議芯片共有四個狀態(tài), 分別處理基于Verilog HDL 程序語言的狀態(tài)機描述偽代碼如下:

2)協(xié)議幀檢測。

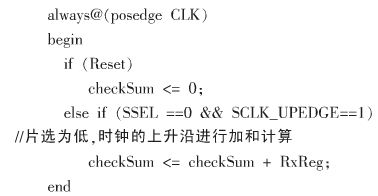

本協(xié)議芯片的幀校驗和采用簡單的加和形式進(jìn)行,在接收一方,如果數(shù)據(jù)幀中有用數(shù)據(jù)的加和同后續(xù)的校驗和字節(jié)相同,則協(xié)議是正確的,否則丟棄該幀。協(xié)議幀校驗和計算的代碼如下:

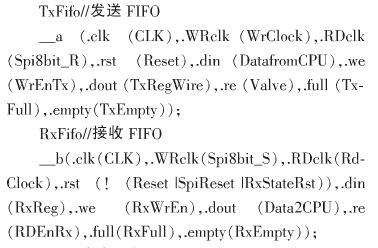

3)FIFO 設(shè)計。

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 塊的資源,Lattice 公司的ispLEVER 7.0 軟件提供了可配置的IP 軟核,該軟核可以采用基于嵌入式SRAM 塊實現(xiàn), 也可以使用查找表實現(xiàn),F(xiàn)IFO 的IP 核框圖如圖4 所示,F(xiàn)IFO 的可配置參數(shù)包括FIFO字節(jié)深度、EmptyFull、Almostempty 和AlmostFull觸發(fā)字節(jié)深度、數(shù)據(jù)寬度、大小端模式等。

圖4 可配置FIFO 控制器IP 軟核框圖

用Verilog HDL 語言實現(xiàn)的發(fā)送和接收FIFO控制器的實例代碼如下:

3.3 協(xié)議芯片綜合

Verilog HDL 程序通過Lattice 公司的CPLD 開發(fā)軟件ispLEVER 7.0 進(jìn)行編譯、綜合,多次嘗試后最終選擇了Lattice 公司MachXO 系列CPLD 中的MachXO2280 芯片, 綜合后的主機協(xié)議芯片占用CPLD 資源的60%左右, 從機協(xié)議芯片占用CPLD資源的45%左右,F(xiàn)IFO 控制器充分利用了MachXO2280芯片內(nèi)部的嵌入式RAM 塊, 同時利用了鎖相環(huán)實現(xiàn)高頻率的時鐘工作。最后通過LSC ispVM(R)System 燒寫軟件經(jīng)JTAG 口下載到CPLD 芯片中進(jìn)行協(xié)議芯片功能驗證測試。

4 結(jié)語

本文設(shè)計的背板總線協(xié)議芯片在背板串行總線時鐘頻率為25MHz、信號電平為LVTTL,底板引線長度為40cm,1 臺主機連接3 臺擴展模塊的情況下工作穩(wěn)定并通過了群脈沖試驗,驗證了這一組協(xié)議芯片的設(shè)計是成功的。由于該組協(xié)議芯片是針對PLC 的周期性和非周期性數(shù)據(jù)傳送專門設(shè)計的,硬件實現(xiàn)的協(xié)議幀控制器支持高速率通信、支持?jǐn)?shù)據(jù)幀檢驗功能,避免了數(shù)據(jù)傳送的錯誤,大大降低了外圍單片機的軟件開銷,增強了可靠性,是一組非常適合用于PLC 背板總線或者需要多模塊協(xié)同工作的背板總線系統(tǒng)協(xié)議芯片。