近年來,隨著信息技術的發(fā)展,網(wǎng)絡化日加普遍,以太網(wǎng)被廣泛應用到各個領域。例如在數(shù)據(jù)采集領域,一些 小型監(jiān)測設備需要增加網(wǎng)絡實現(xiàn)遠程數(shù)據(jù)傳輸?shù)墓δ埽灰切┰O備上增加一個網(wǎng)絡接口并實現(xiàn)了TCP/IP協(xié)議,就可以方便地接入到現(xiàn)有的網(wǎng)絡中,完成遠程 傳輸數(shù)據(jù)的相關功能,所以小型設備的網(wǎng)絡技術一直是大家關注的焦點。另一方面,隨著單片FPGA的邏輯門數(shù)不斷增大,人們開始考慮將整個嵌入式系統(tǒng)集成到 單片F(xiàn)PGA來實現(xiàn),于是2001年Altera第一次提出了可編程片上系統(tǒng)(SOPC)概念,并且推出了第一款嵌入式處理器軟核Nios以及之后的第二 代NiosII以及相應的開發(fā)環(huán)境,此后Xilinx也推出了MicroBlaze微處理器軟核,之后,隨著Altera的CycloneIII和 StraTIxIV以及Xilinx的Spartan6和Virtex6等一系列大容量FPGA的推出,Xilinx于2009年正式提出了目標平臺設計 并且推出了相應的軟件ISE11,至此,嵌入式系統(tǒng)真正開始走向了片上系統(tǒng),自然,這中間也包括了以太網(wǎng)的嵌入式片上系統(tǒng)。

Matlab是美國MathWorks 公司提供的商業(yè)數(shù)學仿真軟件,其中Simulink是Matlab中的一種可視化仿真工具,是一種基于框圖的設計環(huán)境,可以實現(xiàn)數(shù)據(jù)的仿真和處理,它提供 了一種快速、直接明了的方式,用戶可以實時看到系統(tǒng)的仿真結果并且進行相應的數(shù)據(jù)處理。基于以上事實,本文提出了基于FPGA的嵌入式以太網(wǎng)與 Matlab通信系統(tǒng)的設計和研究,采用Xilinx公司的MicroBlaze嵌入式微處理器軟核,利用它和相應外設IP核一起完成SOPC的設計并且 完成與Simulink數(shù)據(jù)的傳輸,最后動態(tài)顯示以太網(wǎng)傳輸?shù)臄?shù)據(jù)。

系統(tǒng)硬件平臺設計

1、系統(tǒng)總體硬件的結構

在系統(tǒng)硬件結構中,考慮到系統(tǒng)復雜度和成本因素,我們選用了Xilinx公司的Spatan3A系列的XC3S700A作為主控制芯片,該芯片為 Xilinx的Spartan系列的低端FPGA,采用了65nm技術,在集成度和性價比上都要優(yōu)于先前Spartan系列的FPGA,系統(tǒng)外掛一塊 Micron公司的32M×16bits的DDR2芯片MT47H32M16作為外擴SDRAM,以及一片Numonyx公司的16Mb的 SPIFlashM25P16作為數(shù)據(jù)存儲器,而10/100Mb以太網(wǎng)我們采用單片PHY芯片加Xilinx的MAC軟核來實現(xiàn)。該方案將物理層和 MAC分開,將MAC用IP來實現(xiàn),從而整個系統(tǒng)更加靈活。其中單片PHY芯片有BroADCom公司的BCM5221,Intel公司的 LXT971A、LXT972A,SMSC公司的DM9000、LAN83C185等。這里我們采用SMSC公司的LAN83C185來實現(xiàn)物理層。

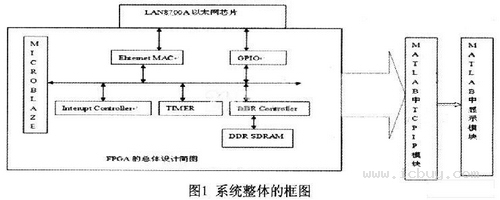

2、系統(tǒng)整體框圖

雖然Matlab中可以采用相關命令創(chuàng)建一個TCP/IP的模塊進行數(shù)據(jù)的接收和顯示,但是與Simulink中TC/IP模塊相比較為繁鎖,因此選擇 用后者動態(tài)實時顯示從以太網(wǎng)發(fā)送過來的數(shù)據(jù),并可進行相應的處理。本設計主要是完成發(fā)送正弦函數(shù)數(shù)據(jù)并在Simulink的接收模塊中顯示正弦函數(shù)圖形。 系統(tǒng)的整體的框圖如圖l所示:

MicroBlaze的系統(tǒng)硬件配置和Simulink接收塊的搭建

1、MicroBlaze和系統(tǒng)設計

Xilinx公司的MicroBlaze嵌入式軟核是業(yè)界優(yōu)秀的32位軟處理器IP核之一,它支持CroConnect總線標準設計集合,具有兼容性和 重復利用性,最精簡的核只需要400個左右的Slice,MicroBlaze軟核內(nèi)部采用哈佛結構的32位指令和數(shù)據(jù)總線,便于各個外設和它們之間的信 號傳輸及相應的控制,它有下面的幾種互聯(lián)總線:

(1)處理器本地總線(PLB)。可以將多個PLB主設備和PLB從設備連接到整個的PLB系統(tǒng)中。

(2)高速的本地存儲器總線(LMB)。用來取RAM塊的同步總線。

(3)XCL總線。是一個高性能的外部內(nèi)存訪問總線。

(4)FSL總線。用于點對點的單向通信總線。

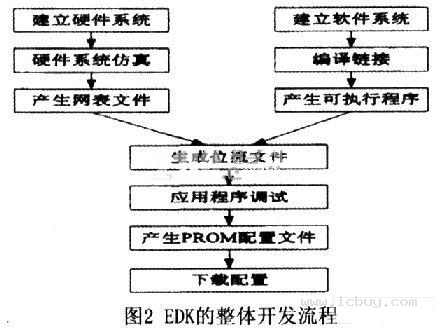

使整個系統(tǒng)的軟硬件設計,包括系統(tǒng)硬件平臺的搭建,驅動程序的配置,Xilkernel操作系統(tǒng)內(nèi)的核參數(shù)配置,軟件庫的設置,文件系統(tǒng)的生成及外設控 制芯片接口配置都可以在EDK(EmbeddedDevelopmentKit)內(nèi)完成。EDK的整體開發(fā)流程如圖2所示。

整個系統(tǒng)設計具體操作如下:

(1)在EDK的集成開發(fā)環(huán)境XPS(XilinxPlatform.Studio)中,處理器功能單 元,系統(tǒng)外圍總線結構,終端外設以及相應的地址映射和默認的驅動等都可以在BSB(BaseSystemBuilder)中完成。在Microblaze 系統(tǒng)的基本構建中其主要設置如下:使用SingleProcessorSystem系統(tǒng),LocalMemory為16k,系統(tǒng)時鐘頻率為 62.5MHz,定時器和以太網(wǎng)中斷必須連接到處理器的中斷控制器上,另外,本設計還用到的GIOP、EthernetMAC、DDR、SDRAM控制器 等,其間用到的IP驅動,都是用xilinx提供IP的自帶默認的相應驅動。

(2)最后XPS自動生成微處理器硬件 規(guī)范MHS(MicroprocessorHardwareSpecificaTIon)和描述軟件系統(tǒng)結構的微處理器軟件規(guī)范MSS(Micro- processorSoftwareSpecification)文件以及一些相關的文件。這些文件都可以手動進行修改,從而是使整個系統(tǒng)更加的優(yōu)化。

(3)生成的系統(tǒng)最后生成bit文件,把其文件下載到目標板子上。

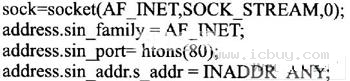

2、Simulink接收模塊的搭建

Simulink中TCP/IP中的接收模塊,其終端的地址,端口的設置要與FPGA上的以太網(wǎng)的IP地址、端口的設置一致,這就為TCP/IP接收模 塊指定了要通信的地址即完成了接收模塊TCP/IP的相關配置,也就完成了FPGA與Matlab中以太網(wǎng)通信的接收模塊的搭建,在Simulink中, 具體的模塊設計如圖3所示。

通信數(shù)據(jù)通過此模塊可以較直觀地用圖形動態(tài)顯示。

系統(tǒng)的軟件平臺及網(wǎng)絡協(xié)議的實現(xiàn)

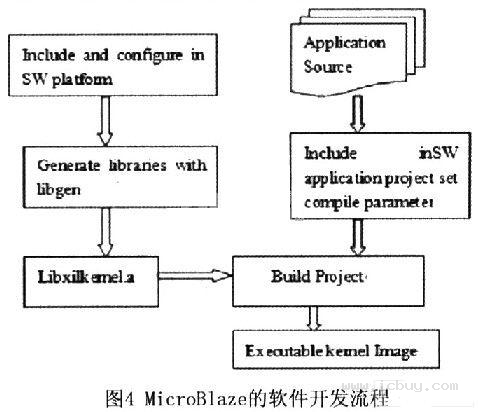

1、軟件內(nèi)核和協(xié)議

本設計主要選擇了Xilinx公司的精簡嵌入式操作系統(tǒng)Xilkemel,它是Xilinx提供的用于EDK系統(tǒng)的小型、模塊化的嵌入式操作系統(tǒng)內(nèi)核, 它支持Microblaze核,與EDK形成的硬件系統(tǒng)無縫連接,具有可定制、CPU資源占用較小、運行速度快等特點,是MicroBlaze嵌入式軟核 的理想操作系統(tǒng),其整體的開發(fā)流程如圖4所示。

網(wǎng)絡通訊協(xié)議我們采用TCP/IP協(xié)議,該通訊協(xié)議采用四層(應用層、傳輸層、互連網(wǎng)絡層、網(wǎng)絡接口層)層級結構,每一層都呼叫它的下一層所提供的網(wǎng)絡來完成自己的需求,系統(tǒng)分為兩部分實現(xiàn):

第一部分為物理層和MAC層,本設計中用LAN83C185來實現(xiàn)物理層,MAC層由Xilinx公司的EthernetMACIP核,并作為整個MicroBlaze系統(tǒng)硬件的一部分在FPGA內(nèi)實現(xiàn)。

第二部分是運輸層和網(wǎng)際層,主要由軟件代碼實現(xiàn)。TCP/IP網(wǎng)絡通信軟件允許用戶遠程注冊到另一個系統(tǒng)中,并從一個系統(tǒng)復制文件到另一個系統(tǒng),雖然 Xilkernel本身不帶有文件處理系統(tǒng)和TCP/IP協(xié)議棧,但它與Xilinx公司的LwIP庫具有良好的接口,加上系統(tǒng)支持庫LibXilMFS 可形成一個比較完整的嵌入式系統(tǒng),其特點是內(nèi)核配置功能都已集成到EDK工具中,使用簡單、方便,內(nèi)核啟動靜態(tài)創(chuàng)建線程,而動態(tài)分配內(nèi)存,可加載或卸載不 同功能模塊來實現(xiàn)內(nèi)核的高擴展性。

本設計主要采用LwIP3.OOb(LightweightInternetProtocolstack)協(xié)議模塊套用于嵌入式系統(tǒng)的開放源代碼 TCP/IP協(xié)議棧中,LwI-P3.00b提供二種API模式:Socket模式和RWA模式,由于Socket模式開發(fā)難度不大,只要啟動 Xemacifinputthread線程,從中斷響應的過程中接收數(shù)據(jù)包并轉移到LwlP的tepipthread中就可以。所以基于方便考慮我們決定 上層協(xié)議部分協(xié)議模塊采用Socket模式,因此需在MSS文件里對LwIP進行例化(包括相應的LwIP參數(shù)設置)從而減少存儲器利用量和代碼編寫。

2、網(wǎng)絡通信程序的實現(xiàn)與設計

網(wǎng)絡通信程序主要完成從超極終端發(fā)送數(shù)據(jù),傳到Simulink中的ICP/IP接收模塊。下面是主要的網(wǎng)絡通信程序:

Server_thread()函數(shù)是Xilkernel的第一個線程,初始化LwIP協(xié)議棧。

ServerAppThread()函數(shù)可完成MAC、IP、掩碼以及網(wǎng)關的配置,并完成Socket應用。

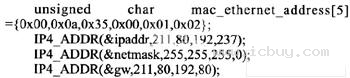

以太網(wǎng)的配置如下:

當服務器程序開始運行時,主進程就創(chuàng)建一個套接字,

并通過bind函數(shù)綁定,用函數(shù)listen進行*,之后用lwip_accept進行接收,然后用 sys_thread_new啟動進程,processGet和ProcessCommand函數(shù)分析數(shù)據(jù)包的內(nèi)容并應用webserber定義的相關的 命令實現(xiàn)相關的應用,write函數(shù)實現(xiàn)數(shù)據(jù)的發(fā)送,完成Socket服務并把數(shù)據(jù)發(fā)送給客戶端。

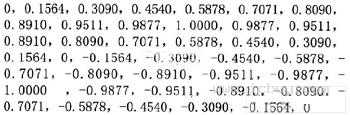

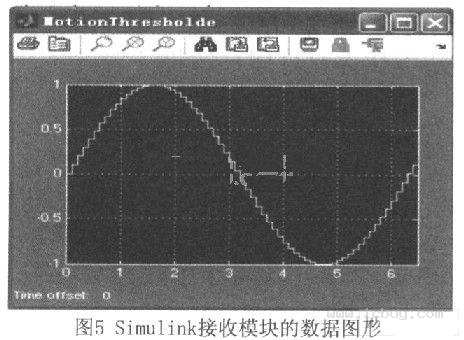

Simulink中用TCP/IP模 塊,remoteaddress參數(shù)設定為(211、80、192、237),端口設定為80,即與 IP4_ADDR(&ipaddr,211,80,l92,237)和address.sinport="htons"(80)設為一致,這樣就保證了接 收與發(fā)送網(wǎng)絡地址和端口的一致性,保證數(shù)據(jù)傳輸?shù)目蓪崿F(xiàn)性。設計發(fā)送的數(shù)據(jù)為:t=0:0.25:10,Y=sin(2*pi/10*t),數(shù)據(jù)列表如 下:

對應的Simulink接收模塊的數(shù)據(jù)圖形顯示如圖5所示。

由圖5我們可以看出,接收到的數(shù)據(jù)和發(fā)送的數(shù)據(jù)基本一致。

結論

本文研究了TCP/IP通信協(xié)議在Xilinx公司FPGA上的實現(xiàn),介紹了其軟硬件的系統(tǒng)組成及原理,通過建立一個例子加以說明和應用這個設計平臺, 證明了此平臺設計可行性,并且完成了FPGA與Matlab的通信,為數(shù)據(jù)的實時顯示及實時控制提供了很好的平臺和設計方法,本設計也完成了CPU軟核設 計的實現(xiàn),其功能可根據(jù)需要進行定制,非常靈活,不但引入了軟核處理器和嵌入式操作系統(tǒng)Xilkernel,而且應用了Lw-IP_300b棧,使用大量 的IP核,這樣大大降低了系統(tǒng)平臺的復雜度,縮短了開發(fā)的周期,其軟硬件部分的設計分離的設計架構,使得整個系統(tǒng)修改和重構更加方便,真正實現(xiàn)了所謂的片 上系統(tǒng)。而本設計采用Matlab接收數(shù)據(jù),并且可利用其強大的數(shù)據(jù)采集、處理、仿真、實時動態(tài)顯示的功能來更好完成數(shù)據(jù)分析研究。