在傳統(tǒng)的嵌入式多處理器系統(tǒng)中,處理器之間的互連是通過(guò)分時(shí)共享總線來(lái)實(shí)現(xiàn)的,所有通信爭(zhēng)用總線帶寬,由此就造成處理器越多,每個(gè)處理器可用帶寬就越少, 從而帶來(lái)嚴(yán)重的系統(tǒng)信息傳輸能力瓶頸。并且總線具有大量的引腳數(shù)目,帶來(lái)了一定的電氣特性和機(jī)械特性等問(wèn)題,使得信號(hào)頻率以及信號(hào)可傳輸距離都受到很大程 度的制約。

RapidIO總線技術(shù)是一種基于高性能包交換的互連技術(shù),具有極低的延遲(納秒級(jí))和高帶寬。RapidIO總線技術(shù)的提出 消除了帶寬這個(gè)瓶頸問(wèn)題,成功解決了處理器集成芯片之間和線路板之間互連問(wèn)題。目前RapidIO已經(jīng)成為唯一的一個(gè)系統(tǒng)內(nèi)串行互連協(xié)議標(biāo)準(zhǔn),世界各大半 導(dǎo)體公司都陸續(xù)推出了基于RapidIO技術(shù)的相關(guān)產(chǎn)品,基于RapidIO通信體系架構(gòu)技術(shù)的系統(tǒng)已在電信、國(guó)防、醫(yī)療等行業(yè)大量使用。

當(dāng)前在一個(gè)高速嵌入式多處理器系統(tǒng)內(nèi)一般由PPC、DSP和FPGA等處理器構(gòu)成。本文對(duì)FPGA的RapidIO節(jié)點(diǎn)設(shè)計(jì)進(jìn)行了功能測(cè)試和驗(yàn)證。

2 RapidIO 技術(shù)概述

RapidIO可提供10Gbps以上的帶寬(RapidIO 2.0規(guī)范可提供100Gbps帶寬),其所有的協(xié)議都是由硬件實(shí)現(xiàn)的,與軟件無(wú)關(guān)。適合用于芯片與芯片、板與板、系統(tǒng)與系統(tǒng)之間的高速數(shù)據(jù)傳輸。

RapidIO 協(xié)議采用三層分級(jí)體系結(jié)構(gòu)。邏輯層規(guī)范位于最高層,定義全部協(xié)議和包格式,它們?yōu)槎它c(diǎn)器件發(fā)起和完成事務(wù)提供必要的信息。傳輸層規(guī)范在中間層,定義 RapidIO地址空間和在端點(diǎn)器件間傳輸包所需的路由信息。物理層規(guī)范在整個(gè)分級(jí)結(jié)構(gòu)的底部,包括器件級(jí)接口的細(xì)節(jié),如包傳輸機(jī)制、流量控制、電氣特性 和低級(jí)錯(cuò)誤管理。

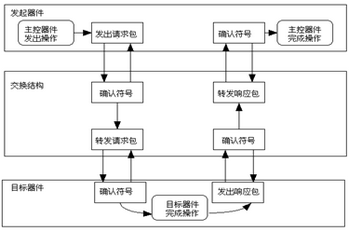

RapidIO的傳輸操作是基于請(qǐng)求和響應(yīng)機(jī)制,傳輸操作可以在包傳輸間歇插入控制符。包(PACKET)是系統(tǒng)中端點(diǎn) 器件的通信單元。由發(fā)起者(intiator)產(chǎn)生一個(gè)傳輸請(qǐng)求,請(qǐng)求包被傳輸?shù)较噜彽慕粨Q器件,從而進(jìn)入交換機(jī)構(gòu),通過(guò)交換機(jī)構(gòu)這個(gè)完整的請(qǐng)求包被傳輸 到目標(biāo)器件(target),目標(biāo)器件根據(jù)請(qǐng)求完成相應(yīng)的操作后,發(fā)送相應(yīng)的響應(yīng)包,經(jīng)過(guò)交換機(jī)構(gòu)傳回到發(fā)起者,這時(shí)一個(gè)完整的傳輸過(guò)程完成。控制符一般 在物理層互連中用作傳輸管理,如包的確認(rèn)、流控信息和維護(hù)功能等。如圖1所示。

圖1 RapidIO的傳輸操作

RapidIO 的三層體系結(jié)構(gòu)可以將不同的單元互連起來(lái),不同的單元之間以包的形式進(jìn)行通信。這樣的互連網(wǎng)絡(luò)可以有很靈活的系統(tǒng)拓?fù)洌S玫氖腔诮粨Q的互連系統(tǒng)。一個(gè) 包從一個(gè)處理單元送到另一個(gè)處理單元是通過(guò)交換單元進(jìn)行的,交換單元通過(guò)對(duì)包格式里的傳輸字段進(jìn)行譯碼,而得到包所要到達(dá)哪個(gè)處理單元。由于通常一個(gè)請(qǐng)求 包對(duì)應(yīng)一個(gè)響應(yīng)包,所以包格式里的傳輸字段還要定義響應(yīng)包的返回路徑。

3 RapidIO的FPGA節(jié)點(diǎn)實(shí)現(xiàn)

典 型的系統(tǒng)網(wǎng)絡(luò)由PPC、DSP和FPGA三種節(jié)點(diǎn)構(gòu)成。隨著CPU、DSP和FPGA等處理器的性能得到較大提升,提高連接這些高性能器件的總線性能成為 提升系統(tǒng)性能的關(guān)鍵。在一些處理器、系統(tǒng)邏輯、FPGA和ASIC中都已經(jīng)實(shí)現(xiàn)了RapidIO技術(shù),如Xilinx公司已經(jīng)出售RapidIO的終端接 口邏輯IP核;TI公司的DSP芯片TMS320C6455內(nèi)部集成了串行RapidIO外設(shè);Motorola公司已經(jīng)推出的 PowerQUICCIII處理器中集成了RapidIO接口邏輯;Tundra公司提供8端口的串行1x/4x的 RapidIO交換芯片Tsi568A和RapidIO橋接芯片。這里討論FPGA中RapidIO節(jié)點(diǎn)的實(shí)現(xiàn)。

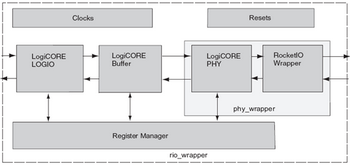

RapidIO網(wǎng)絡(luò)中FPGA上的RapidIO節(jié)點(diǎn),可以采用Xilinx RapidIO解決方案實(shí)現(xiàn)。Xilinx RapidIO解決方案如圖2所示,它由物理層核,邏輯傳輸層核、緩沖器核和參考設(shè)計(jì)4個(gè)部分組成。其中參考設(shè)計(jì)控制時(shí)鐘、復(fù)位和配置空間的存取。

圖2 Serial RapidIO 功能框圖

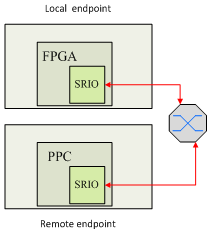

邏 輯層和傳輸層接口如圖3所示。邏輯層通過(guò)Xilinx特有的本地Link接口與物理層相連,以構(gòu)成RapidIO節(jié)點(diǎn)。邏輯層分為幾個(gè)模塊來(lái)控制發(fā)送和接 收包的串接和解析。其中用戶(hù)接口(User InteRFace)包含4個(gè)端口 (Initiator Request, Initiator Response, Target Request 和Target Response) ,從這里向remote節(jié)點(diǎn)發(fā)送包或接收remote節(jié)點(diǎn)發(fā)送的包,它是使用Xilinx SRIO解決方案時(shí)用戶(hù)通信使用的接口。還可以從這些端口發(fā)起到本節(jié)點(diǎn)配置寄存器的讀寫(xiě)操作。維護(hù)接口包含

2個(gè)端口(Maintenance Request/Response Port和Configuration Register Port),控制對(duì)邏輯層的配置寄存器以及用戶(hù)定義寄存器或物理層配置寄存器的讀寫(xiě)。

圖3 邏輯層和傳輸層接口

4 驗(yàn)證設(shè)計(jì)實(shí)例

FPGA 芯片選擇Xilinx的V5系列的芯片XC5VLX110T,它內(nèi)置了16個(gè)RocketIO收發(fā)器,支持從100Mbps到3.75Gbps串行數(shù)據(jù)傳 輸速率,支持目前流行的包括RapidIO在內(nèi)的高速串行I/O接口標(biāo)準(zhǔn)。能夠在它的基礎(chǔ)上實(shí)現(xiàn)RapidIO高速串行數(shù)據(jù)傳輸系統(tǒng)。在程序中還通過(guò)添加 VIO核以方便控制消息、門(mén)鈴等的發(fā)送。試驗(yàn)平臺(tái)構(gòu)架如圖4所示,在FPGA中通過(guò)ChipScope來(lái)觀察相關(guān)信號(hào)進(jìn)行驗(yàn)證。

圖4 調(diào)試環(huán)境

通過(guò)遠(yuǎn)端ppc節(jié)點(diǎn)向fpga發(fā)門(mén)鈴和消息,chipScope在fpga接收端口Target Request得到的結(jié)果如圖5,圖6所示,觸發(fā)信號(hào)選用幀起始標(biāo)記treq_sof_n。由圖可見(jiàn)FPGA的rapidIO節(jié)點(diǎn)可以正確的接收消息和門(mén)鈴。

圖5 門(mén)鈴試驗(yàn)結(jié)果

圖6 消息試驗(yàn)結(jié)果

5 結(jié)束語(yǔ)

RapidIO互連有效的應(yīng)對(duì)了高性能嵌入式系統(tǒng)在可靠性和互連性方面的挑戰(zhàn)。這里使用Xilinx公司的rapidIO解決方案實(shí)現(xiàn)了系統(tǒng)中FPGA的RapidIO節(jié)點(diǎn),在新一代通信及數(shù)據(jù)網(wǎng)絡(luò)應(yīng)用中具有廣泛的應(yīng)用背景