概覽

無線設備的數(shù)量、通信標準的多樣性,以及調制方案的復雜度,每一年都在不斷增加。而隨著每一代新技術的誕生,由于使用傳統(tǒng)技術測試無線設備,需要大量更復雜的測試設備,其成本也在不斷提高。

使用虛擬(軟件)儀器與模塊化I/O相結合是一種最小化硬件成本并減少測試時間的方法。軟件設計儀器的新方法使得射頻測試工程師無需憑借自定義或特殊標準的儀器,就能以多個數(shù)量級的幅度減少測試時間。

閱讀此文可以幫助您了解如何使用NI LabVIEW FPGA來設計和自定義您的射頻儀器,以及通過軟件設計的儀器能為您的測試系統(tǒng)所帶來的好處。

軟件設計儀器簡介

多年來,測試工程師一直在運用諸如LabVIEW的軟件包來實現(xiàn)自定義射頻測量系統(tǒng),并與傳統(tǒng)封裝儀器相比盡可能地減少成本。使用軟件設計的方法不僅提供了強大的靈活性,更能使測試工程師利用到最新的PC,CPU和總線技術所帶來的性能提升。

CPU成為了許多高要求射頻測試應用的瓶頸,CPU有限的并行機制和軟件棧將會導致延時,對于有些需要根據(jù)測量值或待測設備(DUT)的狀態(tài)而動態(tài)調整測試激勵的應用,就會影響到測試效果。為了達到最理想的射頻測試系統(tǒng)效果,需要結合使用自定義儀器硬件和多核技術,這也能使測試系統(tǒng)設計人員得以找到低延時和高吞吐量之間的平衡點,從而大幅減少測試時間。

雖然現(xiàn)成即用的儀器硬件的性能早已被改善,NI仍然致力于運用現(xiàn)場可編程門陣列(FPGA)技術提供更加開放和靈活的測試設備。簡而言之,F(xiàn)PGA是一種用戶可以自定義的高密度的數(shù)字芯片,可以使得測試工程師將他們的自定義信號處理方法和控制算法結合到測試硬件中。因此,即成可用的射頻硬件包含了諸多優(yōu)點:高質量的測量技術,且在其最新的構件中包含了可靠的,可溯源的測量方法,通過與高度并行的用戶自定義邏輯相結合,可以產生較低的延遲,并且它能夠與I/O直接連接以用于在線處理和嚴格的控制環(huán)路。

關于此類硬件的一個案例是NI PXIe-5644R vector signal transceiver (VST)。該設備融合了矢量信號發(fā)生器和矢量信號分析儀的功能,并包含了一個用戶可編程FPGA來用于實時信號處理和控制。由于FPGA賦予其更多的靈活性,VST非常適合用于自定義觸發(fā),待測設備控制,并行測試和實時數(shù)字信號處理(DSP)。

使用LabVIEW FPGA將LabVIEW的運用擴展至硬件自定義

雖然FPGA已廣泛用于自定義主板設計或是即成可用設備的一部分,但用戶自定義FPGA迄今為止還未被大量用于即成可用的射頻儀器設備中。這主要是因為對這些設備進行編程需要擁有專業(yè)的背景知識。硬件描述語言或HDL,通常學習起來非常困難,唯有數(shù)字電路設計專家才能勝任。

LabVIEW FPGA模塊可以幫助大量的工程師和科學家接觸到最新的FPGA技術。使用圖形化編程方法,用戶可以在硬件中實現(xiàn)邏輯定義射頻儀器的行為。事實上,LabVIEW的圖形化數(shù)據(jù)流的特性非常適合用于實現(xiàn)并視覺化呈現(xiàn)那些可在FPGA上進行的并行操作。雖然使用LabVIEW對FPGA編程還是略有區(qū)別,也需要進行額外的學習,但其難度將明顯小于學習HDL的難度。

圖1,使用LabVIEW FPGA模塊,用戶可以使用熟悉的LabVIEW代碼對儀器硬件進行自定義。對于射頻應用,用戶可以以預創(chuàng)建的范例項目為基礎,添加相應修改以實現(xiàn)自定義觸發(fā),待測設備控制,信號處理等功能。

許多LabVIEW FPGA的范例項目都可以作為您射頻應用的起始點,并且這些項目也能在諸如NI PXIe-5644R VST之類的設備上使用。值得一提的是,用戶可以根據(jù)儀器數(shù)據(jù)移動模式(與矢量信號分析儀或發(fā)生器擁有相似的自定義開始,停止和參考觸發(fā)顯示界面),或者根據(jù)數(shù)據(jù)流模式(適用于在線信號處理或者錄制和回放應用)對FPGA進行自定義。

軟件設計儀器與傳統(tǒng)方法的對比

在射頻測量系統(tǒng)中運用基于FPGA的硬件可以帶來從低延時待測設備的控制到減少CPU負載等諸多好處。在下文中將介紹更多不同應用的詳細情況。

使用交互式待測設備控制方法,提高測試系統(tǒng)的整合度

在許多射頻測試系統(tǒng)中,需要使用數(shù)字信號或自定義協(xié)議來控制需要被控制的設備和芯片。傳統(tǒng)的自動化測試系統(tǒng)可以通過待測設備的模式進行排序,在每一個不同的階段進行所需的測量工作。有些智能型的自動化測試儀器(ATE)系統(tǒng)可以根據(jù)接收到的測量值在待測設備設置之間進行排序。

對于任意兩種情況,包含了FPGA的軟件設計儀器都可以降低成本并減少測試時間。將測量處理和數(shù)字控制整合至一個儀器中可以降低系統(tǒng)對其他數(shù)字I/O的需求,并且也無需在儀器間對觸發(fā)進行配置。對于有些必須根據(jù)接受到的測量數(shù)據(jù)進行控制的待測設備,軟件設計儀器可以在硬件中關閉循環(huán),以減少因在軟件中進行決策所帶來的高延時。

使用硬件測量減少測試時間,提高測試可靠性

雖然當今基于軟件的測試系統(tǒng)只能對有限數(shù)量的測量進行并行處理,但只要通過FPGA邏輯,軟件設計儀器可以毫無限制地實現(xiàn)并行處理。通過硬件并行機制可以處理大量的測量任務或數(shù)據(jù)通道,而無需對指定的測量任務進行挑選。諸如快速傅里葉變換、濾波、調制和解調等計算,可以在硬件中進行,由此可以減少CPU的數(shù)據(jù)傳送量和處理量。諸如實時頻譜屏蔽之類的功能,使用軟件設計儀器,可以比使用傳統(tǒng)封裝儀器獲得更高的速率。

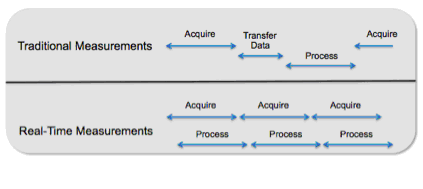

此外,在硬件中執(zhí)行測量任務的低延時意味著在同樣的時間內,標準測試系統(tǒng)可能只能要求完成一個測量任務,但其卻可以同時進行數(shù)十個甚至上百個實時測量任務,從而提高測試結果的質量并增加射頻測試的可靠程度。而且,由于測量任務可以在硬件中連續(xù)執(zhí)行,并周期性地從主機測試程序中進行采樣,用戶可以完全不用擔心遺漏任何重要的數(shù)據(jù)。

圖2. 使用軟件設計儀器,用戶可以連續(xù)采集數(shù)據(jù)并執(zhí)行測試(定期采樣測試結果),而無需停止采集過程來傳輸信息。

通過閉環(huán)反饋快速達到最理想的測試條件

某些射頻測試要求待測設備設置或環(huán)境和生產處理的數(shù)量需要根據(jù)所接收到的測量任務進行改變;這就需要一個閉環(huán)系統(tǒng),但其常常由于軟件棧的延時而受到限制。在許多情況下,可以在硬件中直接閉環(huán),從而使得CPU無需再計算下一個定位點。這樣可以將閉環(huán)測試時間從數(shù)十秒減少至零點幾秒。

通過用戶自定義觸發(fā)來處理特定的數(shù)據(jù)

使用儀器型硬件已解決了觸發(fā)行為的延時問題。然而,通過使用軟件設計的儀器,用戶可以將自定義觸發(fā)功能集成到設備中,從而可以在特定情況下快速執(zhí)行命令。靈活的基于硬件的觸發(fā)意味著用戶可以在捕捉重要的測量數(shù)據(jù)或激活其他的儀器設備時,將自定義頻譜屏蔽或其他復雜的條件設置為標準。并且,通過選擇硬件中特定的數(shù)據(jù)可以使得用戶解放CPU以用于其他重要的任務。

在設計過程中合理運用軟件投資

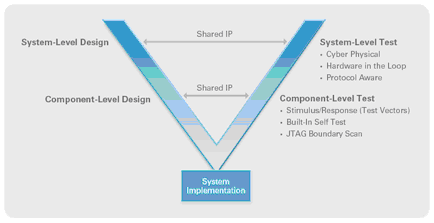

雖然本文內容主要有關射頻測試,但工程師也越來越多地在設計和測試階段反復地使用IP,縮短產品上市周期并大幅減少測試總體費用。通過LabVIEW FPGA,可以對數(shù)字信號處理算法進行定義,并可將其視為設備的一部分或元件確認而重復運用,從而無需再從頭開始編寫測試代碼。這能夠加速測試的開發(fā)(在設計環(huán)節(jié)的初期即可開始進行測試),同時也使得測試覆蓋的范圍更加完整。

圖3. IP可以在設計和測試階段反復使用,從而減少測試的開發(fā)時間并提供更加完整的測試范圍

永不過時的軟件設計儀器

在未來幾年中,廠商定義的儀器和功能固定的即用儀器將毫無疑問地繼續(xù)存在。然而,越來越多復雜的射頻設備和產品上市時間的壓力已推動了基于軟件的儀器系統(tǒng)的不斷增加,這些趨勢的延續(xù)意味著在不久的將來,軟件設計儀器將逐漸在射頻測試,乃至在所有的測試儀器中,扮演一個不可或缺的重要角色。

軟件設計儀器提供了高度的靈活、優(yōu)質的性能,以及采用即時可用硬件而具備的永不過時性。當系統(tǒng)要求改變時,軟件設計儀器的軟件投資將通過不同的模塊化I/O得以保留,而現(xiàn)有的I/O也可以根據(jù)實際應用而隨時改變。

了解VST的詳情請訪問www.ni.com/vst/zhs