隨著集成電路設計技術和深亞微米制造技術的發(fā)展,集成電路已進入了片上系統(tǒng)時代。由于SoC結(jié)構(gòu)極其復雜,對于設計者而言,數(shù)百萬門規(guī)模的系統(tǒng)級芯片設計不可能一切從頭開始,隨著集成電路設計技術的發(fā)展,IP核的開發(fā)己成為不可忽視的發(fā)展趨勢,它的出現(xiàn)為SoC的實現(xiàn)和發(fā)展提供了基礎。IP稱之為知識產(chǎn)權(quán),它可以認為是封裝在硬件設計中的可重復利用的軟件,就功能而言,IP核可以定義為SoC的基本電路功能塊又稱為內(nèi)核,可由用戶或?qū)S肐C公司或獨立的公司開發(fā)而成,IP核的顯著特點是具有重用性。鑒于SoC系統(tǒng)設計者很難獨自開發(fā)、維護和移植所有必須的IP核,所以在Soc設計中必然要用到第3方的IP核,當IP核被轉(zhuǎn)移到用戶設計與制造工藝中時,IP核被重復利用了,具有自主知識產(chǎn)權(quán)的IP核的復用是Soc設計中解決設計層次、產(chǎn)品成本、設計周期和降低風險的關鍵環(huán)節(jié)是SoC設計中的關鍵技術。IP核重復利用可以提高設計能力,節(jié)省設計人員可以縮短上市時間,更好的利用現(xiàn)有的工藝技術,降低成本。基于此筆者設計了基于SoC的音頻接口IP模塊。

1 APB與IIS總線

APB(Advanced Peripheral Bus)是AMBA(Advanced Microcontrollel Bus Architectrure)組成部分,是用于低功耗和減少接口復雜度而設計的。APB用于帶寬,低速,低性能要求,無管線操作的外圍設備。APB總線操作包括Setup和Enable兩個狀態(tài)。其中APB讀操作只需在Enable狀態(tài)數(shù)據(jù)有效,寫操作要求寫數(shù)據(jù)在整個寫操作期間保持有效。

APB協(xié)議規(guī)定每個傳輸只與時鐘上升沿相關。這就使APB外圍設備很容易被集成在設計之中,特點如下:

(1)在高頻操作的性能改進;

(2)獨立的脈沖時鐘;

(3)靜態(tài)時鐘分析比較簡單,因為用單時鐘沿觸發(fā);

(4)自測試邏輯插入沒有特別的條件需要考慮;

(5)在ASIC庫中有性能很好的上升沿寄存器;

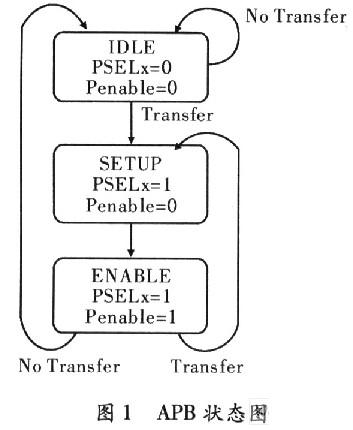

APB狀態(tài)機,如圖1所示。

APB這3個狀態(tài)描述如下:

IDLE:默認初始狀態(tài)。

Setup:當有一個傳輸請求,總線將進入Setup狀態(tài),當PSELx,信號被選擇。總線只在Setup狀態(tài)停留一個周期,并將在時鐘的上升沿進入Enable狀態(tài)。

Enable:在Enable狀態(tài)中,PEnable有效,地址信號,讀寫信號,選擇信號將保持穩(wěn)定,當狀態(tài)從Setup到Enable狀態(tài)。Enable狀態(tài)僅僅維持一個時鐘,如果沒有傳輸發(fā)生,系統(tǒng)將回到IDLE,如果有傳輸發(fā)生,系統(tǒng)狀態(tài)將進入Setup狀態(tài)。當從Enable狀態(tài)到Setup狀態(tài)時允許有短脈沖干擾。

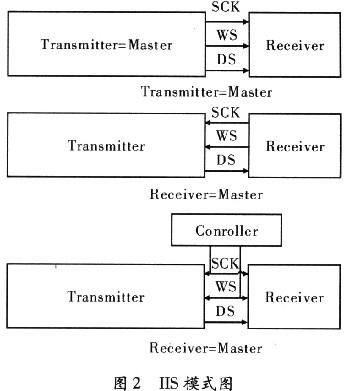

IIS總線:在飛利浦公司的IIS標準中,既規(guī)定了硬件接口規(guī)范,也規(guī)定了數(shù)字音頻數(shù)據(jù)的格式。IIS總線擁有3條數(shù)據(jù)線進行數(shù)據(jù)傳輸:數(shù)據(jù)傳輸線(DS),選擇線(WS),時鐘線(SCK)。在數(shù)據(jù)傳輸過程中,發(fā)送端(Transmitter)和接收端(Receiver)具有相同的時鐘信號,發(fā)送端作為主導裝置(Master)時,產(chǎn)生位時鐘信號、命令(聲道)選擇信號和數(shù)據(jù)。在綜合的系統(tǒng)中,可能具有幾個發(fā)送端和接收端,使識別發(fā)送端比較困難。在這樣的系統(tǒng)中,可以設置一個控制器(Controller)來作為系統(tǒng)的主導裝置來識別多路的數(shù)字音頻信號的數(shù)據(jù)流,此時發(fā)送端成為在外部時鐘控制下的從屬裝置(Stave),系統(tǒng)的主導裝置也可以與發(fā)送端或接收端相結(jié)合,這需要通過對硬件或軟件的設置來激活。它擁有3種模式,如圖2所示。

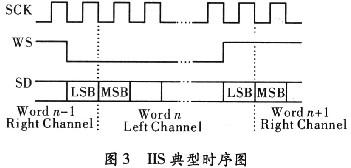

IIS有時序信號圖,如下所述。串行時鐘信號(SCK):即對應數(shù)字音頻的每一位數(shù)據(jù),SCK對應1個脈沖。SCK的頻率=2×采樣頻率×采樣位數(shù)。

聲道選擇信號(WS):用于切換左右聲道的數(shù)據(jù)。WS的頻率等于采樣頻率。

串行數(shù)據(jù)信號(SD):就是用二進制補碼表示的音頻數(shù)據(jù)。

典型時序,如圖3所示。

IIS格式的信號無論有多少位有效數(shù)據(jù),數(shù)據(jù)的最高位總是被最先傳輸,在WS變化,也就是一幀開始后的第2個SCK脈沖處,因此最高位擁有固定的位置,而最低位的位置則是依賴于數(shù)據(jù)的有效位數(shù)。也就使得接收端與發(fā)送端的有效位數(shù)可以不同。如果接收端能處理的有效位數(shù)少于發(fā)送端,可以放棄數(shù)據(jù)幀中多余的低位數(shù)據(jù),如果接收端能處理的有效位數(shù)多于發(fā)送端,可以自行補足剩余的位(常補足為零)。這種同步機制使得數(shù)字音頻設備的互連更加方便,而且不會造成數(shù)據(jù)錯位。為了保證數(shù)字音頻信號的正確傳輸,發(fā)送端和接收端應該采用相同的數(shù)據(jù)格式和長度。對IIS格式來說數(shù)據(jù)長度可以不同。

2 音頻IP模塊設計

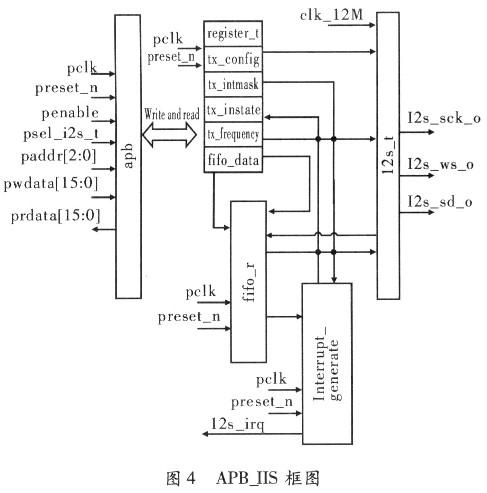

音頻IP模塊,完成APB總線協(xié)議到IIS協(xié)議的轉(zhuǎn)換,實現(xiàn)音頻的輸出,并根據(jù)任務要求,設置各種寄存器和中斷輸出。音頻輸出模塊(APB_IIS)示意框圖,如圖4所示。

APB_IIS模塊由以下5個模塊組成:APB接口模塊,APB接口模塊主要是遵守AMBA協(xié)議,完成讀寫數(shù)據(jù)的譯碼。符合APB協(xié)議完成寄存器讀寫,實現(xiàn)寄存器register_t的配置,狀態(tài)讀寫。

寄存器模塊(register_t),完成各種功能寄存器的設置。register_t模塊,包含配置寄存器模塊(tx_config),屏蔽寄存器(tx_intmask),狀態(tài)寄存器(tx_instate),頻率配置寄存器模塊(tx_frequency),F(xiàn)IFO寫數(shù)據(jù)地址(fifo_data)。

FIFO模塊(fifo_t),的功能是從一個高速時鐘域到低速時鐘域數(shù)據(jù)的緩沖,并產(chǎn)生標志信號,用于中斷產(chǎn)生。

IIS接口模塊(i2s_t),i2s_t模塊遵守IIS協(xié)議,并完成數(shù)據(jù)的輸出。

本模塊符合以下功能要求:

(1)傳輸音頻(Transmitter)模塊;

(2)主模式,由時鐘由外部提供(12 M);

(3)支持時序兩種模式音頻輸出;

(4)分頻器實現(xiàn)8/11/12/16/22.059/24./32/44.11/48(kHz)頻率數(shù)據(jù)傳輸;

(5)內(nèi)部記數(shù)器完成16音頻數(shù)據(jù)的記數(shù);

(6)數(shù)據(jù)的并串轉(zhuǎn)換。

中斷模塊(interrupt_generate),中斷信號是通過FIFO模塊的標志信號和屏蔽寄存器(tx_intmask)信號產(chǎn)生中斷信號給系統(tǒng)的中斷控制器。

3 仿真結(jié)果

圖5為APB接口邏輯讀寫時序和IIS輸出時序的局部波形仿真。時序仿真證明符合規(guī)范和功能要求。

4 結(jié)束語

文中根據(jù)協(xié)議和實際需求設計一個APB轉(zhuǎn)IIS的模塊,具體描述了協(xié)議,功能規(guī)范,完成RTL代碼描述和功能驗證,得出正確可移植的音頻IP模塊。由于模塊是有各個分立的模塊單元組成,所以再根據(jù)實際需求修改模塊是非常容易的。