說明:

DOPB 器件內(nèi)部的外圍設(shè)備數(shù)據(jù)接口總線,用于處理器與片內(nèi)的設(shè)備進(jìn)行數(shù)據(jù)交換。

DLMB 實(shí)現(xiàn)數(shù)據(jù)交換的本地塊存儲(chǔ)器總線,該總線為處理器內(nèi)核與塊存儲(chǔ)器(BRAM) 之間提供專用的高速數(shù)據(jù)交換通道。

IOPB 用于實(shí)現(xiàn)外部程序存儲(chǔ)器的總線接口。當(dāng)程序較大時(shí),需要外接大容量的存儲(chǔ)器,該總線提供讀取指令的通道。

ILMB 用于取指令的本地存儲(chǔ)器總線,該總線與器件內(nèi)部的塊存儲(chǔ)器(BRAM) 相連,實(shí)現(xiàn)高速的指令讀取。

MFSL0. . 7 主設(shè)備數(shù)據(jù)接口, 提供點(diǎn)對(duì)點(diǎn)的通信通道。

SFSL0. . 7 從設(shè)備數(shù)據(jù)接口, 提供點(diǎn)對(duì)點(diǎn)的通信通道。

2 EDK開發(fā)流程

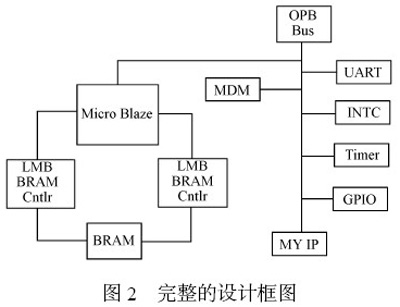

EDK( Embedded Development Kit) 是Xilinx 公司針對(duì)FPGA 內(nèi)部32 位嵌入式處理器開發(fā)而推出的開發(fā)套件。EDK的工具包中集成了硬件平臺(tái)產(chǎn)生器、軟件平臺(tái)產(chǎn)生器、仿真模型生成器、軟件編譯器和軟件調(diào)試等工具,利用其集成開發(fā)環(huán)境XPS( Xilinx Platform Studio) 可以方便、快速地完成嵌入式系統(tǒng)開發(fā)的整個(gè)流程。EDK 以IP core的形式,提供諸如LMB ,OPB 總線接口、外部存儲(chǔ)控制器、SDRAM 控制器、UART 中斷控制器、定時(shí)器及其他一些外圍設(shè)備接口等資源,利用這些資源,設(shè)計(jì)者能夠輕松構(gòu)建一個(gè)完善的嵌入式處理器系統(tǒng),其完整的設(shè)計(jì)框圖如圖2所示。

一個(gè)完整的嵌入式處理器系統(tǒng)設(shè)計(jì)通常包括3 個(gè)部分: 硬件系統(tǒng)的構(gòu)建;存儲(chǔ)器映射及軟件的開發(fā);應(yīng)用程序開發(fā)。

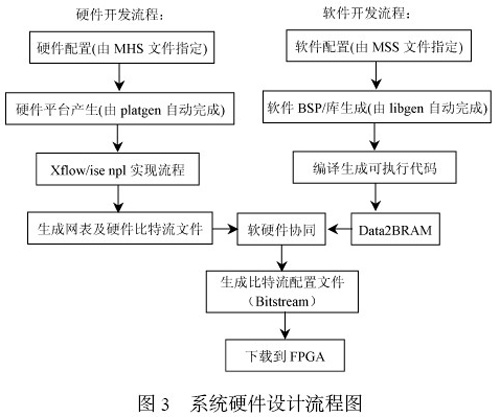

在XPS 集成開發(fā)環(huán)境下,嵌入式處理器硬件系統(tǒng)的構(gòu)建由微處理器硬件規(guī)范(MHS) 文件和微處理器外圍設(shè)備描述(MPD) 文件定義; 軟件系統(tǒng)結(jié)構(gòu)由微處理器軟件規(guī)范(MSS) 文件定義,其開發(fā)流程如圖3 所示。

MHS 文件用于描述硬件系統(tǒng)結(jié)構(gòu),定義處理器類型、總線接口、外設(shè)接口、中斷處理和地址空間。該文件可用任意文本編輯器創(chuàng)建,是文本化的原理圖輸入。MPD 文件包含外圍設(shè)備的所有有效輸入/ 輸出接口和硬件參數(shù)。MSS 文件主要用來定義軟件庫、驅(qū)動(dòng)程序和文件系統(tǒng)。

說明:Data2BRAM 的作用是把軟件代碼文件( 3 .elf) 、FPGA 位流文件( 3 . bit) 和塊存儲(chǔ)器(BRAM) 初始化數(shù)據(jù)文件( 3 . bmm) 轉(zhuǎn)換成新的FPGA 位流文件( 3 . bit )和存儲(chǔ)器數(shù)據(jù)文件( 3 . mem) 。關(guān)于應(yīng)用程序的編寫將在下面的實(shí)例中詳細(xì)介紹。

3 一個(gè)簡單的實(shí)例

本實(shí)例基于e 元素科技的數(shù)字刀劍系列之火龍刀3評(píng)估板,簡要敘述一個(gè)嵌入式處理器系統(tǒng)的開發(fā)流程,著重講述應(yīng)用程序的編寫。對(duì)于其他評(píng)估板,只需對(duì)用戶約束文件( 3 . ucf) 稍做修改即可。為簡單起見,與圖2 所示一個(gè)完整的系統(tǒng)相比,本例所述系統(tǒng)只在OPB 總線上掛MDM(硬件調(diào)試模塊) 和GPIO(通用輸入/ 輸出設(shè)備) 2 個(gè)外圍設(shè)備,GPIO 對(duì)應(yīng)評(píng)估板上8 個(gè)L ED 輸出,當(dāng)完成下載到FPGA 后,8 個(gè)L ED 將不停地閃爍。具體描述如下:

第一步,硬件系統(tǒng)構(gòu)建,在XPS 集成開發(fā)環(huán)境下,利用BSP(Base System Builder ) 向?qū)ё詣?dòng)創(chuàng)建一個(gè)以Mi-croBlaze 處理器為核心的簡單硬件系統(tǒng),設(shè)置處理器時(shí)鐘頻率為50 MHz ,總線時(shí)鐘頻率為50 MHz ,設(shè)置片上讀/寫調(diào)試模塊為調(diào)試接口,在處理器IP 中,只加入MDM 和GPIO。根據(jù)向?qū)е鸩讲僮?即可完成硬件系統(tǒng)的構(gòu)建。

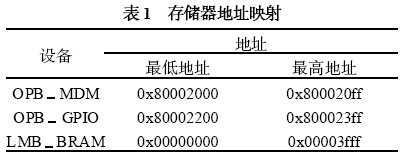

第二步,在硬件系統(tǒng)建立后,利用XPS 的集成工具,完成網(wǎng)表的生成和軟件的配置,存儲(chǔ)器地址映射(默認(rèn)由系統(tǒng)自動(dòng)生成,分配的地址隨系統(tǒng)而異) 如表1 所示。驅(qū)動(dòng)配置和存儲(chǔ)器映射的標(biāo)識(shí)符及地址分配包含在文件xparameter s. h 中, 以上兩步具體操作實(shí)現(xiàn)細(xì)節(jié)可參考EDK相關(guān)文檔。

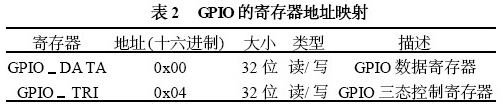

第三步,應(yīng)用程序的開發(fā)。應(yīng)用程序的編寫使用C 語言,其方法有2 種,第一種是可以采用EDK 提供的應(yīng)用程序接口函數(shù)(API) ,接口函數(shù)既多又復(fù)雜,不易搞懂;第二種方法是采用訪問硬件的通用方式即簡單的對(duì)地址賦值的方式。本例選用后者,要采用地址賦值方式,首先要了解GPIO 的寄存器地址映射,參見表2 。

相關(guān)代碼及描述如下:

首先設(shè)定一個(gè)指針變量,將系統(tǒng)分配給GPIO 的地址賦給指針變量, 即讓指針指向GPIO 的基地址, 也就是GPIO 的數(shù)據(jù)寄存器( GPIO DATA) ,接著向GPIO 三態(tài)控制寄存器寫零(其地址為基地址加上偏移量4 ,即讓指針變量加4) ,將GPIO 設(shè)置為輸出,接下來就可以往GPIO數(shù)據(jù)寄存器送數(shù),以控制8 個(gè)L ED 的狀態(tài)。

# include " xbasic_types. h"

# include " xparameters. h"

# include " xutil. h"

# include " xgpio_l. h"

# define L ED DELA Y 2000000

void main ()

{

Xuint32 Data = 0xaa ;

int Delay ;

int count = 0 ;

Xuint32 3 ledpt r ;

ledpt r = (int 3 ) 0x80002200 ; / / 指針指向GPIO

*(ledpt r + 4) = 0x00000000 ;

/ / 向GPIO_TRI 寄存器寫零,將GPIO 初始化為輸出

while (1)

{ count + + ;

if (count %2 = = 0)

{

*ledpt r = 0x55 ;

/ / 向GPIO_DATA 寄存器送數(shù),驅(qū)動(dòng)L ED

}

else

{

* ledpt r = 0xaa ;

/ / 向GPIO_DATA 寄存器送數(shù),驅(qū)動(dòng)L ED

}

for (Delay = 0 ; Delay < L ED_DELA Y; Delay + + ) ;

/ / 延時(shí)以看清L ED 在閃爍

if (count %2 = = 0)

{

* ledpt r = 0x0f ;

/ / 向GPIO_DATA 寄存器送數(shù),驅(qū)動(dòng)L ED

}

else

{

* ledpt r = 0xf0 ;

/ / 向GPIO_DATA 寄存器送數(shù),驅(qū)動(dòng)L ED

}

for (Delay = 0 ; Delay < L ED_DELA Y; Delay + + ) ;

/ / 延時(shí)以看清L ED 在閃爍

}

}