近年來,嵌入式技術(shù)發(fā)展迅速,嵌入式應(yīng)用已經(jīng)深入到金融、航空航天、電信、網(wǎng)絡(luò)、工業(yè)控制、信息家電等各個(gè)領(lǐng)域。嵌入式系統(tǒng)已經(jīng)無所不在,與人們的日常生活息息相關(guān)。嵌入式系統(tǒng)以微處理器為核心,以計(jì)算機(jī)技術(shù)為基礎(chǔ),其主要特征是實(shí)時(shí)性強(qiáng)。針對(duì)嵌入式處理器的應(yīng)用,Xilinx公司推出了IBM PowerPC 405和Microblaze兩種32位的嵌入式處理器內(nèi)核,IBMPowerPC 405是嵌入在現(xiàn)場(chǎng)可編程門陣列(filedprogrammable gate array,F(xiàn)PGA)中的硬核處理器,而MicroBlaze是采用哈佛(Harvard)總線結(jié)構(gòu)的軟核處理器,可在可編程器件中進(jìn)行配置,具有更好的靈活性,適合復(fù)雜嵌入式系統(tǒng)的開發(fā)。

1 MicroBlaze23軟內(nèi)核內(nèi)部結(jié)構(gòu)

MicroBlaze軟內(nèi)核是一種針對(duì)Xilinx FPGA器件而優(yōu)化的功能強(qiáng)火的32位微處理器,適用于所有現(xiàn)產(chǎn)的FPGA器件。MicroBlaze軟內(nèi)核和其它外設(shè)IP核一起,可以完成可編程系統(tǒng)芯片(SOPC)的設(shè)計(jì)。MicroBlaze軟內(nèi)核采用RISC(reduced instruction system computer)架構(gòu)和哈佛(Harvard)結(jié)構(gòu)的32位指令和數(shù)據(jù)總線,內(nèi)部有32個(gè)通用寄存器R0~R31和2個(gè)特殊寄存器程序指針(PC)和處理器狀態(tài)寄存器(MSR)。MicroBlaze還具有指令和數(shù)據(jù)緩存,所有的指令長(zhǎng)度都是32位,有3個(gè)操作數(shù)和兩種尋址模式,指令功能劃分有邏輯運(yùn)算,算術(shù)運(yùn)算,分支,存儲(chǔ)器讀/寫和特殊指令等,指令執(zhí)行的流水線是并行流水線,它分為3級(jí)流水線:取指,譯碼和執(zhí)行。MicroBlaze軟內(nèi)核結(jié)構(gòu)如圖1所示。

Microblaze軟內(nèi)核,片上本地存儲(chǔ)器,標(biāo)準(zhǔn)總線互連以及基于片上外設(shè)總線(OPB)的外圍設(shè)備構(gòu)成了MicroBlaze嵌入式系統(tǒng)。

2 MicroBlaze嵌入式系統(tǒng)開發(fā)流程

在用Xilinx公司生產(chǎn)的FPGA進(jìn)行嵌入式設(shè)計(jì)時(shí),Xilinx公司提供嵌入式開發(fā)工具EDK,它由XPS(xilinxplatformstudio),SDK(software development kit),creat—import peripheral和XMD(xilinx microprocessordebugger)組成。

其中XPS是主設(shè)計(jì)程序平臺(tái),可以實(shí)現(xiàn)嵌入式開發(fā)的所有步驟環(huán)節(jié),其它的軟件工具可以在XPS里面直接調(diào)用。SDK是軟件開發(fā)工具,支持C和C++,主要完成軟件的設(shè)計(jì)。creat—import peripheral工具實(shí)現(xiàn)用戶IP核和CPU的接口設(shè)計(jì)。XMD主要完成軟件調(diào)試。

進(jìn)行硬件設(shè)計(jì)時(shí),EDK以IP cote的形式,提供諸如LMB、OPB總線接口、外部存儲(chǔ)控制器、SDRAM控制器、UART中斷控制器、定時(shí)器及其他一些外圍設(shè)備接口等資源,利用這些資源,用戶能夠輕松構(gòu)建一個(gè)完善的嵌入式處理器系統(tǒng)。進(jìn)行相應(yīng)的軟件設(shè)計(jì)時(shí),EDK提供了外設(shè)IP驅(qū)動(dòng)程序和大量的函數(shù)庫,板級(jí)支持包(BSP:board support package)以及完整的操作系統(tǒng)以幫助用戶開發(fā)軟件平臺(tái)。

當(dāng)用戶需要定制自己的外設(shè)以完成一些特殊功能時(shí),用戶可以Xilinx公司提供的Project Navigator ISE環(huán)境下,用VerilogHDL或者VHDL代碼完成用戶IP core的設(shè)計(jì),利用XPS中提供的creat—import peripheral工具完成創(chuàng)建和導(dǎo)入用戶IP core。利用EDK現(xiàn)有的IP core和用戶自定義IP core可以建立一個(gè)完善的嵌入式系統(tǒng)。在XPS開發(fā)環(huán)境下,完整的開發(fā)流程如圖2所示。

MHS和MSS文件都是由用戶根據(jù)整個(gè)系統(tǒng)的要求通過EDK生成的。其中MHS文件包含了對(duì)整個(gè)MicroBlaze系統(tǒng)組織的描述(包括處理器、總線、外設(shè)等),用戶也可以根據(jù)自己的實(shí)際情況修改MHS文件(例如opb_gpio的輸出寬度),完善系統(tǒng)設(shè)計(jì)。硬件平臺(tái)生成器(PlatGen)產(chǎn)生整個(gè)系統(tǒng)的網(wǎng)表,結(jié)合約束文件可最終生成可配置文件(.bit)用以下載。MSS文件包含了所有外設(shè)的驅(qū)動(dòng)等信息的描述,庫生成器(LibGen)通過它產(chǎn)生所需的驅(qū)動(dòng),用戶根據(jù)這些驅(qū)動(dòng)文件完成軟件調(diào)度程序,再由MB2GCC工具對(duì)調(diào)度程序進(jìn)行編譯生成可執(zhí)行程序。最后.bit文件和軟件程序合成下載到開發(fā)板。若程序執(zhí)行不理想,可以用 XMD進(jìn)行軟件調(diào)試,找出問題所在,解決問題完成設(shè)計(jì)。

3 AD數(shù)據(jù)采樣與實(shí)現(xiàn)

本設(shè)計(jì)給出了AD數(shù)據(jù)接收、采樣、存儲(chǔ)。天線接收到的信號(hào),經(jīng)過信號(hào)斛析,得到了時(shí)間信息,產(chǎn)生數(shù)字信號(hào),經(jīng)過30.69MHz 中頻調(diào)制,送入ad_transmit完戰(zhàn)AD采樣,存儲(chǔ)到嵌入在開發(fā)板上的blockram里面,可以通過FPGA調(diào)試工具chipscope來觀察AD采樣數(shù)據(jù)。

本設(shè)計(jì)采用的足e元素科技的Virtex4系列開發(fā)板,該開發(fā)板上有嵌入的兩個(gè)AD數(shù)據(jù)接口(ADC0,adc1),在本設(shè)計(jì)采用的是adc0。AD采樣是用Verilog代碼設(shè)計(jì)完成的,在ISE環(huán)境下仿真驗(yàn)證成功,掛載到OPB總線上。其硬件平臺(tái)如圖3所示。

構(gòu)建實(shí)驗(yàn)的系統(tǒng)資源為:

Microblaze:系統(tǒng)的核心模塊;

LMB總線:(1)ILMB BRAM Cntrl,DLMBBRAM Cntrl內(nèi)部BRAM控制接口IP,使得MicroBlaze可以通過LMB總線訪問BRAM;(2)BRAM-BLOCK(片內(nèi)存儲(chǔ)模塊),可作為系統(tǒng)的程序存儲(chǔ)空間或高速緩存;

OPB總線:(1)通信接口IP,通過OPB-UARTLITE(串行通信接口),驅(qū)動(dòng)uart接口轉(zhuǎn)換器完成與外部系統(tǒng)如 PC的數(shù)據(jù)通信;(2)用戶接口IP,通過OPB總線訪問 MicroBlaze。

天線等外圍設(shè)備:天線、信號(hào)解析、信號(hào)產(chǎn)生器和中頻調(diào)制完成根據(jù)解析出的時(shí)間信息產(chǎn)生數(shù)字信號(hào),調(diào)制為中頻模擬信號(hào),中頻調(diào)制頻率為30.69MHz。

Uart端口:通過超級(jí)端口觀察軟件凋度程序的執(zhí)行過程。

Chipscope核:ila核及icon核用來觀察數(shù)據(jù),icon核控制ila核,ila核連接所需要觀察的信號(hào)的端口。

Dcm時(shí)鐘控制:控制AD采樣速率,本設(shè)計(jì)采樣頻率為81.84MHz。

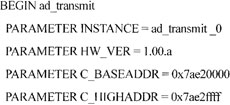

設(shè)計(jì)中的硬件描述文件(MHS)即為按照上面定制的硬件平臺(tái)框圖中給出的系統(tǒng)資源編寫的,其部分內(nèi)容如下:

給出的MHS文件中,列出了用戶IP ad_transmit 地址,時(shí)鐘還有端口連接情況,其中ad_transmit_0_ad_din設(shè)置為外部端口,連接到開發(fā)板上FPGA相應(yīng)的adc0端口。chipscope_ila則列出了通過chipscope觀察的信號(hào)。

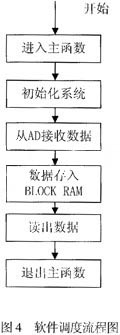

軟件描述文什(MSS)列出了所有外設(shè)的驅(qū)動(dòng)信息,函數(shù)庫產(chǎn)生器利用這些配置信息,配置相應(yīng)的驅(qū)動(dòng)程序函數(shù)庫。用戶根據(jù)這些驅(qū)動(dòng)程序來完成軟件調(diào)度程序,完成軟件設(shè)計(jì)。本設(shè)計(jì)主要通過硬件來實(shí)現(xiàn),軟件調(diào)度程序比較簡(jiǎn)單,流程圖如4所示。

完成軟件調(diào)度程序以后,就可以對(duì)源程序進(jìn)行編澤、匯編和鏈接,生成可執(zhí)行義件,通過在XPS中利用工具“data2bram”,將軟件設(shè)計(jì)中生成的程序代碼作為存儲(chǔ)區(qū)的初始化數(shù)據(jù),合并到硬件設(shè)計(jì)中生成的下載配置文件中,最終生成包含軟、硬件設(shè)計(jì)的FPGA下載配置文件“download.Bit”,就可以將其下載到芯片中驗(yàn)證本設(shè)計(jì)。

通過FPGA調(diào)試工具chipscope來觀察接收的AD采樣數(shù)據(jù),本設(shè)計(jì)中設(shè)定了AD數(shù)據(jù)溢出控制,即AD采樣數(shù)據(jù)在-8192~+8192之間,AD采樣數(shù)據(jù)如圖5,圖6所示,實(shí)現(xiàn)AD數(shù)據(jù)采樣。

本設(shè)計(jì)將用戶IP ad_transimit掛載到OPB總線上,采用chipscope對(duì)AD采樣數(shù)據(jù)進(jìn)行觀察,通過觀察與分析,可以得出本設(shè)計(jì)很好的完成了AD數(shù)據(jù)接收,采樣,存儲(chǔ),是一個(gè)完整的AD數(shù)據(jù)采集系統(tǒng)。進(jìn)一步可以對(duì)存儲(chǔ)的AD采樣數(shù)據(jù)進(jìn)行更為復(fù)雜的數(shù)據(jù)處理過程。