目前,已經(jīng)可以在1.2V 65nm CMOS技術(shù)的基礎(chǔ)上實(shí)現(xiàn)8Vpp和脈沖寬度調(diào)制射頻高壓/大功率驅(qū)動(dòng)器。在0.9到3.6GHz的工作頻率范圍內(nèi),該芯片在9V的工作電壓下可向50Ω負(fù)載提供8.04Vpp的最大輸出擺幅。這使得CMOS驅(qū)動(dòng)器能夠直接連接并驅(qū)動(dòng)LDMOS和GaN等功率晶體管。該驅(qū)動(dòng)器的最大導(dǎo)通電阻為4.6Ω。2.4GHz時(shí)所測(cè)量的占空比控制范圍為30.7%到71.5%.通過使用新型薄氧化層漏極延伸MOS器件,該驅(qū)動(dòng)器可實(shí)現(xiàn)可靠的高壓操作,而這一新型器件通過CMOS技術(shù)實(shí)現(xiàn)時(shí)無需額外的費(fèi)用。

技術(shù)背景

現(xiàn)代無線手持通信無線電(包括射頻(RF)功率放大器(PA)在內(nèi))均是在深亞微米CMOS中得以實(shí)現(xiàn)。不過,在無線基礎(chǔ)設(shè)施系統(tǒng)中,由于需要較大的輸出功率等級(jí),必須通過硅LDMOS或混合技術(shù)(如GaA和更先進(jìn)的GaN)才能實(shí)現(xiàn)RF PA.對(duì)下一代可重新配置的基礎(chǔ)設(shè)施系統(tǒng)而言,開關(guān)模式PA(SMPA)似乎能為多頻帶多模式發(fā)射器提供所需的靈活性和高性能。但是,為了將基站SMPA中使用的高功率晶體管與發(fā)射器的所有數(shù)字CMOS模塊相連,需要能夠生成高壓(HV)擺幅的寬帶RF CMOS驅(qū)動(dòng)器。這樣不僅能實(shí)現(xiàn)更優(yōu)的高功率晶體管性能,而且還能將數(shù)字信號(hào)處理直接用于控制所需的SMPA輸入脈沖波形,從而提高系統(tǒng)整體性能。

設(shè)計(jì)挑戰(zhàn)

LDMOS或GaN SMPA的輸入電容通常為幾個(gè)皮法,必須由振幅高于5Vpp的脈沖信號(hào)驅(qū)動(dòng)。因此,SMPA CMOS驅(qū)動(dòng)器必須同時(shí)提供高壓和瓦特級(jí)的射頻功率。遺憾的是,深亞微米CMOS給高壓和大功率放大器及驅(qū)動(dòng)器的實(shí)現(xiàn)提出了諸多挑戰(zhàn),尤其是極低的最大工作電壓(即可靠性問題引起的低擊穿電壓)和損耗較大的無源器件(例如用于阻抗變換)。

現(xiàn)有解決方案

用于實(shí)現(xiàn)高壓電路的方法并不多。可以采用能夠?qū)崿F(xiàn)高壓容限晶體管的技術(shù)解決方案(如多柵氧化層),但代價(jià)是生產(chǎn)流程較昂貴,必須向基線CMOS工藝添加額外的掩模和處理步驟,因此這種方案并不理想。此外,為可靠地增加高壓耐受力,可以采用僅使用標(biāo)準(zhǔn)基線晶體管(使用薄/厚氧化層器件)的電路方案。在第二種方法中,器件堆疊或串聯(lián)陰極是最常見的例子。但是,射頻復(fù)雜性和性能具有很大的局限性,尤其是當(dāng)串聯(lián)陰極(或堆疊)器件的數(shù)量增加至2個(gè)或3個(gè)以上時(shí)。另一種實(shí)現(xiàn)高壓電路的途徑就是如本文所述的在基線CMOS技術(shù)中使用漏極延伸場(chǎng)效應(yīng)管(EDMOS)來實(shí)現(xiàn)。

新的解決方案

漏極延伸器件基于智能布線技術(shù),這得益于在ACTIVE(硅)、STI(氧化層)及GATE (多晶硅)區(qū)域中可實(shí)現(xiàn)十分精細(xì)的尺寸,并能在沒有附加費(fèi)用的條件下,利用基線深亞微米CMOS技術(shù)實(shí)現(xiàn)PMOS和NMOS兩種高壓容限晶體管。盡管與采用該工藝的標(biāo)準(zhǔn)晶體管相比,這些EDMOS設(shè)備的RF性能實(shí)際上較低,但由于消除了與其他HV等效電路相關(guān)的重要損耗機(jī)制(如串聯(lián)陰極),它們?nèi)阅茉谡麄€(gè)高壓電路中實(shí)現(xiàn)較高整體性能。

因此,本文所述的高壓CMOS驅(qū)動(dòng)器拓?fù)浣Y(jié)構(gòu)采用EDMOS器件來避免器件堆疊。RF CMOS驅(qū)動(dòng)器采用薄氧化層EDMOS器件通過65nm低待機(jī)功耗基線CMOS工藝制造,且無需額外的掩模步驟或工序。對(duì)PMOS和NMOS而言,這些器件上測(cè)量到的fT分別超過30GHz和50GHz,它們的擊穿電壓限度為12V.高速CMOS驅(qū)動(dòng)器前所未有地實(shí)現(xiàn)了高達(dá)3.6GHz的8Vpp輸出擺幅,因而能為像GaN這樣的基于寬帶隙的SMPA提供驅(qū)動(dòng)。

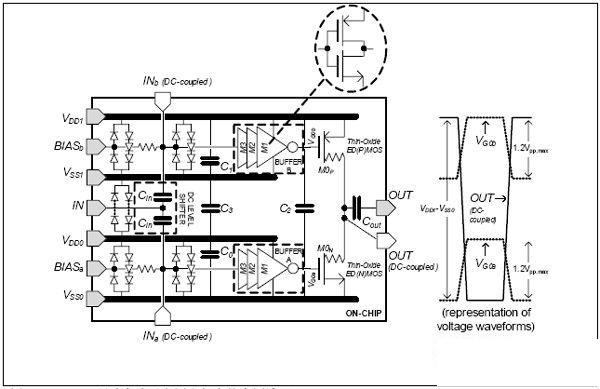

圖1為本文所述驅(qū)動(dòng)器的結(jié)構(gòu)示意圖。輸出級(jí)包括一個(gè)基于EDMOS的逆變器。EDMOS器件可由低壓高速標(biāo)準(zhǔn)晶體管直接驅(qū)動(dòng),從而簡化了輸出級(jí)與其它數(shù)字和模擬CMOS電路在單顆芯片上的集成。每個(gè)EDMOS晶體管均由通過3個(gè)CMOS逆變器級(jí)實(shí)現(xiàn)的錐形緩沖器(圖1中的緩沖器A和B)提供驅(qū)動(dòng)。兩個(gè)緩沖器具有不同的直流等級(jí),以確保每個(gè)CMOS逆變器都能在1.2V的電壓下(受技術(shù)所限,即VDD1-VSS1=VDD0-VSS0=1.2V)穩(wěn)定運(yùn)行。為了使用不同的電源電壓并允許相同的交流操作,兩個(gè)緩沖器的構(gòu)造完全相同,并內(nèi)置于單獨(dú)的Deep N-Well(DNW)層中。驅(qū)動(dòng)器的輸出擺幅由VDD1-VSS0決定,可隨意選擇不超過EDMOS器件最大擊穿電壓的任意值,而內(nèi)部驅(qū)動(dòng)器的運(yùn)行保持不變。直流電平位移電路可分離每個(gè)緩沖器的輸入信號(hào)。

圖1:RF CMOS驅(qū)動(dòng)電路示意圖和相應(yīng)的電壓波形

CMOS驅(qū)動(dòng)器的另一個(gè)功能就是對(duì)輸出方波的脈沖寬度控制,該功能由脈寬調(diào)制(PWM)通過可變柵偏壓技術(shù)實(shí)現(xiàn)。PWM控制有助于實(shí)現(xiàn)微調(diào)和調(diào)諧功能,從而提升高級(jí)SMPA器件的性能。緩沖器A和B的第一個(gè)逆變器(M3)的偏置電平可參照該逆變器本身的開關(guān)閾值對(duì)RF正弦輸入信號(hào)進(jìn)行上移/下移。偏置電壓的改變將使逆變器M3的輸出脈沖寬度發(fā)生變化。然后,PWM信號(hào)將通過另外兩個(gè)逆變器M2和M1進(jìn)行傳輸,并在RF驅(qū)動(dòng)器的輸出級(jí)(EDMOS)合并。

為確保輸出級(jí)之前的兩個(gè)RF路徑的布局對(duì)稱,所有逆變器(從M0到M3)都采用了統(tǒng)一的PMOS-to-NMOS晶體管尺寸比。所有CMOS級(jí)中每個(gè)加寬晶體管(M0級(jí)的總寬度可達(dá)4,032μm)的布局被分割成若干個(gè)單位晶體管布局參數(shù)化單元(P-cell),并通過優(yōu)化實(shí)現(xiàn)最高頻率。每個(gè)P-cell都包含一個(gè)版圖不對(duì)稱的多指晶體管(具有最小柵長)、護(hù)圈和所有與頂層內(nèi)部金屬的互連。每個(gè)晶體管的布局均可充分?jǐn)U展。

此外,該驅(qū)動(dòng)器還包含大尺寸的片上交流耦合和交流退耦平行板交指型金屬邊電容器。電容器Cin與兩個(gè)DC輸入偏壓線路(BIASa,b)一起實(shí)現(xiàn)直流電平位移。使用片上電容器Cout可實(shí)現(xiàn)DC耦合或AC耦合兩種方式的輸出。AC耦合可驅(qū)動(dòng)需要負(fù)柵偏壓的功率晶體管(如GaN)。將四條寬粗的電源線(VSS0,1和VDD0,1)布線于位于兩塊更厚的金屬頂部上的芯片內(nèi)。采用電容器C0、C1、C2和C3對(duì)內(nèi)部電源線進(jìn)行退耦。此外還增加了專用的ESD保護(hù)電路以保護(hù)CMOS芯片。

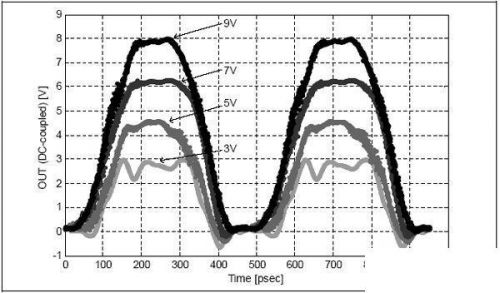

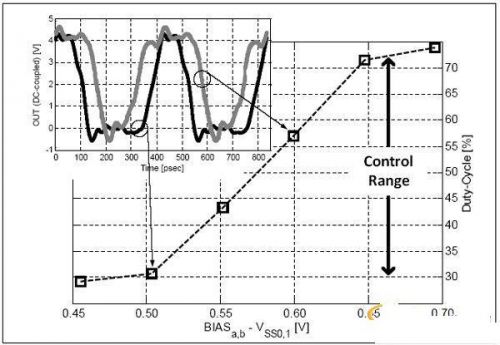

CMOS驅(qū)動(dòng)器的總體芯片面積為1.99mm2,而工作面積(EDMOS和緩沖器)僅為0.16mm2.將原型裸片安裝于PCB上以便于測(cè)試,并在50Ω的負(fù)載環(huán)境下進(jìn)行測(cè)量。使用高速數(shù)字采樣示波器可捕捉時(shí)域信號(hào)。圖2顯示了在3V、5V、7V和9V的供電電壓下,且輸入正弦波為2.1GHz時(shí),驅(qū)動(dòng)器DC耦合輸出的時(shí)域波形。在50Ω負(fù)載和9V電源下所測(cè)量的最大擺幅為8.04Vpp.測(cè)量到的驅(qū)動(dòng)器導(dǎo)通電阻低至4.6Ω。圖3顯示了測(cè)量到的脈沖寬度(以占空比表示)控制范圍,以DC偏置電平(即BIASa,b-VSS0,1)的函數(shù)表示。該圖還顯示了不同占空比條件下的兩種時(shí)域波形。在2.4GHz頻率和5V電源下可觀察到占空比控制范圍為30.7%至71.5%.在高達(dá)3.6GHz的頻率下,RF驅(qū)動(dòng)器將其脈沖波形保持為8Vpp.在2.4GHz下進(jìn)行的另一項(xiàng)測(cè)量表明,在5V和9V電源下連續(xù)工作24小時(shí)后,性能并未發(fā)生下降。

圖2:2.1GHz時(shí),多種電壓下監(jiān)測(cè)到的時(shí)域波形(VDD1- VSS0= 3V, 5V, 7V, 9V)

圖3:2.4GHz時(shí)測(cè)量到的占空比

與之前最先進(jìn)的CMOS器件相比,上述驅(qū)動(dòng)器實(shí)現(xiàn)了更大的輸出電壓擺幅和更高的工作頻率。此外,該CMOS驅(qū)動(dòng)器具有與SiGe-BiCMOS等效電路相近的性能。相比之前所有HV驅(qū)動(dòng)器,本文介紹的芯片具有帶RF控制功能的附加脈沖以提升SMPA系統(tǒng)性能。

本文小結(jié)

本文主要描述了采用1.2V基線65nm CMOS技術(shù)實(shí)現(xiàn)8.04Vpp和3.6GHz工作頻率的首款寬帶PWM控制RF SMPA驅(qū)動(dòng)器。該CMOS驅(qū)動(dòng)器連接了數(shù)字CMOS電路與高功率晶體管,可充當(dāng)面向無線基礎(chǔ)設(shè)施系統(tǒng)的下一代可重新配置多頻多模發(fā)射器的主要構(gòu)建模塊。