0 引言

Altera公司開(kāi)發(fā)的Nios II是基于可編程片上系統(tǒng)SOPC(System on a Programmable Chip)技術(shù)的32 位嵌入式處理器軟核。Altera 公司開(kāi)發(fā)的Nios II軟核,可以直接放在FPGA中,它體現(xiàn)了把實(shí)現(xiàn)產(chǎn)品的全部單元電路集成到一個(gè)芯片之內(nèi)的片上系統(tǒng)SOPC的思想。作為一種具有競(jìng)爭(zhēng)力的技術(shù),在國(guó)外已經(jīng)有大量的產(chǎn)品使用了這種技術(shù),在國(guó)內(nèi)使用Nios II處理器進(jìn)行嵌入式系統(tǒng)設(shè)計(jì)的開(kāi)發(fā)者也越來(lái)越多,但是離大規(guī)模應(yīng)用還有距離,應(yīng)該得到更加廣泛的關(guān)注。本文在實(shí)際的項(xiàng)目中需要使用Nios II來(lái)開(kāi)發(fā)存儲(chǔ)系統(tǒng),對(duì)于利用Nios II來(lái)進(jìn)行嵌入式系統(tǒng)開(kāi)發(fā),還有許多工作需要去深入研究本文在進(jìn)行存儲(chǔ)系統(tǒng)項(xiàng)目開(kāi)發(fā)的過(guò)程中,完成了基于FPGA的系統(tǒng)硬件軟件設(shè)計(jì)。為了到達(dá)系統(tǒng)的設(shè)計(jì)目標(biāo),就需要對(duì)Nios II的SOPC技術(shù)進(jìn)行深入的研究。還需要進(jìn)行uClinux操作系統(tǒng)的移植,基于操作系統(tǒng)的SD卡數(shù)據(jù)讀寫,必然就要涉及到怎樣編寫驅(qū)動(dòng)程序。本文先簡(jiǎn)單介紹操作SD卡的基本的硬件電路,接著給出了SD卡讀寫操作和驅(qū)動(dòng)程序設(shè)計(jì)的基本過(guò)程。最后給出了全文的結(jié)論,本文給出的方法具有一定的普遍性,和實(shí)用性。

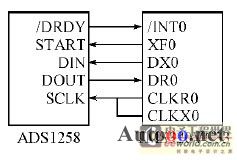

1系統(tǒng)硬件結(jié)構(gòu)設(shè)計(jì)

1.1 SD卡

SD卡(Secure Digitgal Memory Card)即“安全數(shù)碼存儲(chǔ)卡”是由日本松下公司、東芝公司、美國(guó)SANDISK 等公司在MMC卡的基礎(chǔ)上共同開(kāi)發(fā)研究而推出的,是一種容量大、高性能、安全性好、訪問(wèn)接口簡(jiǎn)單的存儲(chǔ)卡,得到了廣泛的使用。使用的范圍包括:MP3、數(shù)碼攝像機(jī)和照相機(jī)產(chǎn)品、智能手機(jī)等消費(fèi)類電子設(shè)備。當(dāng)前很多微處理器在內(nèi)部都集成了與SD卡通信的接口電路。

1.2 SD卡的特征

SD 卡的外形和接口觸點(diǎn)如圖1 所示。外形尺寸分為兩種,分別為:24 mm * 32 mm * 2.1 mm 或24 mm * 32mm *1.4mm.

軟核處理器的SD卡接口設(shè)計(jì)" src="http://files.chinaaet.com/images/2013/06/08/12290336283566.jpg" style="width: 469px; height: 140px; " />

圖1 SD 卡的形狀和接口

微處理器和SD卡之間的接口電路,要符合一定的約定,這個(gè)在SD卡的讀寫操作中,被稱為通信協(xié)議。為了適應(yīng)不同的通信協(xié)議,可以設(shè)置SD 卡使其工作在不同的通信模式之下。SD卡的通信模式分為兩種,一種是所謂的SD模式,另一種是SPI模式。現(xiàn)在SPI通信模式得到越來(lái)越多的使用。在處理器和SD卡的通信過(guò)程中,和SD卡通信的處理器(稱為主機(jī)),選擇一種通信方式,但在通信的整個(gè)過(guò)程中不能改變通信模式。SD卡分析復(fù)位命令,以確定下面的通信采用什么模式,在接下來(lái)的時(shí)間內(nèi),通信雙方要使用相同的通信模式。

當(dāng)工作在SD模式下時(shí),主機(jī)使用SD總線訪問(wèn)SD卡,使用多點(diǎn)總線拓樸結(jié)構(gòu)。這種結(jié)構(gòu)包括一個(gè)主機(jī)和多個(gè)從機(jī)(這里是指SD卡)。所有的SD卡共用一個(gè)時(shí)鐘信號(hào)CLK、電源和地,命令線和數(shù)據(jù)線則是屬于每一SD卡所專用的。前面說(shuō)到現(xiàn)在的微處理器都集成有硬件SPI接口,用于板內(nèi)的芯片之間的操作非常方便。當(dāng)設(shè)定工作在SPI模式下時(shí),主機(jī)使用自身所帶的SPI總線來(lái)訪問(wèn)SD卡。微處理器在第一個(gè)發(fā)給SD卡的復(fù)位命令中配置通信模式為SPI方式,當(dāng)然在操作SD卡的通信期間,通信模式是不能更改為SD模式的。

1.3 SD卡內(nèi)部構(gòu)造

圖2是SD卡的內(nèi)部結(jié)構(gòu)圖,主機(jī)通過(guò)SD卡的接口控制器來(lái)控制SD內(nèi)部的存儲(chǔ)單元中的數(shù)據(jù)。這樣設(shè)計(jì)的目的一方面是把SD卡內(nèi)部的存儲(chǔ)器和外部的操作隔離開(kāi)來(lái),利于保護(hù)內(nèi)部的數(shù)據(jù)。另一方面也有利于內(nèi)部存儲(chǔ)器采用更新的工藝,而不影響外部的訪問(wèn)接口。

在使用微處理器來(lái)讀寫SD卡內(nèi)的數(shù)據(jù)時(shí),要嚴(yán)格遵循通信協(xié)議。首先SD卡的數(shù)據(jù)傳輸?shù)幕締挝皇亲止?jié)。但是在SD卡的內(nèi)部是以塊為單位來(lái)組織數(shù)據(jù)的。對(duì)SD的數(shù)據(jù)讀取操作本質(zhì)上是以塊為單位的。一個(gè)塊的長(zhǎng)度一般是2的冪,比如256字節(jié)或者512字節(jié)。在具體的一次數(shù)據(jù)傳輸中塊的長(zhǎng)度(以字節(jié)為單位)可以在傳輸數(shù)據(jù)之前的命令控制字中設(shè)置。至于SD卡所允許的塊的最大長(zhǎng)度可以讀取SD卡的寄存器CSD來(lái)確定。在SD卡內(nèi)部有控制寄存器和狀態(tài)寄存器,其中的4個(gè)寄存器中存放著配置信息,比如RCA寄存器中存放本次通信過(guò)程中由主機(jī)分配的地址。

1.4訪問(wèn)SD卡的硬件電路

SD卡采用SPI總線方式與處理器連接,其電路原理如圖2所示。

圖2 SD 卡接口電路圖

1.5 NiosII的構(gòu)建過(guò)程

首先要考慮到的是使用什么樣的Nios II,Nios II分為幾個(gè)等級(jí),有標(biāo)準(zhǔn)內(nèi)核和高速內(nèi)核。由于本系統(tǒng)對(duì)速度的要求并不高,設(shè)計(jì)時(shí)采用了標(biāo)準(zhǔn)的Nios II內(nèi)核。在速度和所占用的資源方面具有比較好的折中。采用Altera公司的SOPC Builder工具來(lái)進(jìn)行構(gòu)建,生成一個(gè)Nios II的標(biāo)準(zhǔn)內(nèi)核。

接著要對(duì)選中的Nios標(biāo)準(zhǔn)內(nèi)核進(jìn)行配置,這里要考慮的問(wèn)題是如何如何分配片內(nèi)存儲(chǔ)器和片外存儲(chǔ)器的使用。片內(nèi)存儲(chǔ)器的資源是很寶貴的,所以要先確定系統(tǒng)運(yùn)行所需要的片內(nèi)ROM或RAM,在滿足性能的條件下,盡可能使用較少的片內(nèi)存儲(chǔ)器。

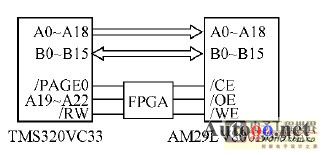

對(duì)于一個(gè)實(shí)際的系統(tǒng),光有片內(nèi)存儲(chǔ)器一般是不夠的,尤其是考慮到要進(jìn)行嵌入式操作系統(tǒng)的移植,所以還要增加片外存儲(chǔ)器。Niso II通過(guò)Avalon總線和片外存儲(chǔ)器以及外部設(shè)備連接。外部存儲(chǔ)器件的類型包括SRAM、SDRAM、DDR2、Flash等,外部設(shè)備包括UART串行口等。本設(shè)計(jì)采用SDRAM.

接著是添加PIO端口,定義輸入輸出端口,主要的目的是用于Nios II讀取數(shù)字量。Nios II所采用的時(shí)鐘和FPGA 的時(shí)鐘密切相關(guān),一般是通過(guò)鎖相環(huán)PLL 把外部輸入的時(shí)鐘進(jìn)行倍頻之后再送給Nios II來(lái)作為主頻使用,同時(shí)外部設(shè)備也使用時(shí)鐘信號(hào)。外部時(shí)鐘信號(hào)為25MHz,而經(jīng)過(guò)倍頻后為50MHz.

至此,主要的配置過(guò)程就結(jié)束了。但是還是需要配置如下部分:

(1) 分配存儲(chǔ)器和外部設(shè)備的基地址和中斷請(qǐng)求優(yōu)先級(jí);

(2) 設(shè)定NiosII處理器的啟動(dòng)地址,本設(shè)計(jì)把片內(nèi)存儲(chǔ)器設(shè)定為Nios II的啟動(dòng)地址。

(3) 在生成NiosⅡ系統(tǒng)時(shí),可以選擇生成Verilog語(yǔ)言還是VHDL 語(yǔ)言,本設(shè)計(jì)采用VHDL語(yǔ)言進(jìn)行設(shè)計(jì);

(4) 最后生成的qsf文件,相當(dāng)于整個(gè)工程的文件,但是關(guān)于配置管腳使用的部分,需要用戶去生成。生成的方法可以在圖形界面下配置,也可以通過(guò)寫tcl文件的方法。寫tcl文件的方法一般來(lái)講,對(duì)于大型工程,還是比較方便的。

(5) 編譯整個(gè)NiosⅡ系統(tǒng),在Altera 提供的開(kāi)發(fā)環(huán)境Quartus II 中進(jìn)行編譯。頂層設(shè)計(jì)文件可以使VHDL 也可以是原理圖的形式。

(6) 采用JATG口進(jìn)行下載,把生成的的SOF文件下載到FPGA里。

2系統(tǒng)軟件設(shè)計(jì)

Altera公司為了用戶方便使用Nios II來(lái)快速研制產(chǎn)品,提供了功能強(qiáng)大、易于使用的Nios II集成開(kāi)發(fā)環(huán)境,與一般的嵌入式系統(tǒng)開(kāi)發(fā)設(shè)計(jì)比較類似。在生成NiosII的過(guò)程中已經(jīng)自動(dòng)生成了需要使用的頭文件(一般是C語(yǔ)言的頭文件),同時(shí)一般外圍設(shè)備的驅(qū)動(dòng)程序也可以生成。對(duì)于嵌入式操作系統(tǒng),可以使用用戶自己裁剪的ucLinux內(nèi)核也可以使用Altera提供的操作系統(tǒng)內(nèi)核。本設(shè)計(jì)使用Altera公司提供的Nios II 9.0版本的開(kāi)發(fā)環(huán)境。

2.1 SD卡初始化

在對(duì)SD 卡進(jìn)行讀/寫之前,必須知道卡的類型、卡的容量、卡的大小等信息。具體來(lái)說(shuō),初始化函數(shù)主要完成以下工作:

(1) 微處理器(這里指Nios II)復(fù)位SD卡,激活SD卡內(nèi)部控制電路進(jìn)行初始化處理,使SD卡進(jìn)入SPI 模式;

(2) 發(fā)送命令查詢SD卡是否支持3.3V供電;

(3) 調(diào)整SPI時(shí)鐘頻率;

(4) 根據(jù)編譯選項(xiàng)使能或者禁止通信過(guò)程中的CRC校驗(yàn);

(5) 設(shè)置用于讀/寫操作的塊數(shù)據(jù)長(zhǎng)度;

(6) 最后是初始化全局變量sds.

SD卡初始化函數(shù)INTSU SD_Initialize(viod)就是用于完成以上任務(wù)的,它讀取SD卡內(nèi)部CSD寄存器,然后對(duì)全局變量sds進(jìn)行賦值。

2.2 SD卡讀寫操作

對(duì)SD卡的讀寫操作需要知道SD 卡的一些基本的屬性:插入卡座中SD卡的型號(hào);SD卡中全部塊的數(shù)量;SD卡的最大數(shù)據(jù)塊的長(zhǎng)度;一次可擦除的塊數(shù)量;卡的讀取、寫入、擦除操作的超時(shí)時(shí)間。

SD卡讀/寫軟件包中定義了一個(gè)全局變量sds,軟件包的很多地方使用了這個(gè)全局變量。SD卡的寫操作包括寫單塊和寫多塊兩種方式。SD卡的初始化函數(shù)SD_Initialixe()已經(jīng)調(diào)用SD_SetBlockLen()函數(shù)設(shè)定了讀/寫數(shù)據(jù)的長(zhǎng)度為SD_BLOCKSIZE 字節(jié),所以卡初始化以后,讀寫都必須以塊為單位。

3 SD卡驅(qū)動(dòng)設(shè)計(jì)

Nios II軟件架構(gòu)是建立在HAL(Hardware Abstraction Layer)基礎(chǔ)之上的。HAL為Nios II的軟件開(kāi)發(fā)者提供了操作底層硬件的編程接口。設(shè)備驅(qū)動(dòng)驅(qū)動(dòng)程序的編制一般要使用HAL提供的API函數(shù)以及C標(biāo)準(zhǔn)庫(kù)等。HAL提供的功能以及它與底層設(shè)備驅(qū)動(dòng)程序之間的關(guān)系如圖3所示,這種模塊化的設(shè)計(jì)架構(gòu)可以加速應(yīng)用程序的開(kāi)發(fā)。使用這種分層的體系架構(gòu),HAL層把應(yīng)用程序和底層硬件驅(qū)動(dòng)程序之間隔離開(kāi)來(lái),使得應(yīng)用程序的開(kāi)發(fā)不依賴于底層HAL和硬件的變化,增加了應(yīng)用程序的可移植性。設(shè)計(jì)驅(qū)動(dòng)程序最重要的是理解具體SD卡的讀寫操作的過(guò)程,之后是如何和嵌入式操作系統(tǒng)連接起來(lái)。在編制好SD卡的驅(qū)動(dòng)程序后,在應(yīng)用程序中操作SD卡就簡(jiǎn)單了。所以編制SD卡的驅(qū)動(dòng)在本設(shè)計(jì)中是重要的一部分。

圖3 基于HAL的系統(tǒng)層次結(jié)構(gòu)

結(jié)束語(yǔ)

本文基于Nios II實(shí)現(xiàn)了對(duì)于SD卡的控制,不僅包括硬件設(shè)計(jì)還包括系統(tǒng)軟件設(shè)計(jì)。傳統(tǒng)的系統(tǒng)設(shè)計(jì)是基于硬核處理器的架構(gòu),系統(tǒng)的硬件設(shè)計(jì)受到了限制。SOPC的設(shè)計(jì)思想使得片上系統(tǒng)的設(shè)計(jì)更加靈活,硬件設(shè)計(jì)的限制因素基本不存在了。在一個(gè)FPGA的芯片上幾乎可以實(shí)現(xiàn)一個(gè)整個(gè)系統(tǒng),對(duì)于系統(tǒng)的小型化的作用是顯著的。本文對(duì)基于NiosⅡ的嵌入式系統(tǒng)的設(shè)計(jì)進(jìn)行了深入的研究,并在此基礎(chǔ)上,設(shè)計(jì)完成了以Altera公司的Cyclone III系列中的EP3C16 FPGA為核心芯片的SOPC開(kāi)發(fā)平臺(tái)。另外本文在此平臺(tái)之上,移植了嵌入式操作系統(tǒng),并在此環(huán)境下實(shí)現(xiàn)了SD卡的接口設(shè)計(jì),因此包括了整個(gè)的硬件和軟件設(shè)計(jì)。在系統(tǒng)設(shè)計(jì)的過(guò)程中,分析了Nios II 的Avalon總線的系統(tǒng)架構(gòu)、SD 卡的通信協(xié)議。