摘要: MicroBlaze 是基于Xilinx公司新一代FPGA器件的軟處理器核。其FSL 總線是FIFO單向鏈路,可以實(shí)現(xiàn)用戶自定義IP核與MicroBlaze內(nèi)部通用寄存器的高速直連。本文對(duì)MicroBlaze的幾種主要總線接口摘要進(jìn)行比較,詳細(xì)分析、介紹FSL總線的結(jié)構(gòu)、特點(diǎn)、工作原理和配置方法。通過(guò)一個(gè)矢量漢字還原的應(yīng)用實(shí)例,具體描述在FPGA片上系統(tǒng)設(shè)計(jì)中利用FSL高速總線整合用戶自定義IP核,實(shí)現(xiàn)軟處理器系統(tǒng)硬件加速的方法及步驟。

關(guān)鍵詞 :FPGA IP核 FSL總線 軟核處理器 MicroBlage

引 言

隨著半導(dǎo)體制造工藝的發(fā)展,以FPGA(現(xiàn)場(chǎng)可編程門陣列)為代表的新一代可編程邏輯器件(PLD)的邏輯資源密度不斷增加,使得可編程技術(shù)很自然地就與系統(tǒng)芯片集成技術(shù)(SoC)的結(jié)合日益緊密,并逐步成為可配置平臺(tái)技術(shù)(configurable platform)的主流。

目前,各主要PLD廠商基于FPGA的可配置平臺(tái)雖然大都采用“微處理器十可編程邏輯”的架構(gòu),但在開發(fā)基于FPGA的嵌入式系統(tǒng)時(shí),卻采用了各自不同的方式來(lái)整合處理器系統(tǒng)與片上的其他邏輯資源(大多數(shù)以用戶IP核形式出現(xiàn))。MicroBlaze軟核處理器是Xilinx公司為其FPGA器件開發(fā)的,其特有的FSL(Fast Simplex Link,快速單向鏈路)總線,可以實(shí)現(xiàn)用戶IP核與軟核處理器的高速連接,為設(shè)計(jì)者提供了一條解決這類問(wèn)題的途徑。

1 MicroBlaze軟核處理器

1.1 概 述

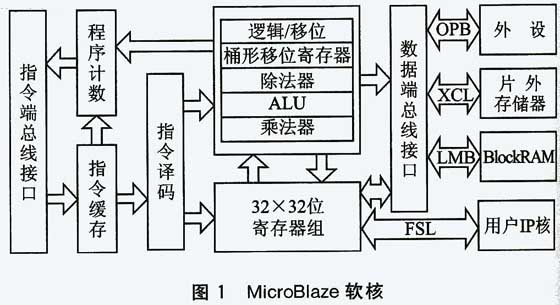

MicroBlaze是基于Xilinx公司FPGA的微處理器軟IP核。它采用RISC架構(gòu)和哈佛結(jié)構(gòu)的32位指令和數(shù)據(jù)總線,內(nèi)部有32個(gè) 32位寬度的通用寄存器;在150 MHz的時(shí)鐘頻率下,最高可達(dá)到125 DMIPS的處理性能,其邏輯結(jié)構(gòu)如圖1所示(圖中省略了指令側(cè)的同類接口)。使用Xilinx公司提供的EDK(嵌入式系統(tǒng)開發(fā)套件),可以在參數(shù)化的圖形界面下方便地完成嵌入式軟處理器系統(tǒng)的設(shè)計(jì)。其突出的優(yōu)點(diǎn),一是設(shè)計(jì)靈活性;二是可以整合用戶自定義IP核,使得算法可以在硬件中并行地執(zhí)行而不是在軟件中串行執(zhí)行,從而極大地加速軟件的執(zhí)行速度,即所謂的硬件加速。

1.2 MicroBlaze軟核總線接口

MicroBlaze軟處理器核具有豐富的接口資源。目前,最新版本的MicroBlaze軟核支持的接口標(biāo)準(zhǔn)有:

◆帶字節(jié)允許的OPB(On-chip Peripheral Bus,片上外設(shè)總線)V2.0接口;

◆高速的LMB(Local Memory Bus,本地存儲(chǔ)器總線)接口;

◆FSL 主從設(shè)備接口;

◆XCL(Xilinx Cache Link,Xilinx緩存鏈路)接口;

◆與MDM(微處理器調(diào)試模塊)連接的調(diào)試接口。

OPB是對(duì)IBM Core Connect片上總線標(biāo)準(zhǔn)的部分實(shí)現(xiàn),適用于將IP核作為外設(shè)連接到MicroBlaze系統(tǒng)中。LMB用于實(shí)現(xiàn)對(duì)片上的blockRAM的高速訪問(wèn)。 FSL是MicroBlaze軟核特有的一個(gè)基于FIFO的單向鏈路,可以實(shí)現(xiàn)用戶自定義IP核與 MicroBlaze內(nèi)部通用寄存器的直接相連;而 XCL則是MicroBlaze軟核新增加的,用于實(shí)現(xiàn)對(duì)片外存儲(chǔ)器的高速訪問(wèn)。 MicroBlaze軟核還有專門的調(diào)試接口,通過(guò)參數(shù)設(shè)置,開發(fā)人員可以只使用特定應(yīng)用所需要的處理器特性。

1.3 MicroBIaze系統(tǒng)的硬件加速

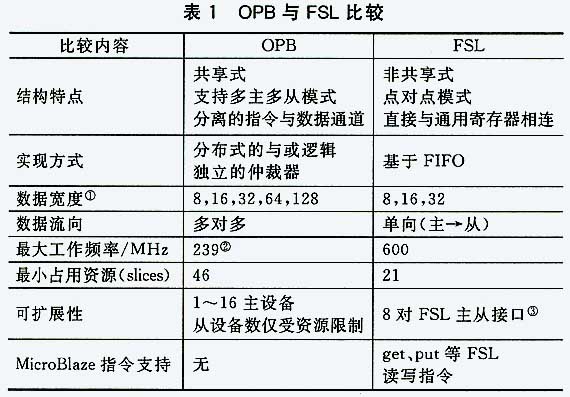

將用戶IP核整合到基于MicroBlaze的嵌入式軟核處理器系統(tǒng)中,通常有兩種方法:一種方法是將IP核連接到OPB總線;第二種方法就是將用戶IP連接到MicroBlaze專用的FSL總線上。OPB與FSL比較如表1所列。

注:①數(shù)據(jù)分別來(lái)自opb_v20和FSL_v20數(shù)據(jù)手冊(cè);

②該數(shù)據(jù)是在總線配置為1主2從情況下得到的;

③該數(shù)據(jù)對(duì)MicroBlaze軟核而言。

從表1可見,盡管OPB和FSL都是MicroBlaze軟核與FPGA其他片上邏輯資源連接的主要途徑,但其特點(diǎn)決定了分工是不同的:OPB總線適用于將低速和低性能要求的設(shè)備連接到MicroBlaze系統(tǒng)中;而FSL總線則適用于將時(shí)間要求高的用戶自定義IP核整合到基于 MicroBlaze的軟核系統(tǒng)中,以實(shí)現(xiàn)硬件加速。

2 FSL總線

2.1 FSL總線接口

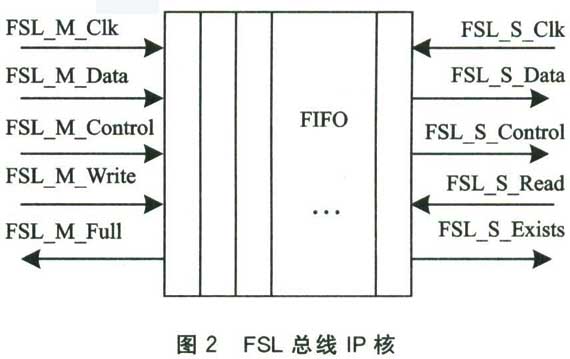

FSL總線是一個(gè)基于FIFO的單向點(diǎn)對(duì)點(diǎn)通信總線,主要用于FPGA的兩個(gè)模塊問(wèn)進(jìn)行快速的通信。FSL總線IP核結(jié)構(gòu)如圖2所示,F(xiàn)SL接口的I/O信號(hào)如表2所列。

該接口的主要特點(diǎn):

◆單向的點(diǎn)對(duì)點(diǎn)通信;

◆非共享的無(wú)仲裁通信機(jī)制;

◆支持控制位與數(shù)據(jù)分離的通信;

◆基于FIFO的通信模式;

◆可配置的數(shù)據(jù)寬度;

◆高速的通信性能(獨(dú)立運(yùn)行達(dá)到600 MHz)。

2.2 FSL總線的寫操作時(shí)序

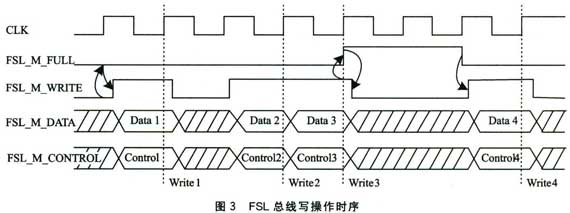

對(duì)FSL總線的寫操作是由FSL_M_Write信號(hào)控制的。圖3是FSL總線的寫操作時(shí)序。FSL主設(shè)備在第一個(gè)時(shí)鐘上升沿檢查到 FSL_M_Full 信號(hào)未置高,就允許主設(shè)備將FSL_M_Write置高,并將FSL_M_Data和FSL_M_Control推上總線,在下一個(gè)時(shí)鐘周期這些數(shù)據(jù)就被總線讀取并送入FIFO了。圖中的Write2和Write3是一組“背靠背”的連續(xù)寫操作。在Write3時(shí),F(xiàn)IFO滿使得 FSL_M_Full信號(hào)被置高,迫使主設(shè)備取消自己的FSL_M_Write信號(hào),直到一次讀操作將FSL_M_Full置低后,才可以發(fā)起另一次寫操作。因此,圖中暗示著在 Write4處也發(fā)生了一次從設(shè)備的讀操作,否則FSL_M_Full將再次置高。

2.3 FSL總線讀操作時(shí)序

對(duì)FSL總線的讀操作是由FSL_S_Read信號(hào)控制的,圖4是FSL從設(shè)備的3次讀操作時(shí)序。當(dāng)FSL總線上存在有效數(shù)據(jù)(FSL_S_Exists =‘1’),F(xiàn)SL_M_Data上的數(shù)據(jù)和FSL_M_Control上的控制位就立即可以被FSL從設(shè)備讀取。一旦從設(shè)備完成讀操作, FSL_S_Read信號(hào)必須置高一個(gè)時(shí)鐘周期,以確認(rèn)從設(shè)備成功完成了一次讀操作。在讀操作發(fā)生后的時(shí)鐘上升沿(圖中Read2 處), FSL_M_Data和FSL_M_Control會(huì)被更新為新數(shù)據(jù),同時(shí)FSL_S_Exists和FSL_M_Full信號(hào)也會(huì)被更新。同樣,這里暗示著在Readl和Read2之間發(fā)生了兩次主設(shè)備的寫操作。

3 FSL總線用法

3.1 使用FSL總線IP核的設(shè)備間通信

目前Xilinx提供的FSL總線IP核的版本是FSL_V20。兩個(gè)設(shè)備要使用FSL進(jìn)行數(shù)據(jù)傳輸,就必須分別作為主設(shè)備或從設(shè)備連接到FSL核上。如果需要進(jìn)行雙向的傳輸,只要兩個(gè)設(shè)備分別作為主從設(shè)備,使用兩個(gè)FSL核連接即可。

無(wú)論是作為主設(shè)備或是從設(shè)備,都需要通過(guò)在設(shè)備的微處理器外設(shè)描述文件(MPD)中進(jìn)行相應(yīng)的定義,以實(shí)現(xiàn)所需類型的FSL接口。下面這段代碼就是一個(gè)分別定義了FSL主設(shè)備接口FSL_OUT和從設(shè)備接口FSL_IN的MPD文件:

BEGIN my_fsl_peripheral

OPTl0N IPTYPE=PERIPHERAL

OPTl0N IMP_NETLIST=TRUE

BUS_INTERFACE BUS=FSL_IN,BUS_STD=FSL,BUS TYPE=SLAVE

BUS_INTERFACE BUS=FSL_OUT,BUS_STD=FSL,BUS_TYPE=MASTER

##Ports

PORT CLK=””,DIR=IN,SIGIS=CLK

PORT RESET=””。DIR=IN

PORT FSL_S_READ=FSL_S_Read,DIR=out,BUS=FSL_IN

PORT FSL_S_DATA=FSL_S_Data,DIR=in,VEC=[o:31],BUS=FSL_IN

PORT FSL_S_CONTROL=FSL_S_Control,DIR=in, BUS=FSL_IN

PORT FSL_s_EXISTS=FSL_S_Exists,DIR=in,BUS=FSL_IN

PORT FSL_M_WRITE=FSL_M_Write,DIR=out,BUS=FSL_OUT

PORT FSL_M_DATA=FSL_M_Data,DIR=out,VEC=[o:31],BUS=FSL_OUT

PORT FSL_M_CONTROL=FSL_M_Control,DIR=out, BUS=FSL_OUT

PORT FSL_M_FULL=FSL_M_Full,DIR=in,BUS=FSL_OUT

3.2 通過(guò)FSL與MicroBlaze通信

MicroBlaze軟核的FSL總線接口支持最多8對(duì)FSL連接,具體實(shí)現(xiàn)多少接口由系統(tǒng)硬件描述文件(MHS)中的參數(shù) C_FSL_LINKS決定。默認(rèn)情況下該參數(shù)為0,表示不實(shí)現(xiàn)FSL接口。當(dāng)需要使用FSL總線把MicroBlaze和FPGA中的一個(gè)或多個(gè)邏輯模塊連接起來(lái)時(shí),必須設(shè)置該參數(shù)的值為相應(yīng)的模塊數(shù)。該參數(shù)的取值范圍是0~8。

在MicroBlaze指令集中還有針對(duì)FSL總線操作的指令,它們分別是:

◆get,put——阻塞式數(shù)據(jù)讀寫FSL,控制信號(hào)被置為0;

◆nget,nput——非阻塞式數(shù)據(jù)讀寫FSL,控制信號(hào)被置為0;

◆cget,cput——阻塞式控制位讀寫FSL,控制信號(hào)被置為1;

◆ncget,ncput——非阻塞式控制位讀寫FSL,控制信號(hào)被置為1。

4 FSL總線應(yīng)用實(shí)例

在下面的實(shí)例中,嘗試通過(guò)FSL總線技術(shù),將實(shí)現(xiàn)特定函數(shù)功能的用戶自定義IP核整合到MicroBlaze軟核系統(tǒng)中,以實(shí)現(xiàn)硬件加速的目的。這里以一個(gè)矢量漢字(vector font)還原功能的硬件模塊的整合為例,說(shuō)明FSL總線的應(yīng)用過(guò)程。所使用的開發(fā)平臺(tái)是Memec Insight 公司生產(chǎn)的Virtex—II系列的MicroBlaze開發(fā)板,板上采用的FPGA器件為Virtex—II 1000,系統(tǒng)時(shí)鐘為100 MHz,開發(fā)工具為Xilinx公司的EDK 6.3及ISE 6.3。

4.1 FSL總線應(yīng)用方案

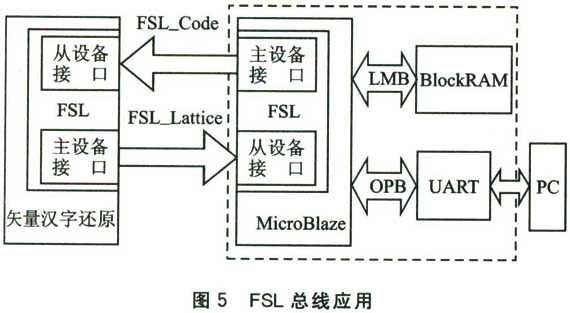

如圖5所示,vectOr_font核通過(guò)FSL_Code-與FSL_Lattice兩條FSL總線與MicroBlaze軟核直接相連。

對(duì)于FSL_Code總線,MicroBlaze核是主設(shè)備,而vector_font核是從設(shè)備。這樣MicroBlaze可以通過(guò) FSL_Code總線向vectOr_font核發(fā)送漢字的區(qū)位碼(或者其他格式的漢字編碼,由使用的矢量字庫(kù)和還原算法決定)以及漢字的屬性信息(如字體、大小等)。

對(duì)于FSL_Lattice總線則正好相反。vector font 核作為主設(shè)備可以通過(guò)它向MicroBlaze核發(fā)送經(jīng)過(guò)還原處理后的漢字點(diǎn)陣數(shù)據(jù)以及漢字點(diǎn)陣尺寸信息(用于將點(diǎn)陣數(shù)據(jù)在顯存中組織成正確的顯示格式)。

4.2 數(shù)據(jù)傳輸指令與控制位指令的應(yīng)用

FSL 提供的獨(dú)立于數(shù)據(jù)傳輸?shù)目刂莆豢梢杂脕?lái)對(duì)正在傳輸中的數(shù)據(jù)進(jìn)行標(biāo)記。為了區(qū)分區(qū)位碼數(shù)據(jù)與漢字屬性數(shù)據(jù),以及點(diǎn)陣數(shù)據(jù)與漢字點(diǎn)陣尺寸數(shù)據(jù)。 MicroBlaze分別通過(guò)FSL的數(shù)據(jù)傳輸指令和控制位傳輸指令來(lái)發(fā)送漢字的區(qū)位碼和漢字屬性信息,接收點(diǎn)陣數(shù)據(jù)和漢字點(diǎn)陣尺寸信息。對(duì)應(yīng)的實(shí)現(xiàn)代碼如下:

//使用非阻塞的數(shù)據(jù)寫函數(shù)向FSL總線寫入漢字區(qū)位碼Microblaze_nbwrite_datatsl(code,O)

//使用非阻塞的控制位寫函數(shù)向FSL總線寫入漢字屬性信息maicroblaze_cnbwrite_cnlfsl(attibute,O)

//使用非阻塞的數(shù)據(jù)讀函數(shù)從FSL總線讀取漢字點(diǎn)陣數(shù)據(jù)microblaze_nbread_datafsl(1attice,O)

//使用非阻塞的控制位讀函數(shù)從FSL總線讀取漢字點(diǎn)陣尺寸信息microblaze_cnbread_cnlfsl(size,O)

代碼中用到的與FSL有關(guān)函數(shù)的定義,都在include目錄下的mb_interface.h文件中。其中,各函數(shù)的第二個(gè)參數(shù)代表進(jìn)行讀寫操作的 FSL總線接口的編號(hào),對(duì)應(yīng)Mi—croBlaze軟核的8對(duì)FSL接口。該參數(shù)的取值范圍從0到7。本例中,MicroBlaze只使用了一對(duì) FSL接口,故而值為0。

4.3 實(shí)現(xiàn)步驟

首先,在Base System Wizard中設(shè)計(jì)圖5虛線框中所示的一個(gè)簡(jiǎn)單的MicroBlaze嵌入式處理器系統(tǒng)。然后,在XPS集成開發(fā)環(huán)境下完成用戶自定義IP核(本例中即 vectoz__font核)的添加、Microblaze核FSL接口的添加(設(shè)置參數(shù) C_FSL_LINKS=1),同時(shí)添加兩個(gè)FSL總線IP核,分別用于實(shí)現(xiàn)FSL_Code和FSL_Lattice總線。另外,將兩個(gè)FSL總線IP 核的參數(shù)C_USE_CONTROL置為1,以打開FSL總線的控制位傳輸功能。所有這些改動(dòng),最后都會(huì)被更新到MES文件中。這樣,硬件平臺(tái)生成工具 platgen就可以根據(jù)它生成所需要的FPGA配置文件了。

硬件的實(shí)現(xiàn)完成后,進(jìn)行相應(yīng)軟件參數(shù)的設(shè)置,如將系統(tǒng)標(biāo)準(zhǔn)輸入輸出設(shè)備指向UART模塊等。然后,用庫(kù)生成工具libgen,根據(jù)MSS(系統(tǒng)軟件描述文件)文件,將所需外設(shè)函數(shù)庫(kù)的頭文件添加進(jìn)工程中。

通過(guò)調(diào)用這些函數(shù),可以操作和控制這些外設(shè)。通過(guò)Tool項(xiàng)里的build命令,調(diào)用mb—gcc:編譯工具,將編寫的應(yīng)用程序編譯成ELF文件,再用 updatebitstrcam命令將程序代碼對(duì)應(yīng)的RAM初始化數(shù)據(jù)添加到前面生成的FPGA配置文件中,生成最終的bit配置文件。最后,使用 download命令將bit文件下載到目標(biāo)板中。

以上就是整個(gè)FSL應(yīng)用實(shí)例設(shè)計(jì)的實(shí)現(xiàn)過(guò)程。本例只是為了說(shuō)明FSL總線的使用。實(shí)際應(yīng)用中,還可以根據(jù)具體情況通過(guò)FSL,將更多的用戶自定義IP核(如DCT、FFT等)添加到.MicroBlaze軟核系統(tǒng)中去。

5.結(jié) 語(yǔ)

在嵌入式系統(tǒng)的開發(fā)中,人們一直希望能夠有一個(gè)滿足自己需要的“定制”的嵌入式處理器,而不是手頭大量存在的通用微處理器。但是,直接將用戶自定義IP核添加到處理器核中,不僅受到處理器原架構(gòu)的束縛,還有可能降低處理器的性能(處理器工作頻率);而通過(guò)與內(nèi)部寄存器直接相連的FSL接口,用戶自定義IP 可以在不破壞處理器原有結(jié)構(gòu)的情況下,緊密地與MicroB- laze軟核結(jié)合在一起。這樣,即使關(guān)鍵路徑覆蓋了用戶IP 核,由于它在處理器內(nèi)核之外,也不會(huì)導(dǎo)致處理器時(shí)鐘頻率的降低。

通過(guò)對(duì)FSL總線的分析以及上述實(shí)例的驗(yàn)證,證明了在基于MicroBlaze的SoC 系統(tǒng)設(shè)計(jì)中,一方面可以針對(duì)具體應(yīng)用進(jìn)行“量體裁衣”式的設(shè)計(jì);另一方面,利用其專用的FSL總線接口技術(shù),實(shí)現(xiàn)嵌入式軟處理器系統(tǒng)與用戶自定義邏輯的整合,從而在不提高系統(tǒng)主頻的前提下,通過(guò)部分函數(shù)功能的硬件實(shí)現(xiàn)來(lái)提升系統(tǒng)的性能。