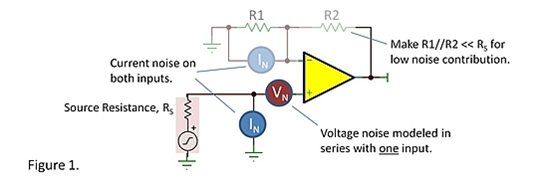

以之前對電阻噪聲的討論為基礎(chǔ),這次讓我們一起學(xué)習(xí)放大器噪聲的一些基本知識。對于低噪聲應(yīng)用來講,同相放大電路是最常見的,因此我們將主要探討同相運(yùn)算放大器。 如圖1所示,將輸入源等效為一個(gè)電壓源與一個(gè)電阻串聯(lián),我們知道源電阻RS的噪聲與其電阻平方根值是成正比例關(guān)系的(如圖2中的直線所示)。低噪聲放大器的設(shè)計(jì)目標(biāo)是在電阻引入噪聲的基礎(chǔ)上,盡可能少地引入運(yùn)放附加的噪聲。

如圖1所示,放大器噪聲的等效模型為在一個(gè)輸入端串聯(lián)一個(gè)電壓噪聲,同時(shí)在兩端分別連接一個(gè)電流噪聲源。把電壓噪聲看作失調(diào)電壓的時(shí)變元件。同樣,電流噪聲是輸入偏置電流的時(shí)變元件,在每個(gè)輸入端各有一個(gè)。由于我們總能將反相輸入端的電流噪聲值降到最低,因此我們將忽略它。

圖2給出了BJT做為輸入級的OPA209和JFET做為輸入級的OPA140這兩個(gè)運(yùn)算放大器電路的總輸入?yún)⒖荚肼暤那€。在25°C的時(shí)候,兩條曲線均與源電阻的噪聲成比例關(guān)系。對每個(gè)運(yùn)算放大器而言,都通過平方和的均方根的方式來對三種噪聲源進(jìn)行了一個(gè)求和。你也許會在某些運(yùn)算放大器的數(shù)據(jù)手冊上看到這樣的圖形。

當(dāng)源電阻阻值減小時(shí),它的約翰遜噪聲隨之減小(由阻值平方根值的倒數(shù)決定),在一定程度上,放大器的噪聲電壓將起到主導(dǎo)作用。總的噪聲將等于放大器的電壓噪聲。當(dāng)源電阻阻值增加時(shí),流過源電阻的電流噪聲將線性增加,而且會增加很快且最終會超過源電阻的噪聲。因此當(dāng)源電阻阻值很高時(shí),電流噪聲將會起主導(dǎo)作用。

當(dāng)源電阻值為2kΩ或者更低時(shí),低噪聲放大器的設(shè)計(jì)會遇到最大的挑戰(zhàn)。較低的源電阻噪聲就要求放大器有很低的噪聲電壓。雙極性(BJT輸入)放大器通常在這方面比較擅長。還需注意的是,如圖2所示,在一個(gè)最佳位置, OPA209的總噪聲與源電阻噪聲幾乎相等。源阻最佳噪聲性能發(fā)生在RS=VN/IN。

當(dāng)源電阻阻值大約為20kΩ時(shí),F(xiàn)ET輸入的放大器幾乎不會引入任何的額外噪聲。只有當(dāng)源電阻阻值達(dá)到幾個(gè)GΩ的時(shí)候,F(xiàn)ET運(yùn)算放大器的電流噪聲才會產(chǎn)生影響。可以遵循以下準(zhǔn)則:當(dāng)源電阻阻值小于10kΩ時(shí),低噪聲的BJT放大器會產(chǎn)生較低的噪聲。當(dāng)源電阻阻值大于10kΩ時(shí),F(xiàn)ET或者CMOS的運(yùn)算放大器才會可能會有優(yōu)勢。

反饋網(wǎng)絡(luò)中的R1和R2也會產(chǎn)生一定的噪聲,但通常情況下是可以忽略的。當(dāng)R1和R2的并聯(lián)值小于或者等于RS值的十分之一時(shí),它們將僅僅使總噪聲的值產(chǎn)生小于10% (<1dB) 的增量。無論這些電阻的比值是多少,這都會是個(gè)事實(shí)。在圖2中,反饋網(wǎng)絡(luò)中元件的噪聲被設(shè)定為零。

當(dāng)然,還有很多需要了解的,如想了解更多,我推薦我的同事Art Kay寫的一本書“Operational Amplifier Noise: Techniques and Tips for Analyzing and Reducing Noise”。

思考點(diǎn):OPA140在10kΩ 之上有一個(gè)非常寬的電阻范圍,在這個(gè)范圍之內(nèi),噪聲性能很好。是否存在一種方法可以使得較低的源電阻值可以達(dá)到同樣的效果?

感謝閱讀并且歡迎給出建議。