一、方案設(shè)計(jì)基礎(chǔ)

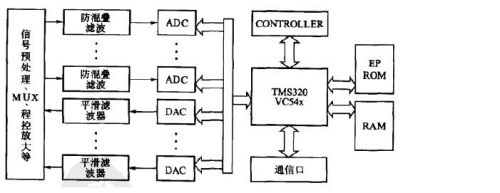

DSP方案設(shè)計(jì)包括硬件設(shè)計(jì)以及軟件設(shè)計(jì)兩部分。硬件設(shè)計(jì)又稱(chēng)為目標(biāo)板設(shè)計(jì),是基于算法需求分析、成本、體積、功耗等全面考慮的基礎(chǔ)上完成的設(shè)計(jì),如圖1-1是一個(gè)典型的DSP目標(biāo)板結(jié)構(gòu)圖。

圖1-1 DSP目標(biāo)板

二、數(shù)字電臺(tái)原理設(shè)計(jì)

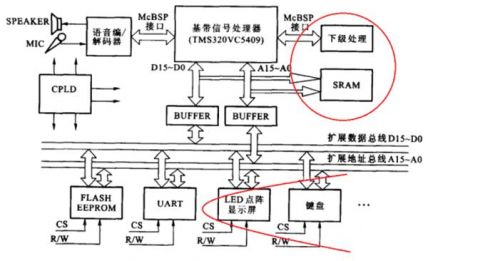

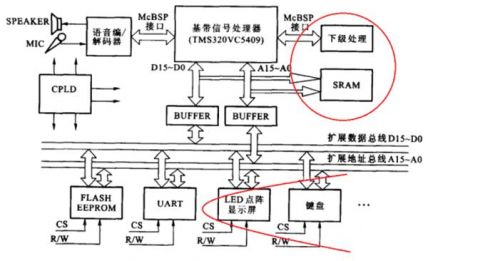

采用CVSD(連續(xù)可變斜率增量調(diào)制)語(yǔ)音編解碼和UART數(shù)據(jù)接口,送入基帶處理模塊的語(yǔ)音數(shù)據(jù)流最高為16kbps,數(shù)據(jù)流最高為9.6kbps,DSP的基帶處理,包括進(jìn)行信道編/譯碼、加入/提取信令、組/拆幀等,送出64kbps數(shù)據(jù)到數(shù)字調(diào)制/解調(diào)電路。

圖1-2

對(duì)于數(shù)字語(yǔ)音通信,從MIC(話筒)來(lái)的語(yǔ)音信號(hào)在語(yǔ)音編解碼器中,經(jīng)過(guò)CVSD編碼變?yōu)?6kbps串行數(shù)字語(yǔ)音流。通過(guò)VC5409的一個(gè)多通道緩沖串口(McBSP)接收引腳送入,再進(jìn)行信道編碼,以增強(qiáng)糾錯(cuò)能力。

從VC5409上引出的16位數(shù)據(jù)線(D15-D0)與16位地址線(A15-A0),經(jīng)過(guò)了一級(jí)總線驅(qū)動(dòng)器(BUFFER),增強(qiáng)驅(qū)動(dòng)能力,以擴(kuò)展足夠的外設(shè)。

在此基帶處理模塊的設(shè)計(jì)中,需要擴(kuò)展EEPROM存儲(chǔ)器與通用異步收發(fā)器(UART)。擴(kuò)展EEPROM是為了存儲(chǔ)用戶的數(shù)據(jù)以及編制的軟件,并在目標(biāo)板上電時(shí),通過(guò)Bootloader引導(dǎo)DSP片內(nèi)RAM,完成用戶程序的自啟動(dòng)。擴(kuò)展UART接口是針對(duì)數(shù)據(jù)通信任務(wù),主控機(jī)或者上位機(jī)可通過(guò)UART接口與基帶處理模塊上的VC5409進(jìn)行數(shù)據(jù)交換。

對(duì)于上圖1-2,本電臺(tái)基帶處理系統(tǒng)包括7個(gè)子模塊:語(yǔ)音前端、基帶DSP、UART、BUFFER、擴(kuò)展存儲(chǔ)器、CPLD控制單元、電源。不包括下級(jí)處理模塊,以及擴(kuò)展的外設(shè)顯示屏、鍵盤(pán)等。

三、設(shè)計(jì)中每部分的作用

1、基帶DSP

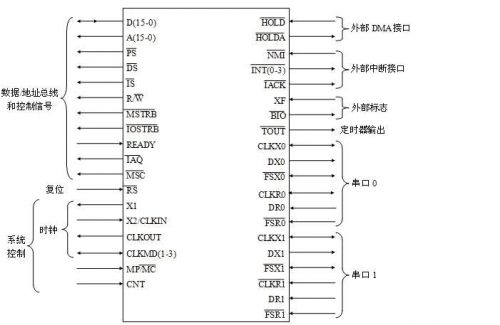

TMS320VC5409芯片主要包括CPU、片內(nèi)存儲(chǔ)器和片內(nèi)外設(shè)三個(gè)部分,它們通過(guò)片內(nèi)總線相互連接,交換數(shù)據(jù)信息和控制信息。TMS320VC5409配置有片內(nèi)RAM 32K,片內(nèi)ROM 16K,三個(gè)串口,一個(gè)并口。

VC5409的三個(gè)串口使用了其中的兩個(gè),一個(gè)用于接收和發(fā)送語(yǔ)音編碼信號(hào),另一個(gè)用于接收和發(fā)送標(biāo)準(zhǔn)輸入信號(hào)。由于DSP的串口是極其寶貴的資源,所以需要剩下一個(gè)串口通過(guò)CPLD預(yù)留出來(lái),以備系統(tǒng)擴(kuò)展。考慮到系統(tǒng)的完整性,還預(yù)留了HPI接口(HD0-HD7)。

VC5409的總線均連接到了總線驅(qū)動(dòng)器SN74LVTH16245上,所有外設(shè)的地址線和數(shù)據(jù)線連接到總線驅(qū)動(dòng)器的另一端,這樣連接的目的是數(shù)據(jù)緩沖和隔離保護(hù)DSP芯片VC5409,避免DSP芯片被燒壞。

由于DSP芯片的程序一般是燒在存儲(chǔ)器中的,但是這些非遺失性的存儲(chǔ)器(ROM)訪問(wèn)速度較慢,一般不能直接用做程序存儲(chǔ)器使用,需要在上電時(shí)引導(dǎo)到CPU的高速程序存儲(chǔ)器中,這個(gè)過(guò)程稱(chēng)為BOOTLOADER。VC54xx系列DSP在片上ROM放有引導(dǎo)程序,使用該引導(dǎo)程序可以很方便的在DSP上電復(fù)位時(shí)將用戶的應(yīng)用程序從外部存儲(chǔ)設(shè)備中裝入到DSP片內(nèi)存儲(chǔ)器和高速片外程序存儲(chǔ)器中。本設(shè)計(jì)是將程序燒在EPROM中的,所以采用的是EPROM并口引導(dǎo)方式。

2、DSP電源設(shè)計(jì)

DSP電源可以采用由TPS73HD318芯片組成的雙電源電路,1.8V主要為VC5409的內(nèi)部邏輯提供電壓,包括CPU、時(shí)鐘電路和所有外設(shè);3.3V電壓為外部接口引腳供電;它還帶有200ms寬脈沖的復(fù)位信號(hào),其中TPS-RS就是復(fù)位信號(hào),可利用此信號(hào)使DSP、URAT復(fù)位。電源電壓為12V,12V的電源電壓通過(guò)穩(wěn)壓器7805與7905轉(zhuǎn)換為5V電壓。選用12V作為系統(tǒng)的電源電源是因?yàn)樾酒?span lang="EN-US" xml:lang="EN-US">MC3418需要的電壓是12V,為所有芯片里面需呀供電電壓最高的,而其他芯片只需5V甚至更低。

3、語(yǔ)音前端設(shè)計(jì)

該功能模塊的主要任務(wù)是對(duì)輸入的低功率語(yǔ)音信號(hào)進(jìn)行放大濾波,轉(zhuǎn)換為負(fù)載所需的足夠的輸出功率信號(hào)。之后需要再對(duì)語(yǔ)音信號(hào)進(jìn)行編碼。語(yǔ)音前端可分為信號(hào)放大濾波電路與語(yǔ)音編解碼電路。

語(yǔ)音信號(hào)放大濾波電路,是為了把信號(hào)增大到可利用的程度。在語(yǔ)音編碼前端對(duì)信號(hào)進(jìn)行放大選用LM356運(yùn)算放大器,其輸入性能比通常的運(yùn)放增強(qiáng)一個(gè)數(shù)量級(jí)以上,可以應(yīng)用于采樣和同步電路、快速的A/D和D/A轉(zhuǎn)換器、寬帶、低噪聲等放大器。

編/解碼芯片采用MC3418。這但是單片MC3418只能工作在半雙工模式。為了完成全雙工,采用了兩片MC3418,分別用于編解碼電路。

編碼和解碼電路的外圍電路相同,編碼電路將編/解碼選擇引腳(15腳)置高電平,解碼電路將此引腳接地即處于低電平。

4、UART部分

擴(kuò)展設(shè)備UART包括電平轉(zhuǎn)換器和UART協(xié)議控制器。電平轉(zhuǎn)換器將計(jì)算機(jī)串口送來(lái)的15v數(shù)據(jù)電平轉(zhuǎn)化為0~5V的TTL電平。UART協(xié)議控制器選用的是TL160C550。

TL160C550的作用是對(duì)從外圍器件接收的信號(hào)實(shí)行串行到并行的轉(zhuǎn)換,對(duì)從CPU接收的信號(hào)實(shí)行并行到串行的轉(zhuǎn)換。在ACE(異步通信單元)工作的任何時(shí)候CPU都可以讀ACE(異步通信單元)的狀態(tài)。該接口使用TL16C550芯片是TL16C450異步通信單元(ACE)的升級(jí)產(chǎn)品。TL16C550內(nèi)嵌完整的MODEM控制協(xié)議和處理器終端系統(tǒng),減輕用戶在通信協(xié)議上的軟件編程以及管理工作。TL16C550還有可編程的片內(nèi)波特率產(chǎn)生器,能對(duì)基準(zhǔn)時(shí)鐘進(jìn)行分頻并產(chǎn)生內(nèi)部發(fā)生器邏輯的16*時(shí)鐘,DSP可以在任何時(shí)刻訪問(wèn)其內(nèi)部寄存器。它使用1.8432MHz和3.072MHz晶體頻率的波特率產(chǎn)生器可得到各種的數(shù)據(jù)速率。該系統(tǒng)把UART擴(kuò)展在VC5409的I/O空間。

TL16C550輸出的是TTL電平,所以在跟PC通信時(shí)需要進(jìn)行電平轉(zhuǎn)換,轉(zhuǎn)換為RS-232電平。電平轉(zhuǎn)換使用MAX3238即多通道RS-232驅(qū)動(dòng)器/接收器。

6、總線驅(qū)動(dòng)器

由于DSP芯片的地址總線和數(shù)據(jù)總線的驅(qū)動(dòng)能力有限,從VC5409上引出的16為數(shù)據(jù)線(D15-D0)與16位地址線(A15-10),經(jīng)過(guò)一級(jí)總線驅(qū)動(dòng)器(BUFFER),可以有效增強(qiáng)驅(qū)動(dòng)能力,以便擴(kuò)展足夠的外設(shè)。同時(shí)BUFFER起到隔離作用,避免擴(kuò)展的5V高電壓外設(shè)燒毀3.3V的低電壓VC5409。總線驅(qū)動(dòng)器器件選用SN74LVTH16245,這是一種16位總線驅(qū)動(dòng)器,與地址、數(shù)據(jù)總線均為16位的VC5409匹配。其中數(shù)據(jù)總線使用SN74LVTH16245來(lái)進(jìn)行雙向驅(qū)動(dòng),需要特別是針對(duì)數(shù)據(jù)總線進(jìn)行加強(qiáng)驅(qū)動(dòng)能力的設(shè)計(jì);地址總線是單向的,沒(méi)有方向的控制使用SN74LVTH16245單向驅(qū)動(dòng)器就可以了。

7、擴(kuò)展存儲(chǔ)器

由于VC5409為ROM型器件,用戶的運(yùn)行程序和數(shù)據(jù)在掉電后不能保留,需要擴(kuò)展FLASH EEPROM來(lái)加以存儲(chǔ)。