FPGA和ARM的Profibus-DP主站通信平臺(tái)設(shè)計(jì)

孫倩華,滿慶豐,夏繼強(qiáng) 北京航空航天大學(xué)

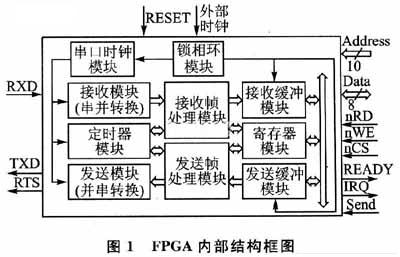

摘要: 提出一個(gè)使用FPGA和ARM微控制器實(shí)現(xiàn)Profibus-DP主站(1類)通信平臺(tái)的解決方案;解析了Profibus-DP通信協(xié)議,重點(diǎn)是令牌輪轉(zhuǎn)協(xié)議;給出了該主站通信平臺(tái)的系統(tǒng)構(gòu)建。該通信平臺(tái)可以獨(dú)立實(shí)現(xiàn)Profibus-DP主站(1類)與其他主站(1類和2類)的令牌傳遞的主主通信功能,以及其與從站的主從通信功能。

Abstract:

Key words :

摘要:提出一個(gè)使用FPGA和ARM微控制器實(shí)現(xiàn)Profibus-DP主站(1類)通信平臺(tái)的解決方案;解析了Profibus-DP通信協(xié)議,重點(diǎn)是令牌輪轉(zhuǎn)協(xié)議;給出了該主站通信平臺(tái)的系統(tǒng)構(gòu)建。該通信平臺(tái)可以獨(dú)立實(shí)現(xiàn)Profibus-DP主站(1類)與其他主站(1類和2類)的令牌傳遞的主主通信功能,以及其與從站的主從通信功能。

Profibus-DP是由西門子公司推出的一種開放式現(xiàn)場(chǎng)總線標(biāo)準(zhǔn),用于現(xiàn)場(chǎng)級(jí)分布式自動(dòng)化外設(shè)之間的高速數(shù)據(jù)傳輸。Profibus在2007年4月突破2000萬節(jié)點(diǎn)大關(guān)。據(jù)PI(世界性的現(xiàn)場(chǎng)總線Profibus用戶組織)稱現(xiàn)在已經(jīng)超過2 500萬個(gè)節(jié)點(diǎn),并希望在2012年突破5 000萬個(gè)節(jié)點(diǎn),年銷售芯片450萬個(gè)。

目前國(guó)內(nèi)業(yè)界對(duì)于Profibus-DP的研究和相關(guān)產(chǎn)品的開發(fā)都是基于國(guó)外提供的專用協(xié)議芯片(主站多數(shù)采用西門子推出的ASPC2,從站多采用SPC3等智能通信芯片),而沒有協(xié)議芯片樣機(jī)開發(fā)的相關(guān)報(bào)道。對(duì)于主站的開發(fā),國(guó)內(nèi)一些科研院所(北航706教研室、中科院、浙大等)也曾利用可編程邏輯器件配合MCU設(shè)計(jì)出簡(jiǎn)單主站的試驗(yàn)產(chǎn)品,但是這些產(chǎn)品僅能實(shí)現(xiàn)單主站的功能,對(duì)于組成強(qiáng)大的Profibu-DP網(wǎng)絡(luò)還望塵莫及。為了打破國(guó)外芯片的壟斷,推動(dòng)國(guó)內(nèi)相關(guān)芯片及產(chǎn)品的開發(fā),本文提出了一種FPGA與ARM相結(jié)合的方式解決Profibu-DP 1類主站的主主通信及主從通信問題,實(shí)現(xiàn)了比較完整的主站研制方案。

1 Profibus-DP主站通信機(jī)理及技術(shù)特性

1.1 Profibus-DP主站通信協(xié)議

Profibus協(xié)議的結(jié)構(gòu)以O(shè)SI為參考模型,DP使用第1層、第2層和用戶接口,第3層到第7層未加以描述。一個(gè)DP系統(tǒng)既可以是一個(gè)單主站結(jié)構(gòu),也可以是一個(gè)多主站結(jié)構(gòu),本文涉及的是多主站結(jié)構(gòu)。多主站結(jié)構(gòu)使用混合的總線訪問控制機(jī)制,主站之間采取令牌控制方式;令牌在主站之間傳遞,擁有令牌的主站擁有總線訪問控制權(quán);主站與從站之間采取主從的控制方式。

令牌是一種特殊的報(bào)文,如下所示:

SD DA SA

SD為開始分界符,DA為目的地址,SA為源地址。令牌環(huán)是所有主站的組織鏈,按照主站的地址構(gòu)成邏輯環(huán)。在這個(gè)環(huán)中,令牌在規(guī)定的時(shí)間內(nèi)按照地址的升序在各主站間依次傳遞,用戶通過編寫令牌傳遞程序保證每個(gè)主站在一個(gè)確切規(guī)定的時(shí)問內(nèi)得到令牌,之后該主站就可以在規(guī)定的時(shí)間內(nèi)與所屬?gòu)恼就ㄐ牛部膳c所有主站通信。其中主站與所屬?gòu)恼鹃g的數(shù)據(jù)通信由主站按已確定的循環(huán)順序自動(dòng)地進(jìn)行處理。

1.2 令牌循環(huán)時(shí)間分析

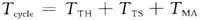

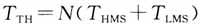

最壞情況下令牌循環(huán)時(shí)間為:

其中,TTH為站點(diǎn)令牌保持時(shí)間,TTS為令牌的整體傳輸延遲,TMA為令牌維護(hù)時(shí)間。在不考慮出錯(cuò)重發(fā)的前提下,N個(gè)主站令牌的整體傳輸延遲TTS=N·TTK,TTk是發(fā)送令牌PDU(協(xié)議數(shù)據(jù)單元)需要的時(shí)間。高優(yōu)先級(jí)報(bào)文的傳送時(shí)間為THMS,報(bào)文數(shù)量為M;低優(yōu)先級(jí)報(bào)文的傳送時(shí)間為TLMS,報(bào)文數(shù)量為L(zhǎng)。假設(shè)所有站點(diǎn)的報(bào)文服務(wù)均含有應(yīng)答,則 代入上述公式可得:

代入上述公式可得:

代入上述公式可得:

代入上述公式可得:

2.2 ARM控制器部分程序設(shè)計(jì)

ARM控制器程序?qū)?yīng)于Profibus通信協(xié)議數(shù)據(jù)鏈路層之上的DDLM直接數(shù)據(jù)鏈路映射程序、主站通信狀態(tài)機(jī)、應(yīng)用層數(shù)據(jù)接口及應(yīng)用層。

本設(shè)計(jì)對(duì)Profibus-DP協(xié)議按層次封裝為函數(shù),層層調(diào)用。

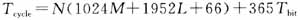

2.2.1 Slave_Handler狀態(tài)機(jī)

Slave_Handler狀態(tài)機(jī)功能塊負(fù)責(zé)實(shí)現(xiàn)主從通信功能,根據(jù)從站狀態(tài)做出相應(yīng)處理,有固定的處理次序,每次調(diào)用Slave_Handler狀態(tài)機(jī)產(chǎn)生一個(gè)DDLM請(qǐng)求,從而控制從站進(jìn)入相應(yīng)的通信狀態(tài)。Slave_Handler狀態(tài)轉(zhuǎn)換圖如圖2所示。

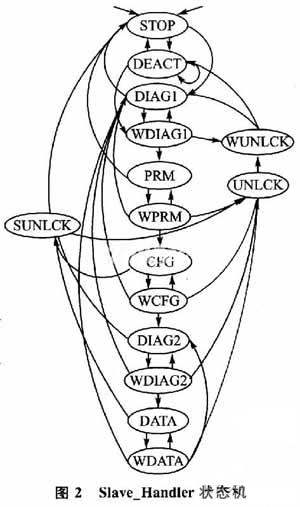

2.2.2 Scheduler和FDL_Controller狀態(tài)機(jī)

Scheduler狀態(tài)機(jī)功能塊負(fù)責(zé)實(shí)現(xiàn)對(duì)Slave_Handler狀態(tài)機(jī)的控制。它向Slave_Handler狀態(tài)機(jī)發(fā)送從站輪詢控制信號(hào),控制其逐步與從站建立數(shù)據(jù)交換關(guān)系。

FDL_Controller狀態(tài)機(jī)由10個(gè)FDL狀態(tài)組成并在這些狀態(tài)間轉(zhuǎn)換,如圖3所示。

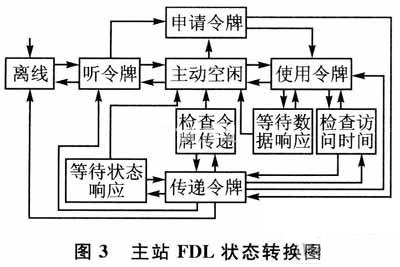

邏輯令牌環(huán)的建立主要工作是對(duì)LAS和GAPL的初始化。LAS和GAPL的具體初始化流程如圖4所示。

LAS的形成標(biāo)志著邏輯令牌環(huán)初始化的完成。接下來就是邏輯令牌環(huán)運(yùn)轉(zhuǎn)的維護(hù)階段,令牌將按照LAS進(jìn)行循環(huán)傳遞,得到令牌的主站有權(quán)進(jìn)行對(duì)其所屬?gòu)恼镜妮喸儭鬟f過程中主站將以固定的時(shí)間間隔,通過Request FDLStatus主動(dòng)幀來詢問自己GAP范圍內(nèi)的所有地址,并根據(jù)詢問結(jié)果修改LAS和GAPL。在主站活動(dòng)表生成之后,前驅(qū)站詢問ReqtJest FDL Starus,主站回復(fù)準(zhǔn)備進(jìn)入邏輯令牌環(huán),并從Listen_Token狀態(tài)進(jìn)入Active_Idle狀態(tài)(主站的前驅(qū)站會(huì)修改自己的GAP和LAS,并把該主站作為自己的后繼站)。主站在Active_Idle狀態(tài)*總線,能夠?qū)ぶ纷约旱闹鲃?dòng)幀作應(yīng)答,但沒有發(fā)起總線活動(dòng)的權(quán)力,直到前驅(qū)站傳送令牌給它,它保留令牌并進(jìn)入U(xiǎn)se_Token狀態(tài),在此狀態(tài)下驅(qū)動(dòng)Scheduler狀態(tài)機(jī)工作。主站持有令牌后,首先計(jì)算上次令牌獲得時(shí)刻到本次令牌獲得時(shí)刻經(jīng)過的時(shí)間(即實(shí)際輪轉(zhuǎn)時(shí)間tRR),并與用戶設(shè)定的目標(biāo)輪轉(zhuǎn)時(shí)間tTR比較,如果tRR小于tTR,則主站開始處理傳輸任務(wù)。首先處理高優(yōu)先級(jí)傳輸服務(wù),所有高優(yōu)先級(jí)服務(wù)處理完畢后處理低優(yōu)先級(jí)服務(wù)。在這個(gè)過程中,每一個(gè)完整的報(bào)文循環(huán)之后,主站就重新計(jì)算tTR—tTH。若結(jié)果小于0,主站進(jìn)入PassToken狀態(tài),將令牌傳遞給后繼站,未完成的任務(wù)留到下一次令牌持有的時(shí)候再執(zhí)行。所有傳輸服務(wù)都完成后,不管是否有時(shí)間剩余,主站都交出令牌。如果主站接到令牌時(shí)發(fā)現(xiàn)tTR—tTH<O,則只發(fā)送一個(gè)高優(yōu)先級(jí)報(bào)文,完成后交出令牌。主站在令牌傳遞成功后,進(jìn)入Active_Idle狀態(tài),直到再次獲得令牌。

3 系統(tǒng)工作過程

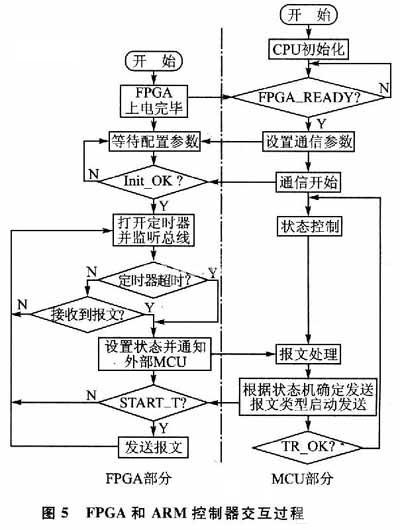

系統(tǒng)工作過程主要是ARM控制器和FPGA的通信交互過程,如圖5所示。從系統(tǒng)安全性上考慮,F(xiàn)PGA和ARM建立通信必須有雙方的確認(rèn)信號(hào),雖然Altera Cyclone系列FPGA從上電到穩(wěn)定之前引腳沒有輸出,從系統(tǒng)安全性角度考慮還是不夠的。

這里FPGA_READY信號(hào)的設(shè)計(jì)是考慮到FPGA內(nèi)部鎖相環(huán)模塊PLL穩(wěn)定工作之前需要建立時(shí)間,而其未穩(wěn)定時(shí)是不能對(duì)其進(jìn)行操作的。通信的狀態(tài)通過ARM控制器上的狀態(tài)機(jī)(FDL控制狀態(tài)機(jī)、調(diào)度狀態(tài)機(jī)和主從通信狀態(tài)機(jī))進(jìn)行轉(zhuǎn)換,根據(jù)定時(shí)要求、從站響應(yīng)幀給出的信息,以及錯(cuò)誤檢查等信息,狀態(tài)機(jī)能夠應(yīng)付一般的異常并自行恢復(fù)到正常的通信之中。

4 結(jié)論

Profibus-DP協(xié)議用任何微處理器都能實(shí)現(xiàn),只要微處理器配有內(nèi)部或外部的異步串行接口(UART),但當(dāng)數(shù)據(jù)傳輸速率較快(超過500 kb/s)時(shí),用ASIC芯片來實(shí)現(xiàn)更安全可靠。本文充分利用了FPGA實(shí)時(shí)性好和ARM核微控制器便于開發(fā)的優(yōu)點(diǎn),實(shí)現(xiàn)了Profibus-DP 1類主站,經(jīng)過搭建簡(jiǎn)單測(cè)試環(huán)境進(jìn)行測(cè)試,能和市場(chǎng)上的成品主從站建立通信連接并進(jìn)行基本的主主、主從通信。

來源:國(guó)外電子元器件

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。