一、為什么要講邊沿檢測

也許,沒有那么一本教科書,會說到這個重要的思想;也許,學了很久的你,有可能不知道這個重要的思想吧。很慚愧,我也是在當年學了1年后才領(lǐng)悟到這個思想的。

說實話,我的成長很艱辛,沒有人能給我系統(tǒng)的指導,而我得撐起這一片藍天,于是乎無數(shù)個漏洞,我一直在修補我的不足。我沒能對自己滿足過,不是 說我“貪得無厭”,而是,我不夠“完美”。人可以不完美,但不可以不追求完美;或許終點永遠達不到,但努力的過程,你一直在靠近完美;有方向感地奮斗,讓 你永遠立于不敗之地。

也許我看的書不夠多,但學校暑假那邊關(guān)于的FPGA的書,我都翻過一遍了;特權(quán)的《深入淺出玩轉(zhuǎn)FPGA》是我所看過的書中,唯一一本涉及到這個重要思想的書,也許這就是有過項目實戰(zhàn)的人出的書,和官方理論教材的區(qū)別吧。

說起邊沿檢測,還有過一個故事:

話說七哥當年,去一家FPGA公司面試。考官給他一支筆,讓他用邏輯門畫出邊沿檢測電路。話音剛落,七哥持筆揮霍,數(shù)秒鐘內(nèi)畫出了邊沿檢測的電路圖,并且給出了完美的解釋。瞬間思維的展現(xiàn)與重要應用的說明,讓考官目瞪口呆。據(jù)說,七哥贏了,這之后,七哥便被那家公司錄用了,一路牛逼,到了今天,證明了自己,取得了很大的成績。

二、什么是邊沿檢測

所謂邊沿檢測,就是檢測輸入信號,或者FPGA內(nèi)部邏輯信號的跳變,即上升沿或者下降沿的檢測。這在FPGA電路設(shè)計中相當?shù)膹V泛,幾乎我每一個稍微完善的工程都會應用到這個思想;后續(xù)章節(jié)的講解,也不少這個思維的應用。

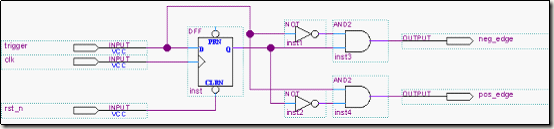

以下是七哥當年用決定自己工作的一張圖,Bingo在Quartus II Block中用邏輯門畫了出來:

如上圖5個信號:

正常工作,沒有復位的情況下,工作流程如下:

(1)D觸發(fā)器經(jīng)過時鐘clk的觸發(fā),輸出trigger信號,保存了t0時刻的信號。

(2)同時由trigger通過非門輸出信號,保留了當前時刻t1的觸發(fā)信號

(3)經(jīng)過與門輸出信號pos_edge,neg_edge

a) 只有t0時刻為高,且t1時候為低的時候,與門輸出高,此時為下降沿。

b) 只有to時候為低,且t1時候為高的時候,與門輸出高,此時為上升沿。

當然,在復位的時刻,DFF被復位,無法檢測觸發(fā)信號。

三、實現(xiàn)邊沿檢測的最優(yōu)化

1. Block或Verilog實現(xiàn)

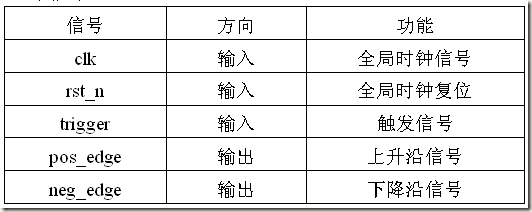

一般為了防止觸發(fā)信號的波動,加幾級觸發(fā)器,消除抖動,使得信號更穩(wěn)定。

此例程中,相對于上圖多了觸發(fā)器。其用觸發(fā)器對信號打慢兩拍,使得觸發(fā)信號然后在進行相關(guān)的處理;再來檢測邊沿的上升沿,下降沿。

(1)用Block畫圖實現(xiàn)

(2)用verilog代碼實現(xiàn)

edge_tech_design.v代碼如下所示:

/*****************************************************

* Module Name : edge_tech_design.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011-6-25

* Revision : v1.0

* Description :

*****************************************************/

module edge_tech_design

(

input clk,

input rst_n,

input trigger,

output pos_edge,

output neg_edge

);

//Capture the rising_endge & falling_edge

reg trigger_r0,trigger_r1,trigger_r2;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

trigger_r0 <= 1'b0;

trigger_r1 <= 1'b0;

trigger_r2 <= 1'b0;

end

else

begin

trigger_r0 <= trigger;

trigger_r1 <= trigger_r0;

trigger_r2 <= trigger_r1;

end

end

assign pos_edge = trigger_r1 & ~trigger_r2;

assign neg_edge = ~trigger_r1 & trigger_r2;

endmodule

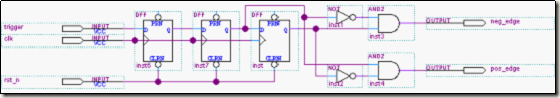

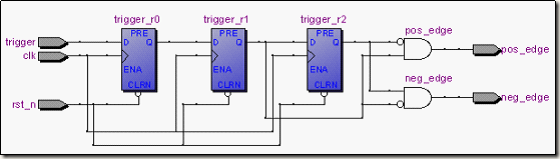

編譯后,分析Quartus II RTL圖,如下所示,與Bingo在Block用邏輯門設(shè)計的一樣,說明了代碼的正確性。

(3)Modelsim-Altera仿真圖如下所示,在上升沿(下降沿)到來的時候,時序能夠及時準確的檢測到。

2. 邊沿檢測應用

邊沿檢測技術(shù)在項目應用中,非常低廣泛。如要有效捕獲信號跳變沿,邊沿檢測技術(shù)的應用是必不可少的。Bingo大致歸納了一下,有如下幾個方面

(1)將時鐘邊沿使能轉(zhuǎn)換為邊沿檢測使能,使時鐘同步化。

(2)捕獲信號的突變(UART,SPI等信號使能突變)

(3)邏輯分析儀中信號的邊沿檢測。

3. 實現(xiàn)指標及存在缺陷

沒有十全十美的東西,也沒有十全十美的電路、代碼;本章節(jié)中所介紹的邊沿檢測技術(shù)亦如此。有如下缺陷:

(1)增大CLK信號可以增強邊沿檢測的效率,但不能濾去跳變的雜波。

(2)減少CLK可以有效濾去跳變的雜波,但不能及時檢測到邊沿跳變。

(3)增加DFF能更好的濾除雜波,寄存信號,但同時檢測延時大。