摘 要:針對主飛行顯示儀" title="主飛行顯示儀">主飛行顯示儀對圖形處理和顯示的苛刻要求,采用基于儀器總線和擴(kuò)展總線的高速陣列信號處理板的設(shè)計(jì)模式,,提出了一種基于硬件加速的PFD圖形顯示設(shè)計(jì)方法,。該方法實(shí)現(xiàn)了圖形分層" title="圖形分層">圖形分層雙緩存交替切換、圖形填充" title="圖形填充">圖形填充,、圖形合成" title="圖形合成">圖形合成和多通道DMA像素引擎,,提高了PFD圖形生成和顯示的實(shí)時(shí)性和可靠性。實(shí)踐證明,,該設(shè)計(jì)顯著解決了PFD圖形顯示系統(tǒng)中的速度瓶頸,。

關(guān)鍵詞:主飛行顯示儀 圖形分層 圖形填充 圖形合成 FPGA

主飛行顯示儀PFD(Primary Flight Display)包含了至關(guān)重要的安全飛行信息[1],它包括被安裝在與傳統(tǒng)“T”型配置的模擬儀表及相同屏幕位置上的飛行儀表,。PFD通常直接在飛行員的正前方,。隨著航空電子技術(shù)的快速發(fā)展,傳統(tǒng)的CRT顯示終端逐步被光柵式圖形顯示器LCD所替代,。然而,,光柵式圖形顯示系統(tǒng)在顯示圖形前,需要大量的各種運(yùn)算,,如圖形掃描變換,、反走樣、圖形旋轉(zhuǎn)及其他的特殊算法操作[2],。隨著顯示分辨率的提高,,要處理的像素也越來越多,而所允許的處理時(shí)間卻受屏幕刷新率所限制,。因此,,怎樣實(shí)時(shí)生成并準(zhǔn)確顯示逼真圖形畫面,是對嵌入式PFD設(shè)計(jì)者的一個(gè)極大的挑戰(zhàn),。而基于PC機(jī)的傳統(tǒng)圖形生成和圖形顯示方式,,又過于復(fù)雜且存在安全隱患,。鑒于這種情況,參考文獻(xiàn)[3-5]雖然提出了一些解決方法,,但實(shí)際效果并不是很明顯,。本文采用基于儀器總線和擴(kuò)展總線的高速陣列信號處理板的設(shè)計(jì)模式,提出了一種基于硬件加速的PFD圖形顯示設(shè)計(jì)方法,。該方法實(shí)現(xiàn)了圖形分層雙緩存交替切換,、圖形填充、圖形合成和多通道DMA像素引擎,,提高了PFD圖形生成和顯示的實(shí)時(shí)性和可靠性,。文中以Quartus Ⅱ5.0 和Modelsim_Altera 5.6e為開發(fā)、仿真和綜合的平臺(tái),,在Altera公司的Cyclone Ⅱ系列FPGA" title="FPGA">FPGA上成功下載并運(yùn)行,。

1 整體設(shè)計(jì)方案

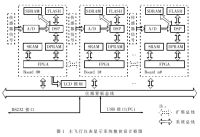

在PFD顯示系統(tǒng)中,要同時(shí)顯示多個(gè)畫面,,如姿態(tài)指引畫面,、全羅盤畫面、導(dǎo)航地圖畫面及飛行視景等,。每個(gè)畫面的處理算法都有其特殊性,,如在姿態(tài)指引畫面中,顯示畫面需要根據(jù)飛機(jī)參數(shù)的變化實(shí)時(shí)更新,,要求在地平線上填充藍(lán)色背景(藍(lán)色表示天空),,而在地平線下填充綠色(綠色表示大地)。隨著飛機(jī)姿態(tài)的變化,,地平線將在邊界線內(nèi)改變大小及方向,,畫面上的藍(lán)色和綠色區(qū)域?qū)⒅匦路峙洌@種天地區(qū)域的動(dòng)態(tài)重新填充是個(gè)非常費(fèi)時(shí)的工作,。此外,,姿態(tài)指引畫面還需要疊加一些字符(俯仰角度等),,這些字符需要隨著地平線一同旋轉(zhuǎn),。可見,,姿態(tài)指引畫面是電子主飛行儀中最為耗時(shí)的畫面之一[4],。而全羅盤畫面則側(cè)重于字符、線段的繪制和旋轉(zhuǎn)變換,,反走樣運(yùn)算任務(wù)十分繁重,。在導(dǎo)航地圖畫面生成和處理中,數(shù)據(jù)量和處理量都比較大,,如位置顯示,、飛行航跡生成等,。針對不同圖形畫面的處理算法,本文設(shè)計(jì)了大規(guī)模陣列處理機(jī)模型,,其主飛行儀表顯示系統(tǒng)整體設(shè)計(jì)框圖如圖1所示,。該設(shè)計(jì)采用共享外部總線和分布式并行處理相結(jié)合的系統(tǒng)結(jié)構(gòu)。每個(gè)處理板通過儀器背板總線互相連接,,提供了共享外部總線的結(jié)構(gòu),;而相鄰板之間也有一套擴(kuò)展總線,提供了局部共享總線的結(jié)構(gòu),。這樣,,板間既可通過背板總線直接交換數(shù)據(jù),也可以通過擴(kuò)展總線以DMA方式進(jìn)行數(shù)據(jù)傳輸,。另外,,每個(gè)板內(nèi),DSP通過局部總線連接一個(gè)容量較大的SDRAM作為全局共享外部存儲(chǔ)器,,而FPGA通過局部總線連接一個(gè)容量較小的雙口RAM作為局部共享存儲(chǔ)器,。這些全局和局部存儲(chǔ)器可以作為板間或DSP間數(shù)據(jù)交換的大型緩沖區(qū)。從圖形或圖像處理算法實(shí)現(xiàn)上考慮,,這種結(jié)構(gòu)既可滿足流水線式的并行算法,,也可以滿足分布式的并行算法(同一算法分布到多個(gè)處理器同時(shí)執(zhí)行)。

2 FPGA的設(shè)計(jì)

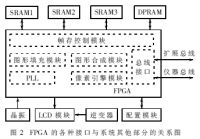

針對每塊板的不同處理功能,,對FPGA進(jìn)行了不同的算法設(shè)計(jì),。以板0#為例作一介紹。圖2為FPGA的各種接口與系統(tǒng)其他部分的關(guān)系,。

2.1 總線接口設(shè)計(jì)

系統(tǒng)有兩套總線:儀器總線和擴(kuò)展總線,。儀器總線仿VXI總線設(shè)計(jì),采用雙排歐式插座設(shè)計(jì),,模擬信號和數(shù)字信號分開在各自的插座之上,,提高了電磁兼容性。模擬部分主要包括:飛行傳感器調(diào)理信號和系統(tǒng)模擬電源,。數(shù)字部分采用基于多板分布式并行處理機(jī)制的共享式總線結(jié)構(gòu),,主要包括:24位地址總線、16位數(shù)據(jù)總線,、模塊功能選擇與控制總線,、以及時(shí)鐘和觸發(fā)信號等;擴(kuò)展總線采用基于板間流水線處理機(jī)制的鏈?zhǔn)浇Y(jié)構(gòu),,主要包括:20位地址總線,、8位數(shù)據(jù)總線和控制總線??偩€接口中,,讀寫控制,、地址譯碼、中斷及DMA控制,、時(shí)鐘和握手信號均由FPGA實(shí)現(xiàn),。限于篇幅,具體設(shè)計(jì)細(xì)節(jié)不再贅述,。

2.2 幀存控制模塊

幀存控制模塊由交叉多路轉(zhuǎn)換器Cross-MUX,、讀寫控制器和地址發(fā)生器組成。系統(tǒng)上電復(fù)位時(shí),,首先將變化頻繁,、數(shù)據(jù)量小的前景與變化緩慢或不變、數(shù)據(jù)量大的背景圖形分開存儲(chǔ)于高速SRAM中,,每3片SRAM組成全彩色(R,、G、B)圖形幀存(這樣的圖形幀存共有3組),。其中,,SRAM3為背景幀存,SRAM1和SRAM2為前景幀存,。將前景幀存設(shè)計(jì)為雙緩存輪流切換方式,,當(dāng)其中一組寫入生成圖形數(shù)據(jù)時(shí),另一組則正被讀出數(shù)據(jù)到圖形合成模塊,,圖形生成與顯示并行進(jìn)行,。

2.3 圖形合成模塊

圖形合成模塊支持一層到四層的圖形合成,通過設(shè)置合適的圖形開始點(diǎn)和結(jié)束點(diǎn)(包括豎直和水平)來完成控制,。公式(1),、(2)、(3)分別給出了其控制模型,。式中,,Plx為當(dāng)前l(fā)x層像素的灰度值,介于0~255之間,;x為層

2.4 像素引擎模塊

像素引擎模塊產(chǎn)生像素時(shí)鐘輸入信號CLK,、行同步信號/Hsync、場同步信號/Vsync,、數(shù)據(jù)使能信號/DE,、掃描方向選擇信號DPSR和R,、G,、B數(shù)據(jù)控制信號,控制LCD屏顯示全彩色圖形或圖像,。

2.5 圖形填充模塊

圖形填充算法[6]的效率高低,,直接影響到圖形顯示系統(tǒng)的加速程度,。設(shè)計(jì)高效的填充算法猶為重要。本系統(tǒng)設(shè)計(jì)了一種基于形態(tài)學(xué)膨脹算子的多種子填充算法,。膨脹算子具有天然并行運(yùn)算能力,,易于FPGA硬件實(shí)現(xiàn),并且改進(jìn)算法后,,填充速度大幅度提高,。圖形填充模塊由結(jié)構(gòu)元素生成器、膨脹處理器和位置計(jì)數(shù)器組成,。

2.5.1 結(jié)構(gòu)元素生成器

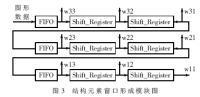

形態(tài)學(xué)圖形膨脹算法,,是用結(jié)構(gòu)元素對圖形某鄰域窗口進(jìn)行的處理[7]。本設(shè)計(jì)采用的是3×3的方形結(jié)構(gòu)元素,,每次需要讀取9個(gè)數(shù)據(jù),。為此,在FPGA內(nèi)部定義了寄存器和FIFO,,將相關(guān)的圖形灰度數(shù)據(jù)進(jìn)行存儲(chǔ),,以使其在一個(gè)時(shí)鐘周期內(nèi),以流水線的方式形成填充所需要的一個(gè)結(jié)構(gòu)元素窗口,。流水線的方式,,加快了數(shù)據(jù)處理速度。結(jié)構(gòu)元素窗口形成模塊框圖如圖3所示,。圖中,,w22為結(jié)構(gòu)元素原點(diǎn),如圖4所示,。

2.5.2 膨脹處理器

參考文獻(xiàn)[8]中膨脹處理器的設(shè)計(jì)方法是:從3×3窗口讀取的數(shù)據(jù)w11,、w12、w33…w33中,,挑出數(shù)值最大的元素并把它輸出,,采用兩兩比較排序算法,共需要12級比較,。由于多級比較器的傳輸遲滯,,最大工作頻率受到限制。本系統(tǒng)中將多種子呈多條水平線分布,,種子值為1,,待填充區(qū)域?yàn)?,結(jié)構(gòu)元素的w22在滑動(dòng)時(shí),,只與0或1比較,,比較結(jié)果若為1,則直接實(shí)現(xiàn)8鄰域填充,。這一方法簡化了比較過程,,提高了系統(tǒng)帶寬和處理速度,。在填充區(qū)域?yàn)?20×480像素時(shí),其最大工作頻率可以達(dá)到80.12MHz(而參考文獻(xiàn)[8]在填充區(qū)域?yàn)?20×120像素時(shí),,其最大工作頻率為62.751MHz),,加速效果比較明顯。

2.5.3 位置計(jì)數(shù)器

位置計(jì)數(shù)器根據(jù)行,、列位置標(biāo)志來確定滑動(dòng)窗口(結(jié)構(gòu)元素)在圖形數(shù)據(jù)陣列中的位置,。圖形邊界根據(jù)位置計(jì)數(shù)器的值查表得到,邊界判斷比較迅速,。

圖形填充模塊的狀態(tài)遷移圖如圖5所示,。本設(shè)計(jì)根據(jù)需要設(shè)定了六個(gè)狀態(tài):Idle、ReadFIFO,、Comp,、WriteRAM、Boundary,、Bd_P,。這六個(gè)狀態(tài)根據(jù)窗口位置是否有種子而進(jìn)行轉(zhuǎn)換,從而完成圖形填充,。

以上描述中,,結(jié)構(gòu)元素與種子比較、像素點(diǎn)的填充,、邊界判斷等內(nèi)容可有多種表達(dá)算法,,特別是種子預(yù)置、邊界判斷和邊界填充,,有待進(jìn)一步研究,。

3 仿真及實(shí)驗(yàn)結(jié)果

圖6是仿真和實(shí)驗(yàn)結(jié)果。圖6(a)是圖形分層雙緩存交替切換,、圖形填充,、圖形合成和多通道DMA像素引擎的時(shí)序仿真圖;圖6(b)是實(shí)驗(yàn)結(jié)果圖,。對800×600的屏,,刷新率可達(dá)47.6Hz,即21ms/幀,;對320×480的區(qū)域,,填充一次約花費(fèi)2.86ms。

本文提出的基于儀器總線和擴(kuò)展總線的高速陣列信號處理板的整體設(shè)計(jì)模式,,具有較強(qiáng)的圖形處理和數(shù)據(jù)吞吐能力,。基于硬件加速的PFD圖形顯示設(shè)計(jì),提高了PFD圖形生成和顯示的實(shí)時(shí)性及可靠性,,也顯著提高了圖形質(zhì)量,使顯示畫面更加逼真,。經(jīng)設(shè)計(jì)和部分調(diào)試表明:該方案具有較好的工程實(shí)用性和易擴(kuò)展性,。

參考文獻(xiàn)

[1] CAMPBELL C B.Advanced integrated general aviation primary flight display user interfaced design,development and assessment.Digital Avionics Systems Conference,,2002,,21:1045-1-10A5-12.

[2] PAETH A.A Fast algorithm for general raster rotation.Graphics Interface,1986,,(5):77-81.

[3] READ B C.Developing the next generation cockpit display system.IEEE,,1996.

[4] HANDLEY S J,ALLERTON D J.The designed of an EFIS attitude indicator for a flight simulator[A].ICA-S[C],, 1994:282-292.

[5] ZHU Yaodong Dong,,ZHANG Huanchun,JING Yazhi.A new design method of combined graphics display system in

aircraft cockpit[J].Journal of Nanjing University of Aeronautics & Astronautics,,2002.

[6] ROGERS D F.Procedural elements for computer graphics(Second Edition).Beijing:China Machine Press,,2002:82-119.

[7] GONZALEZ R C,RICHARD E.Woods digital image processing(Second Edition).Beijing:Publishing House of Elec- tronics Industry,,2005:420-450.

[8] 李雷鳴.基于DSP和FGPA的全姿態(tài)指示器填充算法研究及硬件實(shí)現(xiàn)技術(shù).碩士學(xué)位論文.南京:南京航空航天大學(xué),,2004: 29-43.