基于SOPC的扭振信號測量系統(tǒng)實現(xiàn)研究

電子科技 楊懌菲 唐小華 王花朋

摘要: 利用SOPC技術(shù)實現(xiàn)的軸系扭振監(jiān)測系統(tǒng),與以往的數(shù)字式扭振監(jiān)測技術(shù)相比,由于采用了軟硬件協(xié)同設(shè)計,從而大大節(jié)省了軟硬件成本,縮短了開發(fā)周期;NIOS軟核的利用使監(jiān)測系統(tǒng)擁有了強(qiáng)大的運(yùn)算能力,數(shù)據(jù)的傳輸速度也有較大提升。基于SOPC技術(shù)的扭振監(jiān)測信號動態(tài)分析范圍較大,可以在高低轉(zhuǎn)速的軸系之間快速切換,若與數(shù)據(jù)庫技術(shù)結(jié)合,則可以實現(xiàn)檢測、分析和監(jiān)控告警一體化。同時這種監(jiān)測系統(tǒng)也適用于各種回轉(zhuǎn)軸系系統(tǒng),如內(nèi)燃機(jī)曲軸、發(fā)電機(jī)、齒輪傳動鏈等,具有廣闊的應(yīng)用前景。

Abstract:

Key words :

扭振(即扭轉(zhuǎn)振動)廣泛存在于各種回轉(zhuǎn)軸系中,如內(nèi)燃機(jī)曲軸、發(fā)電機(jī)、齒輪傳動鏈等。就內(nèi)燃機(jī)軸系而言,嚴(yán)重的扭振會導(dǎo)致動力裝置的部件斷裂,造成不可估計的財產(chǎn)損失和人員傷亡。因此對扭振的動態(tài)測量和監(jiān)控一直為人們所重視。

目前按照對扭振信號的提取方式,扭振測量可以分為模擬式、數(shù)字式和軟件式。數(shù)字式扭振監(jiān)測應(yīng)用較為廣泛。這一類儀器測量精度較高,信號采集主要用單片機(jī)或單片機(jī)及CPLD。單片機(jī)采集信號速度低且系統(tǒng)實時性較差;用單片機(jī)結(jié)合CPLD實現(xiàn),系統(tǒng)可擴(kuò)展性不好,一旦硬件做成很難改動,另外可編程器件與單片機(jī)接口的速率匹配也是一個瓶頸問題。

SOPC(System On Programmble Chip)是Altera公司提出的片上可編程系統(tǒng)解決方案。它將CPU、存儲器、I/0接口、DSP模塊、低電壓差分信號(LVDS)技術(shù)、時鐘數(shù)據(jù)恢復(fù)技術(shù)(CDR)以及鎖相環(huán)(PLL)等系統(tǒng)設(shè)計所必需的模塊集成到一片F(xiàn)PGA上,構(gòu)成一個可編程的片上系統(tǒng),使所設(shè)計的電路在其規(guī)模、可靠性、體積、功耗、上市周期、開發(fā)成本、產(chǎn)品維護(hù)及硬件升級等多方面實現(xiàn)最優(yōu)化。用SOPC技術(shù)實現(xiàn)扭振信號監(jiān)測,在測量精度、數(shù)據(jù)傳輸及計算、系統(tǒng)擴(kuò)展等方面都有很大優(yōu)勢。

1 扭振監(jiān)測原理及方法

軸系在旋轉(zhuǎn)時若沒有扭振,則軸的各瞬時速度都等于其平均速度,軸上的齒輪盤也是勻速轉(zhuǎn)動,且傳感器輸出的每齒一個脈沖信號的重復(fù)周期是相同的。當(dāng)軸系發(fā)生扭振時,相當(dāng)于在軸系平均速度上疊加了一個扭振的波動,于是傳感器輸出的脈沖序列就不再是均勻間隔了,而是一個載波頻率被扭振信號調(diào)制的調(diào)頻信號。這個調(diào)頻信號可以用脈沖記數(shù)法進(jìn)行解調(diào)。設(shè)軸系旋轉(zhuǎn)一周的時間為tc,則平均速度為 齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

因此只要測出tn和tc就可算出相應(yīng)各£。的扭角θn。

信號的拾取可采用光電編碼器。光電編碼器由光柵盤和光電檢測裝置組成,光柵盤是在一定直徑的圓板上等分地開通若干個長方形孔。將光電編碼器的光柵碼盤安裝在轉(zhuǎn)軸上,且與轉(zhuǎn)軸同心,當(dāng)軸系轉(zhuǎn)動時光柵盤與軸同速旋轉(zhuǎn),經(jīng)發(fā)光二極管等電子元件組成的檢測裝置輸出若干脈沖信號,對脈沖信號計數(shù),并通過計算就可得出θn。

2 扭振信號監(jiān)測系統(tǒng)的設(shè)計及實現(xiàn)

2.1 系統(tǒng)結(jié)構(gòu)及板級硬件設(shè)計

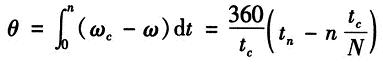

扭振信號測監(jiān)系統(tǒng)的總體結(jié)構(gòu),如圖1所示。

系統(tǒng)設(shè)計采用Altera公司的新一代低成本FPGA—CycloneⅡ系列的EP2C35實現(xiàn)SOPC系統(tǒng)設(shè)計。系統(tǒng)硬件主要包括FPGA上的NiosⅡ處理器系統(tǒng)、FPGA外的接口和外設(shè)兩部分。NiosⅡ處理器系統(tǒng)由基于Avalon Bus的NiosⅡCPU、串行接口、PIO、PIO控制器、存儲器控制器、定時器以及片上RAM等IP組成。

外設(shè)包括:信號拾取整形模塊、USB—Blaster-模塊、Flash、SDRAM、LCD模塊、電源模塊、鍵盤等。信號由光電編碼器拾取后經(jīng)整形模塊進(jìn)入NiosⅡ處理器,Clock(系統(tǒng)時鐘)模塊提供50 MHz有源時鐘和用戶自定義的外部時鐘。上位PC用軟件接收RS232發(fā)送的連續(xù)采樣數(shù)據(jù),根據(jù)規(guī)定好的協(xié)議,解碼出需求的數(shù)據(jù)進(jìn)行分析。4個按鍵開關(guān)和PS/2,用于控制信號采樣和數(shù)據(jù)發(fā)送,滿足用戶多種控制要求。系統(tǒng)通過PIO可實現(xiàn)對整形模塊、鍵盤、LCD等外設(shè)的控制。存儲器控制器分別與片外Flash和SDRAM連接,實現(xiàn)對存儲器的訪問。

2.2 系統(tǒng)硬件定制

2.2.1 FPGA硬件模塊設(shè)計

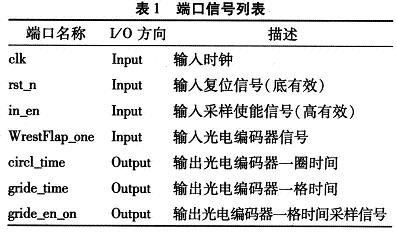

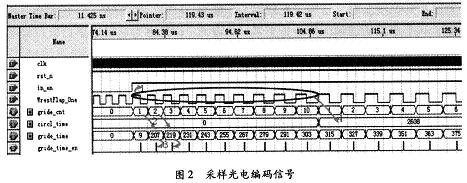

硬件電路板測試完成后,需要設(shè)計FPGA硬件模塊實現(xiàn)數(shù)據(jù)采集。模塊各端口列表,如表1所示,信號采集仿真波形,如圖2所示。輸出信號中所有光電編碼器時間是系統(tǒng)時鐘個數(shù)的計數(shù)值。最后通過軟件模塊計算得到平均扭角、瞬時扭角以及誤差。

如圖2所示,當(dāng)in_en高有效時,在WrestFlap_one上升沿,寄存器gride_cnt加l,同時gride_time,circl_time開始計算。當(dāng)下一個WrestFlap_one上升沿時,寄存器gride_cnt加1,直加到一圈格數(shù),然后又重新開始重復(fù)的計算。同時當(dāng)下一個WrestFlap_one上升沿時gride_time輸出計算了上一圈的光電編碼器一格時間。當(dāng)gride_cnt一圈數(shù)完時,circl_time輸出上一圈的總時間。在WrestFlap_one下降沿,gride_en輸出使能采樣信號,高有效,此信號做為后端FIFO寫使能信號。(圖中橢圓區(qū)域為一圈光電編碼信號的輸出,仿真中規(guī)定一圈有10格,第1格對應(yīng)的gride_time是207,第2格對應(yīng)的gride_time是219…。)

2.2.2 SOPC硬件模塊加載及系統(tǒng)構(gòu)成

在SOPC Builder中進(jìn)行扭振測量系統(tǒng)配制。添加Ahera自有的豐富IP核,選擇SOPC Builder生成HDL代碼的類型為Verilog,選擇芯片EP2C35,確定系統(tǒng)工作頻率,配制處理器選項,定義處理器地址,配制外圍設(shè)備,安排存儲器地址和范圍,為外圍設(shè)備和接口設(shè)置所需的中斷優(yōu)先級。同時為優(yōu)化硬件設(shè)計,系統(tǒng)設(shè)計了用戶自定義外設(shè)模塊。SOPC Build所用模塊如下:

(1)NIOS II Processor CPU;

(2)tri_state_bridge(Avalon連接總線);

(3)lcd_16207_0(LCD顯示);

(4)sdram,cfi_flash(存儲器);

(5)button_pio,switch_pio(輸入控制端口);

(6)Dma(傳輸控制)。

2.2.3 用戶自定義外設(shè)設(shè)計

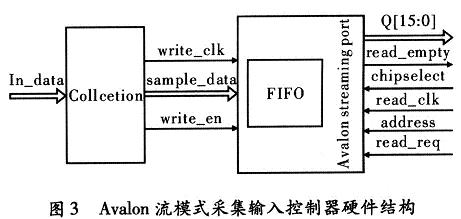

系統(tǒng)設(shè)計自定義模塊是Avalon流模式采集輸入控制器。該控制器設(shè)計符合Avalon總線規(guī)范,功能是將采集的數(shù)據(jù)完整送入SDRAM以便存儲以及方便數(shù)據(jù)處理。系統(tǒng)CPU速率為50 MHz,而采樣速率不定,因此需要FIFO實現(xiàn)前后傳輸?shù)倪B貫性。然后經(jīng)過DMA傳輸通道將數(shù)據(jù)存入SDRAM。Avalon流模式采集輸入控制器硬件結(jié)構(gòu),控制器模塊分為采集模塊和HFO傳輸模塊兩部分。采集模塊實現(xiàn)數(shù)據(jù)的采集,其輸入接口有:write_clk(寫時鐘)、write_en(寫使能)與sample_data(16位數(shù)據(jù)總線)。掛在Avalon總線上的接口有FIFO Q[15:0](數(shù)據(jù)輸出總線)、chipselect(片選信號)、read_req(讀請求信號)、address(Avalon總線地址)read_empty(讀空信號)、read_clk(讀時鐘)。

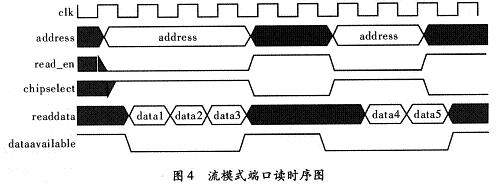

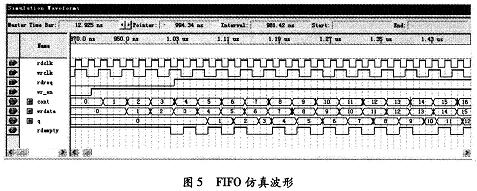

設(shè)計使用光電編碼每格有效信號作為寫使能控制向FIFO寫數(shù)據(jù),讀請求信號read_req由總線發(fā)出,經(jīng)read_empty控制DMA取FIFO中數(shù)據(jù)的時間,在read_empty低電平期間(即FIFO不空)取FIFO中數(shù)據(jù)。其時序見圖4,其中Dataavailable信號接FIFO輸出的空信號(read_empty)。仿真波形,如圖5所示。

設(shè)計完成后啟動SOPC Builder的Generate生成用于綜合和仿真的文件,最后在QuarusⅡ中鎖定端口引腳,對生成的處理器系統(tǒng)進(jìn)行仿真、綜合、適配并下載到FPGA中。

2.3 系統(tǒng)軟件設(shè)計

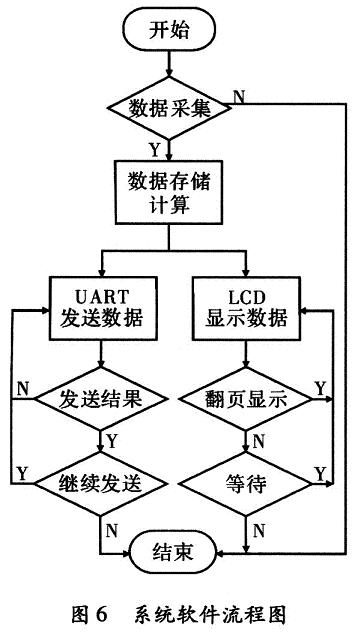

系統(tǒng)軟件共有數(shù)據(jù)采集模塊、數(shù)據(jù)存儲計算模塊、UART數(shù)據(jù)發(fā)送控制模塊和LCD顯示控制模塊。系統(tǒng)軟件流程圖,如圖6所示,數(shù)據(jù)采集模塊有開關(guān)使能。當(dāng)開關(guān)鍵有效且處于有效采樣信號下時,系統(tǒng)開始接收由光電編碼器經(jīng)整形電路采集到的脈沖信號,每次采樣信號有效時,采樣次數(shù)加一,系統(tǒng)共可采集8 000格數(shù)據(jù)。

數(shù)據(jù)存儲計算模塊根據(jù)采集到的數(shù)據(jù)計算出瞬時扭角,平均扭角和誤差。同時數(shù)據(jù)發(fā)送模塊通過按鍵組控制向上位PC機(jī)發(fā)送這3種數(shù)據(jù),并由LCD控制模塊以二行形式顯示,通過按鍵控制進(jìn)行刷新顯示。

3 結(jié)束語

利用SOPC技術(shù)實現(xiàn)的軸系扭振監(jiān)測系統(tǒng),與以往的數(shù)字式扭振監(jiān)測技術(shù)相比,由于采用了軟硬件協(xié)同設(shè)計,從而大大節(jié)省了軟硬件成本,縮短了開發(fā)周期;NIOS軟核的利用使監(jiān)測系統(tǒng)擁有了強(qiáng)大的運(yùn)算能力,數(shù)據(jù)的傳輸速度也有較大提升。基于SOPC技術(shù)的扭振監(jiān)測信號動態(tài)分析范圍較大,可以在高低轉(zhuǎn)速的軸系之間快速切換,若與數(shù)據(jù)庫技術(shù)結(jié)合,則可以實現(xiàn)檢測、分析和監(jiān)控告警一體化。同時這種監(jiān)測系統(tǒng)也適用于各種回轉(zhuǎn)軸系系統(tǒng),如內(nèi)燃機(jī)曲軸、發(fā)電機(jī)、齒輪傳動鏈等,具有廣闊的應(yīng)用前景。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。