1 引言

波形發(fā)生器已經(jīng)廣泛的應(yīng)用在通信、控制、測量等各個(gè)領(lǐng)域,如鋸齒波、正弦波、方波等波形常用于電路的設(shè)計(jì)與調(diào)試。隨著電子技術(shù)的迅猛發(fā)展,數(shù)字化正逐漸地成為電子產(chǎn)業(yè)的發(fā)展趨勢,各公司都將自己的產(chǎn)品向數(shù)字化、集成化、小型化等方向進(jìn)行拓展。眾所周知,數(shù)字化的電子產(chǎn)品有其不可替代的優(yōu)勢,譬如體積小、集成程度高、抗干擾能力強(qiáng)等特點(diǎn)。但是,數(shù)字電路只能夠較好地處理脈沖波形,即只對l和0形成的方波處理得很好.對于連續(xù)漸變的信號(hào)不能夠很好地處理,而這恰恰正是模擬電路的優(yōu)勢所在。本文將數(shù)字電路與模擬電路相結(jié)合,即通過FPGA來產(chǎn)生所需各種模擬波形的控制信號(hào),然后通過模擬電路來處理漸變信號(hào),這樣町以得到各種清晰的波形。

2 示波器顯示原理

首先,對示波器的顯示原理進(jìn)行簡要地說明,以便更好地了解硬件電路的工作過程。在整個(gè)顯示期間,示波器需要始終處于“X-Y”檔,即爾波器的波形是 X軸和Y軸輸入信號(hào)的疊加合成顯示。可知,一般情況下,x軸輸入的變量為信號(hào)頻率,Y軸輸入的變量為信號(hào)幅度。因此,當(dāng)在x軸上輸入5KHz的信號(hào)頻率值,在Y軸上輸入0V的直流電壓幅度時(shí),在示波器位于(5KHz,0V)的位置處就會(huì)顯示出一個(gè)亮點(diǎn);同理,若在Y軸上輸入5V的直流電壓幅度,而在x軸上輸入0Hz的信號(hào)頻率值時(shí),在示波器位于(0Hz,5V)的位置處也會(huì)顯示出一個(gè)亮點(diǎn);而如果在x軸和Y軸上的輸入分別為5KHz、5V時(shí),則亮點(diǎn)就會(huì)出現(xiàn)在示波器上的(5KHz,5V)處。這樣,如果通過程序不間斷地對兩個(gè)坐標(biāo)軸進(jìn)行賦值,就可以在示波器上顯示出一條清晰.連續(xù)的信號(hào)波形。

3 硬件設(shè)計(jì)

本文主要詳細(xì)地介紹了常用信號(hào)中階梯波和鋸齒波的模擬波形設(shè)計(jì),它們的模擬電路實(shí)現(xiàn)簡單,并且實(shí)際的輸出波形清晰。方案中的硬件電路主要是南DSP、 FPGA以及外圍芯片構(gòu)成,DSP用于控制模擬波形的輸出位置和幅度;外圍芯片用來進(jìn)行模擬波形的產(chǎn)生,如利用兩個(gè)DAC0832來產(chǎn)生兩路電壓信號(hào),一個(gè)用于控制鋸齒波的高度,另一個(gè)用于控制階梯波的高度。而FPGA則進(jìn)行所需的各種控制信號(hào)的邏輯編程。

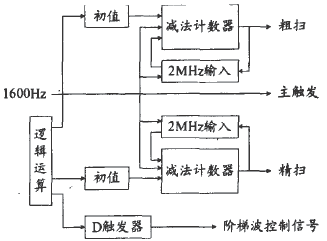

這里,F(xiàn)PGA采用的是ALTERA公司的10K10系列的可編程邏輯器件。ALTERA公司的FLEX 10K系列器件是業(yè)界第一塊嵌入式可編程邏輯器件,為柔性邏輯元素陣列架構(gòu),利用通用的門海架構(gòu)來實(shí)現(xiàn)一般性的邏輯功能,還采用專用的硅片來實(shí)現(xiàn)規(guī)模較大的專用功能。和標(biāo)準(zhǔn)的門陣列比較,由于嵌入式功能在硅片上實(shí)現(xiàn),所需的硅片面積更小、系統(tǒng)速度更高。FLEX 10K系列不僅能提供高密度、高速度和系統(tǒng)集成功能,并且在單個(gè)器件內(nèi)部包含多重32比特總線、6144比特的RAM空間,還支持串行與并行兩種配置方式及JTAG模式的在線仿真,這些特點(diǎn)都使得FLEX IOK系列器件成為目前應(yīng)用最為廣泛的可編程邏輯器件之一。與之對應(yīng),采用的開發(fā)工具是MaxplusⅡ可編程邏輯開發(fā)軟件,利用MaxplusⅡ作為 EDA的軟件工具,可實(shí)現(xiàn)強(qiáng)大的邏輯功能,還具有周期短、集成度高、價(jià)格合適等優(yōu)點(diǎn)。并且,由于電路的邏輯模塊都是在FPGA中實(shí)現(xiàn)的,因此,它們具有良好的可移植性和易維護(hù)性等特點(diǎn),并方便以后系統(tǒng)的改進(jìn)。同時(shí),這也進(jìn)一步地減少了電路板面積,使電路的集成度大大地提高。在本設(shè)計(jì)方案中,主要是使用 FPGA來進(jìn)行各種模擬波形的控制編程,產(chǎn)生各種邏輯用以作為其控制信號(hào)。其中,F(xiàn)PGA中邏輯控制的結(jié)構(gòu)框圖如圖1所示,可分為三個(gè)部分,而粗掃、精掃信號(hào)是作為鋸齒波的控制信號(hào)。

圖1 FPGA中控制信號(hào)模塊功能框圖

FPGA的工作過程為:首先,對輸入的32KHz時(shí)鐘信號(hào)以計(jì)數(shù)器進(jìn)行分頻,產(chǎn)生一個(gè)1600Hz的窄脈沖信號(hào),它一方面作為外部模擬波形產(chǎn)生電路的掃描觸發(fā)信號(hào),另一方面作為鋸齒波控制信號(hào)的工作起始信號(hào),即該信號(hào)每到來一次,就啟動(dòng)其它功能模塊,按照需要的時(shí)序產(chǎn)生所需的控制信號(hào)。由圖1可知,1600Hz頻率到來,會(huì)打開精掃計(jì)數(shù)器與粗掃計(jì)數(shù)器的輸入時(shí)鐘(2MHz),并啟動(dòng)二者的初始裝載過程,然后以這個(gè)初始值對輸入脈沖進(jìn)行減法計(jì)數(shù),當(dāng)減法溢出時(shí),輸出端就會(huì)產(chǎn)生所需的掃描信號(hào)。同時(shí),還要利用該信號(hào)關(guān)閉各自的輸入時(shí)鐘信號(hào),直到下一個(gè)1600Hz的到來。當(dāng)經(jīng)過邏輯運(yùn)算改變減法計(jì)數(shù)器的8位初始值時(shí),輸出信號(hào)的時(shí)刻相對于1600Hz信號(hào)來講,就會(huì)有相應(yīng)的變化。通過這種邏輯方式,就可以控制各種模擬波形的出現(xiàn)時(shí)間,從而能夠控制示波器上各種波形的顯示位置。其中,減法計(jì)數(shù)器初值的改變是通過一個(gè)8位鎖存器來實(shí)現(xiàn),即將DSP的地址線、讀/寫信號(hào)線及I/O空間的訪問控制線進(jìn)行邏輯運(yùn)算,作為8位鎖存器的選通信號(hào),然后利用程序?qū)?位數(shù)據(jù)寫入減法計(jì)數(shù)器。

而階梯波控制信號(hào)則是完全由軟件程序來實(shí)現(xiàn),即根據(jù)其各種時(shí)序,在不同的時(shí)刻將不同的數(shù)據(jù)寫入FPGA中進(jìn)行鎖存,然后經(jīng)由D觸發(fā)器輸出用以控制信號(hào)的產(chǎn)生。為了滿足系統(tǒng)的需要,還設(shè)計(jì)了一個(gè)控制波形寬度變化的邏輯用以產(chǎn)生顯示所需的不同寬度的脈沖序列,其T.作方式是將兩個(gè)不同頻率的方波信號(hào)和一個(gè)D觸發(fā)器的輸出端D與,D分別作邏輯與操作,然后再進(jìn)行邏輯或運(yùn)算,再通過程序來改變D觸發(fā)器的輸出狀態(tài),從而得列具有兩種寬度的輸出脈沖。

4 實(shí)驗(yàn)結(jié)果

4.1階梯波波形

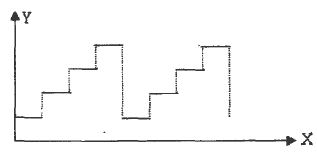

這里,簡要地介紹一下階梯波波形的具體產(chǎn)生過程。首先,需要設(shè)計(jì)一個(gè)可產(chǎn)生4種不同直流電壓的模擬電路,使其能夠在不同的控制信號(hào)組合狀態(tài)下,會(huì)輸出不同幅度的直流電壓。該模擬電路總共有4個(gè)控制信號(hào)輸入端,通過DSP的軟件程序控制組合的輸入。當(dāng)組合狀態(tài)為“0001”時(shí),電路會(huì)輸出幅度為4V的直流電壓,而當(dāng)組合狀態(tài)為“0010”時(shí),電路將輸出幅度為5v的直流電壓。同時(shí),還要給出其塒應(yīng)的輸出位置。這樣.當(dāng)程序循環(huán)改變輸入的組合狀態(tài)時(shí),在雙蹤顯示模式下,就可以得到如圖2所示的階梯波波形,將這一波形輸入到示波器的x軸上,就會(huì)在示波器的相應(yīng)位置上出現(xiàn)四個(gè)亮點(diǎn)。

圖2階梯波波形

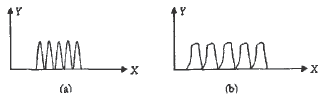

在實(shí)際工程中,通過DSP程序在FPGA中進(jìn)行兩種不間脈沖寬度之間的轉(zhuǎn)換,將所需脈沖寬度的信號(hào)經(jīng)過外部的單穩(wěn)態(tài)觸發(fā)器設(shè)置適當(dāng)?shù)膶挾龋俳?jīng)過微分、積分電路中,就會(huì)形成如圖3所示的波形,把這一波形輸入到示波器的Y軸上,并將其設(shè)置為“X-Y”檔,最后就會(huì)顯示出四條亮線。當(dāng)圖(a)中的較窄脈沖輸入到Y(jié)軸時(shí),通過程序使其在不同的幅值點(diǎn)的停留時(shí)間基本保持一致,這樣,它所對應(yīng)的顯示亮線會(huì)比較均勻;而當(dāng)圖 (b)中的較寬脈沖輸入到Y(jié)軸時(shí),通過程序使其在最高幅值點(diǎn)處停留的時(shí)間比在其它幅值點(diǎn)停留的時(shí)間長,這使得它所對應(yīng)的亮線頂部比亮線的其它部分較亮,最后就會(huì)在示波器上顯示出形狀類似火柴頭的亮線圖形。

圖3兩種寬度在脈沖信號(hào)

4.2鋸齒波波形

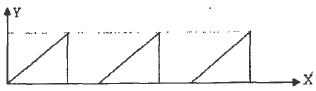

同樣地,按照相間的構(gòu)想就可以產(chǎn)生鋸齒波波形。由上可知,F(xiàn)PGA會(huì)輸出1600Hz的脈沖作為外部模擬電路的觸發(fā)信號(hào),在它的作用下,模擬電路會(huì)產(chǎn)生一個(gè)長為100us的掃描信號(hào),將其作為示波器上X軸的輸入信號(hào),而將0V的直流電壓輸入Y軸。那么,根據(jù)示波器的顯示原理,由于Y軸的輸人為0V,則亮點(diǎn)只能出現(xiàn)在x軸上,而x軸的輸入信號(hào)又是一個(gè)頻率值固定的連續(xù)信號(hào),這樣在示波器上就會(huì)顯示出一個(gè)在x軸上連續(xù)的扣描基線的波形。然后,通過DSP 的軟件程序控制模擬電路,產(chǎn)生連續(xù)變化的直流電壓值,再輸出到示波器的Y軸上時(shí),就可以在示波器上得到鋸齒波波形,如圖4所示。

圖4鋸齒波波形

5 結(jié)論

這里,利用FPGA構(gòu)成核心控制電路用以產(chǎn)生模擬波形的控制信號(hào),再輔以外圍的電路生成鋸齒波和階梯波。通過實(shí)驗(yàn)觀察,產(chǎn)生的波形清晰,無雜波干擾.表明該模擬電路能夠很好地處理漸變信號(hào),充分地體現(xiàn)了模擬電路的優(yōu)點(diǎn)。并且,在實(shí)際工程中,合理地運(yùn)用鋸齒波和階梯波來生成項(xiàng)目所需的各種模擬波形。只要將部分電路稍加改造,就可以應(yīng)用于其他應(yīng)用系統(tǒng)中。