1 引言

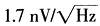

隨著微電子技術(shù)的發(fā)展,寬帶放大器在科研中具有重要作用。寬帶運(yùn)算放大器廣泛應(yīng)用于A/D轉(zhuǎn)換器、D/A 轉(zhuǎn)換器、有源濾波器、波形發(fā)生器、視頻放大器等電路。這些電路要求運(yùn)算放大器具有較高的頻帶寬度,電壓增值。為此,以可編程增益放大器THS7001和可變?cè)鲆娣糯笃?a class="innerlink" href="http://forexkbc.com/tags/AD603" title="AD603" target="_blank">AD603為核心,設(shè)計(jì)一種可編程寬帶運(yùn)算放大器。該電路增益調(diào)節(jié)范圍為-6~70 dB,步進(jìn)間距為6dB,AGC為60 dB,-3 dB通頻帶為40 Hz~15MHz。矩陣鍵盤設(shè)置增益值、步進(jìn),點(diǎn)陣液晶顯示實(shí)時(shí)電壓有效值,人機(jī)界面友好,操作簡單方便。

2 系統(tǒng)總體設(shè)計(jì)方案

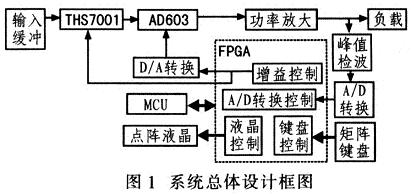

該系統(tǒng)主要由可控增益放大器、功率放大與峰值檢波、單片機(jī)顯示和控制3大模塊組成。其中可變?cè)鲆娣糯笃饕訲HS7001和AD603為核心。單片機(jī)控制THS7001實(shí)現(xiàn)增益粗調(diào),并通過D/A轉(zhuǎn)換控制AD603實(shí)現(xiàn)增益細(xì)調(diào),從而使總增益在- 6~70 dB的寬頻帶范圍內(nèi)線性變化。前置放大器采用由寬帶電壓型反饋運(yùn)放THS4011構(gòu)成的射極跟隨器,可有效提高輸入電阻;后級(jí)功率放大器采用電流型反饋運(yùn)放AD811,提高系統(tǒng)帶負(fù)載能力。由二極管峰值檢波電路測量峰值,并通過A/D轉(zhuǎn)換、D/A轉(zhuǎn)換實(shí)現(xiàn)自動(dòng)增益控制。通過鍵盤手動(dòng)預(yù)置增益值,LCD實(shí)時(shí)顯示預(yù)置增益值并輸出有效值。其系統(tǒng)總體設(shè)計(jì)框圖如圖1所示。

3 器件選型及理論分析

3.1 輸入級(jí)電路運(yùn)放選型

由于該電路噪聲主要取決于第一級(jí)放大器。所以選擇第一級(jí)運(yùn)放成為決定噪聲大小的關(guān)鍵。電壓反饋型(VFB)運(yùn)算放大器具有同相和反向輸人端阻抗基本相同(均為高阻),低噪聲,更好的直流特性,增益帶寬積為常數(shù)。反饋電阻的取值自由等特點(diǎn):而電流反饋型(CFB)運(yùn)算放大器則具有同相輸入端為高阻阻,反向輸入端為低阻抗,帶寬不受增益影響,壓擺率更快,反饋電阻的取值有限制等特點(diǎn)。由此看出,CFB放大器適用于那些需要壓擺率快、低失真和可設(shè)置增益而不影響帶寬的電路;而VFB放大器則適用于那些需要低調(diào)電壓、低噪聲的電路。因此選用電壓反饋型運(yùn)放THS4011作為前級(jí)輸入。THS4011是一款高速低噪聲運(yùn)算放大器,其帶寬為290 MHz,壓擺率為310 V/μs,輸入噪聲為 。

。

4.2 峰值檢波電路

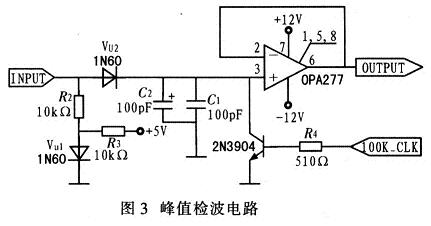

峰值檢波電路由二極管電路和電壓跟隨器組成。其工作原理:當(dāng)輸入電壓正半周通過時(shí),檢波管 VU2導(dǎo)通,對(duì)電容C1、C2充電,直到到達(dá)峰值。三極管的基極由FPGA控制,產(chǎn)生1Oμs的高電平使電容放電,以減少前一頻率測量對(duì)后一頻率測量的影響,提高幅值測量精度。其中Vu1為常導(dǎo)通,以補(bǔ)償VU2上造成的壓降。適當(dāng)選擇電容值,使得電容放電速度大于充電速度,這樣電容兩端的電壓可保持在最大電壓處,從而實(shí)現(xiàn)峰值檢波。

該電路能夠檢測寬范圍信號(hào)頻率,較低的被測信號(hào)頻率,檢波紋波較大,但通過增加小電容和大電容并聯(lián)構(gòu)成的電容池可濾除紋波。而后級(jí)隔離,則增加由OPA277構(gòu)成的射極跟隨器,如圖3所示。

5 系統(tǒng)軟件設(shè)計(jì)

5.1 程序部分設(shè)計(jì)

系統(tǒng)軟件設(shè)計(jì)遵循結(jié)構(gòu)化和層次化原則,由一個(gè)主程序及若干子程序構(gòu)成。主程序通過調(diào)用子程序控制子程序間的時(shí)序,從而使整個(gè)程序正常運(yùn)行。系統(tǒng)軟件設(shè)計(jì)部分由單片機(jī)和FPGA組成。單片機(jī)主要完成讀取鍵值、控制增益和顯示功能。而FPGA則作為總線控制器,管理鍵盤、液晶和A/D轉(zhuǎn)換器與單片機(jī)之間的數(shù)據(jù)交換。以O(shè)uartus II 7.2為設(shè)計(jì)環(huán)境,用Verilog HDL硬件描述語言編程,完成各功能模塊的設(shè)計(jì),并仿真測試設(shè)計(jì)好的各個(gè)模塊,再將各個(gè)模塊相互連接。程序以按鍵中斷為主線,以各項(xiàng)功能為分支,圖4為程序流程。

5.2 FPGA部分設(shè)計(jì)

FPGA主要完成A/D、D/A轉(zhuǎn)換器的串并轉(zhuǎn)換。采用12位D/A轉(zhuǎn)換器TLV5618,該器件是串行接口,大大節(jié)約系統(tǒng)端口資源,但MCU的P0、 P2端口是并行口,與串行器件的時(shí)序匹配較復(fù)雜,用靜態(tài)口P1端口模擬串行口時(shí)序又會(huì)占用MCU很多處理時(shí)間,影響系統(tǒng)效率。

為使MCU對(duì)串行器件操作簡單,把串行時(shí)序在FPGA中用狀態(tài)機(jī)描述,同時(shí)該控制狀態(tài)機(jī)又對(duì)MCU提供P0口、CS、WR的微機(jī)標(biāo)準(zhǔn)時(shí)序接口形式,這樣MCU只需選中相應(yīng)地址,就可寫入所要得到的電壓數(shù)據(jù),狀態(tài)機(jī)會(huì)完成串并轉(zhuǎn)換。

以串行接口時(shí)序?qū)?shù)據(jù)寫入器件并鎖存,與寫IO端口操作一樣簡單方便,而D/A轉(zhuǎn)換器模塊的輸出端既可得到相應(yīng)輸出電壓,又達(dá)到控制增益的目的。

AGC部分采用循環(huán)結(jié)構(gòu),將A/D轉(zhuǎn)換采樣得到的數(shù)據(jù)與預(yù)設(shè)值循環(huán)相比較,再通過D/A轉(zhuǎn)換控制增益倍數(shù),從而實(shí)現(xiàn)自動(dòng)增益控制。

6 測試方案及測試數(shù)據(jù)

該系統(tǒng)使用專門的測試儀器,包括單片機(jī)仿真器、雙蹤示波器、PC機(jī)、多功能函數(shù)信號(hào)發(fā)生器和交流電壓表等。調(diào)節(jié)輸入信號(hào)的幅值和頻率,結(jié)合示波器,測試寬帶放大器的增益范圍以及通頻帶。測試結(jié)果表明,寬帶放大器總增益調(diào)節(jié)范圍為-6~70 dB。-3 dB通頻帶為40 Hz~15 MHz。將輸入信號(hào)頻率同定,改變輸入電壓幅值。記錄輸入電壓和輸出電壓的最大值和最小值。結(jié)果表明,AGC動(dòng)態(tài)范圍大于60 dB。將輸入端短接,設(shè)置不同的電壓放大倍數(shù),測量輸出電壓。結(jié)果表明,輸出電壓噪聲小于300 mV。

7 結(jié)束語

寬帶放大器以可編程增益放大器THS7001和可變?cè)鲆娣糯笃鰽D603為核心,利用數(shù)字技術(shù)實(shí)現(xiàn)增益的步進(jìn)和預(yù)置。總增益范圍為-6~70 dB,通頻帶為40.Hz~15 MHz,AGC動(dòng)態(tài)范圍達(dá)到60 dB。前置放大器采用低噪聲電壓反饋型運(yùn)放THS4011,大大提高輸人電阻。后級(jí)功率放大采用電流型反饋運(yùn)放AD811,有效提高系統(tǒng)的帶負(fù)載能力。系統(tǒng)采用多種抗干擾措施,并結(jié)合軟件修正,實(shí)現(xiàn)較高的精度,具有良好的噪聲,線性性能以及較低的功耗。系統(tǒng)界面友好,操作簡單,經(jīng)測試已投入應(yīng)用。