隨著微電子制造業(yè)的發(fā)展,制作高速、高集成度的CMOS電路已迫在眉睫,從而促使模擬集成電路的工藝水平達(dá)到深亞微米級。因為諸如溝道長度、溝道寬度、閾值電壓和襯底摻雜濃度都未隨器件尺寸的減小按比例變化,所以器件的不匹配性隨著器件尺寸的減小越加明顯。在短溝道CMOS電路中由于不匹配性引起的特性變化可能會限制器件尺寸的減小而影響工藝水平的發(fā)展,這樣不匹配性的消除就顯得更重要。

1 差分放大器性能

差分放大器的目的是抑制共模輸出,增大差模輸出。期望差模輸出電壓隨差模輸入電壓的變化而成比例變化。任意信號中的共模輸入部分在電路中必須受到抑制。在理想對稱的差分放大器中,每邊的輸出值都等于另外一邊的輸出值。當(dāng)Vi1=-Vi2時,有Vo1=-Vo2,此時放大器是理想對稱的。換言之,當(dāng)輸入是理想的差模電壓(Vic=0)時,輸出也是純粹的差模形式的電壓(Voc=0),因此Adm-cm=0。類似的,當(dāng)只輸入共模電壓(Vid=0)時,Acm-dm=0。但是,即使在理想對稱的差分放大器中,也不可能做到Acm=0。何況,即使標(biāo)稱相同的器件也會因為制造工藝的原因,存在有限的不匹配(失配)。因此非理想差分放大器本身還存在不匹配現(xiàn)象。

差分放大器性能的一個重要方面就是所能檢測到的最小直流和交流差模電壓。放大器的不匹配效應(yīng)和溫漂都在輸出端產(chǎn)生了難以區(qū)分的直流差模電壓。同樣,不匹配效應(yīng)和溫漂會使非零的共模輸入一差模輸出增益非零的差模輸入一共模輸出增益增大。非零的Acm-dm對于放大器尤其重要,因為它將共模輸入電壓轉(zhuǎn)換為差模輸出電壓,但在下一級輸入時,卻被當(dāng)作差模電壓信號。

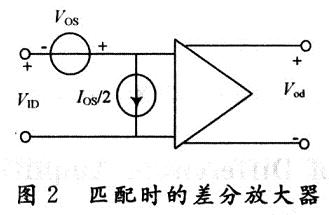

如圖1所示,當(dāng)Vin=0,且完全對稱,Vout=0,但在失配存在的情況下,Vout≠0。對于差分放大器來說,不匹配效應(yīng)對直流性能的影響主要在兩個方面:輸人失調(diào)電壓和輸入失調(diào)電流,這兩個參量描述了差分放大器中直流性能的一些輸入?yún)⒖夹?yīng)。如圖2所示,一個匹配的放大器的直流特性和一個失調(diào)電壓源串聯(lián)在輸入端、失調(diào)電流源并聯(lián)在輸入端的時理想放大器的直流特性完全一致。只有當(dāng)這兩個參量都存在的情況下,失調(diào)模型才是正確的。

2 工藝消除失配

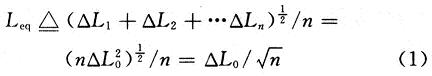

將處在飽和區(qū)的MOS管的特性表述為: 1/2μCoxW/L(VGS-VTH)2。對于兩個標(biāo)稱相同的晶體管,μ,Cox,W,L以及VTH之間的失配導(dǎo)致了漏極電流的失配(VGS固定)或柵源電壓的失配(漏極電流固定)。直觀上可以認(rèn)為,隨著W與L的增加,他們的相對失配,△W/W與△L/L會分別減小,也就是越大的器件表現(xiàn)出越小的失配。一個更重要的觀察結(jié)果是,隨著晶體管面積(W/L)的增加,所有的失配都減小。例如,增大W會使△W/W與△L/L都減小。這是因為隨著WL,的增加,隨機(jī)變化經(jīng)歷更大的“求平均”過程,因此其幅值下降了。對于圖3所示的情況,有△L2<△L1。這是因為,如果該器件被看成許多小晶體管的并聯(lián),如圖3所示,若每一個寬度為W0,那么可以得出等效長度為:

1/2μCoxW/L(VGS-VTH)2。對于兩個標(biāo)稱相同的晶體管,μ,Cox,W,L以及VTH之間的失配導(dǎo)致了漏極電流的失配(VGS固定)或柵源電壓的失配(漏極電流固定)。直觀上可以認(rèn)為,隨著W與L的增加,他們的相對失配,△W/W與△L/L會分別減小,也就是越大的器件表現(xiàn)出越小的失配。一個更重要的觀察結(jié)果是,隨著晶體管面積(W/L)的增加,所有的失配都減小。例如,增大W會使△W/W與△L/L都減小。這是因為隨著WL,的增加,隨機(jī)變化經(jīng)歷更大的“求平均”過程,因此其幅值下降了。對于圖3所示的情況,有△L2<△L1。這是因為,如果該器件被看成許多小晶體管的并聯(lián),如圖3所示,若每一個寬度為W0,那么可以得出等效長度為:

式中:△L0是寬為W0的晶體管長度變化的統(tǒng)計值。等式表明,對于給定的W0,隨著n的增加,Leq的變化減小,如圖4所示。

上述結(jié)論也可以擴(kuò)展到其他器件參數(shù)。例如,假定:器件面積增加,μCox與VTH有更小的失配。如圖5所示,理由是,大尺寸晶體管可以分解為寬長分別為W0和L0小單元晶體管的串并聯(lián)。其中,每個單元都呈現(xiàn)出(μCox)j與VTHj。對于給定的W0與L0,μCox與VTH經(jīng)歷更大的平均過程,致使大尺寸晶體管之間的失配更小。

3 版圖方法減少失配

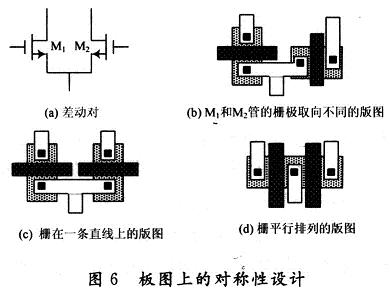

針對電路設(shè)計中,特別是全差動電路中的不對稱而產(chǎn)生的電路失調(diào),盡管有些失配是不可避免的,但是在版圖設(shè)計中,可通過器件對稱設(shè)計,使晶體管方面優(yōu)化,對所關(guān)心的器件及周圍環(huán)境進(jìn)行對稱性設(shè)計,盡量減少因工藝制造原理而引起的失配。

如圖6(a)所示,如果兩個MOS管按圖6(b)那樣沿不同方法放置,由于在光刻及圓片加工的許多步驟中沿不同軸向的特性大不一樣,就會產(chǎn)生很大失配。因而圖6(c)和(d)的方案更合理一些。這兩者的選擇是由一種稱作“柵陰影”的細(xì)微效應(yīng)決定的。

如圖7(b)所示,為了避免溝道效應(yīng),通常在源一漏離子注入時把注入方向(或圓片方向)傾斜7°左右,這樣?xùn)艠O多晶硅就會阻擋一部份離子,形成陰影區(qū)。結(jié)果,在源區(qū)或漏區(qū)就有一條窄區(qū),它接收的注入較小,因而在注入退火之后,使源區(qū)和漏區(qū)邊緣的擴(kuò)散產(chǎn)生了細(xì)微的不對稱。

圖7(a)給出考慮有柵陰影存在時的結(jié)構(gòu)圖,在圖中,如果陰影區(qū)出現(xiàn)在源區(qū)(或漏區(qū)),那么這兩個器件不會因陰影導(dǎo)致不對稱。在圖中,即使標(biāo)出了這兩個管子在陰影區(qū)的源(或漏)極,這兩個MOS管也不一樣,這是因為M1管源區(qū)的右邊是M2管,而M2管源區(qū)的右邊是場氧。同樣,M1和M2左邊的結(jié)構(gòu)也不一樣。就是說在制造過程中,M1和M2周圍的工藝步驟不一致。因此圖8所示的結(jié)構(gòu)更好。

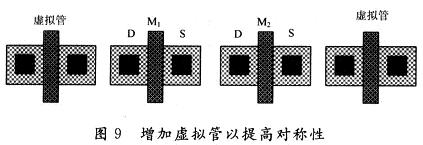

圖8所示結(jié)構(gòu)固有的不對稱性可以通過在晶體管兩邊加兩個虛擬MOS管的方法加以改進(jìn),因為這可以使M1和M2管周圍的環(huán)境幾乎相同,如圖9所示。

同時,在對稱軸的兩邊保持相同環(huán)境也很重要。例如,在版圖中,只有一個MOS管旁邊有一條無關(guān)的金屬線通過,這會降低對稱性,增大M1和M2之間的失配。在這種情況下,也可以在另一邊放置一條相同的金屬線(見圖10),最好的辦法就是去掉引起不對稱的金屬線。

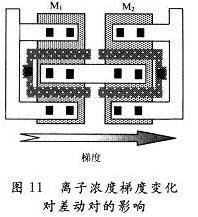

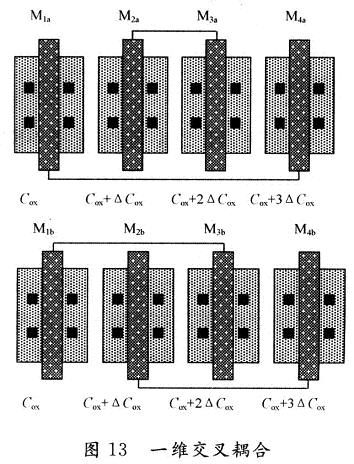

對于大的晶體管,對稱性就變得更困難了。例如,在圖11所示的差分對中,為使輸人失調(diào)電壓較小,這兩個晶體管的寬度都比較大,但沿x軸方向的梯度會引起明顯的失配。為了減小失配,可以采用“共中心”的布局方法。這樣沿x軸和y軸方向的一階梯度效應(yīng)就會互相抵消。如圖12所示,這種布局把M1和M2都分成兩個寬度為原來50%的晶體管,沿對角放置且并聯(lián)連接。然而,在版圖上布線很困難,經(jīng)常會導(dǎo)致如圖13所示的系統(tǒng)不對稱,或者線對地電容及線間電容的不同而引起整體不對稱。對于規(guī)模大一點的電路,如運放,則引走線可能過于復(fù)雜而無法實現(xiàn)。

線性梯度效應(yīng),也可像圖12所示,通過“一維”交叉耦合的辦法得到抑制。這里,所有四個寬度為50%的晶體管一字排開,M1和M2可由相鄰兩個晶體管與相距最遠(yuǎn)的兩個晶體管分別相連構(gòu)成,也可由兩組相間隔的晶體管分別相連構(gòu)成。

為分析該結(jié)構(gòu)中的梯度效應(yīng),假設(shè)每兩個相鄰的半寬晶體管之間的柵氧電容變化為△Cox。將M1a和M4a并聯(lián),得到:

因此,這種類型的交叉耦合抵消了梯度效應(yīng)的影響。若用圖13所示的組合可得:

式(4)和式(5)顯示,圖13所示的方法消除誤差的能力較差。

4 結(jié) 語

針對CMOS差動放大器晶體管的不匹配,從理論上深刻分析其不匹配原因,介紹電路設(shè)計方法和版圖設(shè)計方法進(jìn)行失調(diào)電壓的消除,并對所提出的電路技術(shù)進(jìn)行仿真驗證,能夠達(dá)到降低失調(diào)電壓的效果。