O 引言

FIR(fini te impulse response)濾波器是數(shù)字信號處理系統(tǒng)中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴(yán)格的線性相頻特性,同時其單位沖激響應(yīng)是有限的,沒有輸入到輸出的反饋,系統(tǒng)穩(wěn)定。因此,F(xiàn)IR濾波器在通信、圖像處理、模式識別等領(lǐng)域都有著廣泛的應(yīng)用。在工程實(shí)踐中,往往要求對信號處理要有實(shí)時性和靈活性,而已有的一些軟件和硬件實(shí)現(xiàn)方式則難以同時達(dá)到這兩方面的要求。隨著可編程邏輯器件的發(fā)展,使用FPGA來實(shí)現(xiàn)FIR濾波器,既具有實(shí)時性,又兼顧了一定的靈活性,越來越多的電子工程師采用FPGA器件來實(shí)現(xiàn)FIR濾波器。

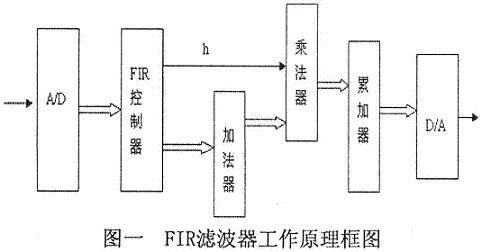

1 FIR濾波器工作原理

在進(jìn)入FIR濾波器前,首先要將信號通過A/D器件進(jìn)行模數(shù)轉(zhuǎn)換,使之成為8bit的數(shù)字信號,一般可用速度較高的逐次逼進(jìn)式A/D轉(zhuǎn)換器,不論采用乘累加方法還是分布式算法設(shè)計FIR濾波器,濾波器輸出的數(shù)據(jù)都是一串序列,要使它能直觀地反應(yīng)出來,還需經(jīng)過數(shù)模轉(zhuǎn)換,因此由FPGA構(gòu)成的FIR濾波器的輸出須外接D/A模塊。FPGA有著規(guī)整的內(nèi)部邏輯陣列和豐富的連線資源,特別適合于數(shù)字信號處理任務(wù),相對于串行運(yùn)算為主導(dǎo)的通用DSP芯片來說,其并行性和可擴(kuò)展性更好,利用FPGA乘累加的快速算法,可以設(shè)計出高速的FIR數(shù)字濾波器。

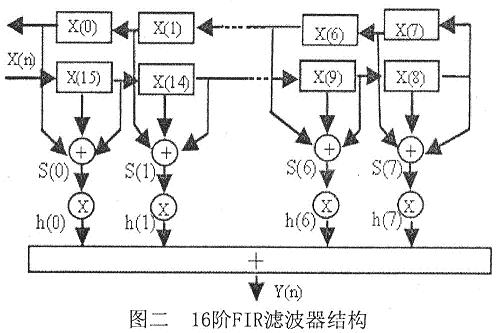

2 16階濾波器結(jié)構(gòu)

在濾波過程中實(shí)現(xiàn)抽取,對于抽取率為N的抽取濾波器而言,當(dāng)進(jìn)來N個數(shù)據(jù)時濾波器完成1次濾波運(yùn)算,輸出1次濾波結(jié)果。抽取濾波器的結(jié)果和先濾波后抽取的結(jié)果是一致的,只是對于同樣的數(shù)據(jù),進(jìn)行濾波運(yùn)算的次數(shù)大大減少。在數(shù)字系統(tǒng)中采用拙取濾波器的最大優(yōu)點(diǎn)是增加了每次濾波的可處理時間,從而達(dá)到實(shí)現(xiàn)高速輸入數(shù)據(jù)的目的。采樣數(shù)據(jù)與濾波器系數(shù)在控制電路的作用下,分別對應(yīng)相乘并與前一個乘積累加,經(jīng)過多次(有多少階就要多少次)反復(fù)的乘累加最后輸出濾波結(jié)果,將相同系數(shù)歸類,16階濾波器公式:

乘法器的數(shù)量減少一半,但加法器的數(shù)量增多了,但相對乘法運(yùn)算來說,加法運(yùn)算所占用的資源少的多,運(yùn)算的速度也快得多。

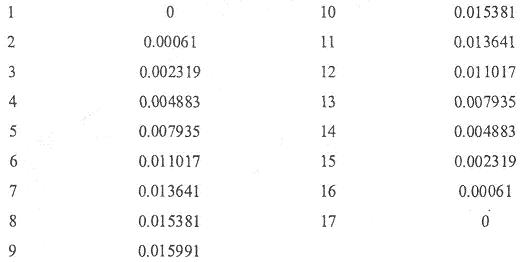

3 濾波器系數(shù)的求取

使用Matlab集成的濾波器設(shè)計工具FDAtool,可以完成多種濾波器的數(shù)值設(shè)計、分析與評估,設(shè)計16階低通濾波器參數(shù)如下:

采樣頻率:Fs為50MHz,濾波器歸一化截止頻率:Fc為0.4MHz,輸入數(shù)據(jù)位寬:8位,輸出數(shù)據(jù)寬度:16位FDAtool采用漢寧窗函數(shù)(Hanning)設(shè)計16階線性相位FIR數(shù)字濾波器,并提取其特性參數(shù)h(n)浮點(diǎn)數(shù)值。

MATLAB中算出的系數(shù)h(n)的值是一組浮點(diǎn)數(shù),進(jìn)行浮點(diǎn)值到定點(diǎn)值的轉(zhuǎn)換,用16位二進(jìn)制補(bǔ)碼表示為

濾波器抽頭數(shù)是16個,考慮到線性FIR濾波器的偶對稱特性,只考慮8個獨(dú)立濾波器抽頭數(shù),則需要一個28×8的表(其中指數(shù)8指的是8個濾波器抽頭數(shù),后面的8指的是輸入數(shù)據(jù)的位寬)。但是Virrex—e FPGA只能提供4輸入的杏找表,所以要對查找表的地址進(jìn)行電路分割。將8位地址線分為高4位和低4位,分別作為兩個24×8的查找表的地址輸入,從而指數(shù)倍地節(jié)省了硬件資源。

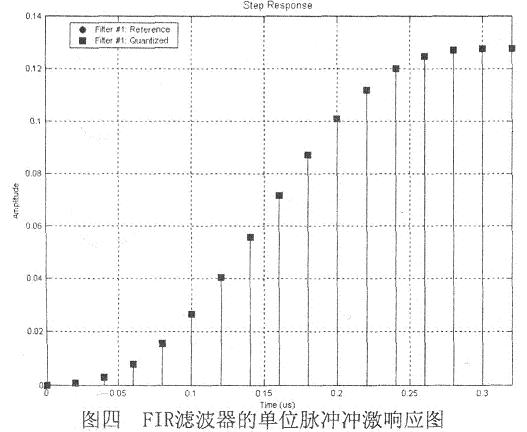

4 主程序及仿真

在時鐘和計數(shù)器的控制下,根據(jù)查找表輸出結(jié)果位權(quán)的不同,將輸入數(shù)據(jù)向左移動相應(yīng)的位數(shù),低位按照位權(quán)的不同補(bǔ)上個數(shù)相當(dāng)?shù)?ldquo;0”,然后將移位數(shù)據(jù)進(jìn)行累加操作,輸出最終濾波結(jié)果,這里的結(jié)果依舊是用二進(jìn)制數(shù)據(jù)表示的,只是位數(shù)因?yàn)橐莆缓屠奂硬僮髟黾恿?位。

圖五 移位加法器的波形仿真圖

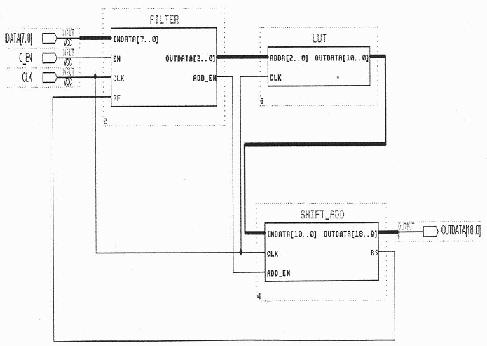

以上便是基于分布式算法的FIR濾波器的三個主要模塊的分析,為了能使該濾波器能正常工作,還需要用VHDL語言編寫控制程序,使各模塊連接起來,總的來說,該濾波器的實(shí)現(xiàn)原理圖如下:

圖六基于分布式算法的FIR濾波器頂層原理圖在FPGA中,不論是基于乘累加的FIR濾波器,還是基于分布式算法的FIR濾波器(包括FIR濾波器的各模塊)都是通過VHDL語言編程來實(shí)現(xiàn)的。

5 結(jié)語

本文所介紹的基于FPGA、采用分布式算法實(shí)現(xiàn)FIR濾波器的方法,在提高系統(tǒng)運(yùn)行速度和節(jié)省硬件資源方面具有很大的優(yōu)勢。基于分布式算法的FIR濾波器結(jié)構(gòu)可以擴(kuò)展成任意階數(shù)的FIR濾波器。而且,通過改變階數(shù)和查找表中的系數(shù),還可以將此設(shè)計靈活地運(yùn)用于實(shí)現(xiàn)高通、低通和帶阻濾波器,可移植性較好。因此,這種方法在高速數(shù)字信號處理中將有很好的應(yīng)用前景。