數(shù)字信號處理器(Digital Signal Processor,DSP)在圖形圖像處理、高精度測量控制、高性能儀器儀表等眾多領(lǐng)域得到越來越廣泛的應(yīng)用,實際運用中,通常須將DSP采集處理后的數(shù)據(jù)傳送到PC機,然后進行存儲和處理。

T1公司的TMS320VC33微處理器具有性價比高,同時,該芯片的I/O電平、字長、運行速度、串口功能具有大多數(shù)DSP的共同特點。本文針對TMS320VC33與PC RS-232的通訊,分析三種具體的接口電路和軟件設(shè)計方法,實現(xiàn)高速DSP與低速設(shè)備的通訊:①通過TMS320VC33的通用I/O口實現(xiàn)通信;②通過TMS320VC33中可設(shè)置為通用I/O的串行引腳實現(xiàn)通信;③直接利用TMS320VC33的串口功能實現(xiàn)通信,在硬件和軟件設(shè)計的基礎(chǔ)上,完成相關(guān)試驗和調(diào)試,并達到預(yù)期的效果。

采用通用I/O口實現(xiàn)

PC的RS-232接口按照設(shè)定的固定波特率傳送,RS-232串行口進行通信采用三線式接法,即RX(數(shù)據(jù)接收)、TX(數(shù)據(jù)發(fā)送)、GND(地)三個引腳,PC機按幀格式發(fā)送、接收數(shù)據(jù),一幀通常包括1位起始位("0"電平)、5-8位數(shù)據(jù)位、1 位(或無)校驗位、1位或1位半停止位("1"電平),起始位表示數(shù)據(jù)傳送開始,數(shù)據(jù)位為低位在前、高位在后,停止位表示一幀數(shù)據(jù)結(jié)束。

TMS320VC33微處理器的串口幀格式?jīng)]有起始位和停止位,只有數(shù)據(jù)位,且數(shù)據(jù)位為高位在前、低位在后。利用TMS320VC33微處理器的通用I/O引腳實現(xiàn)串行通信時,須依據(jù)RS232的通信協(xié)議并結(jié)合DSP硬件資源編寫相應(yīng)的DSP程序。

1.硬件設(shè)計

TMS320VC33微處理器共有10個引腳可配置為通用I/O口,其中XFO、XFl為專用的通用I/O口,通過軟件設(shè)計可實現(xiàn)XFO、XFl專用I/O口與RS232的串行通信,電路結(jié)構(gòu)如圖1所示。

串口通信的方法" onclick="get_larger(this)" src="http://files.chinaaet.com/images/20100810/294996af-0f04-434f-b02a-49ec536971af.jpg" />

本文選用MAX3232E作為RS232C電平與TTL電平的轉(zhuǎn)換芯片,R1in、T1out為RS232C電平,R1out、T1in為TTL電平,TMS320VC33微處理器的INT2引腳為外部中斷腳,R10ut同時連接到INT2和XF0,即可利用傳輸?shù)牡谝晃挥|發(fā)TMS320VC33微處理器的外部中斷。

2.軟件設(shè)計

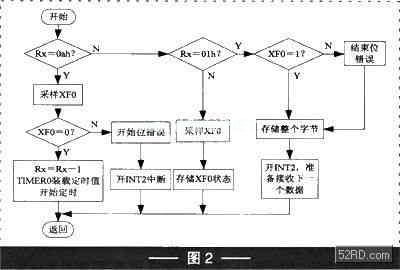

假設(shè)系統(tǒng)已經(jīng)完成初始化,數(shù)據(jù)接收流程如圖2所示,設(shè)傳輸速率為9600bit/s,一個起始位("0")、8位數(shù)據(jù)位、一個終止位("1")。數(shù)據(jù)傳輸時對起始位定時半位的時間,數(shù)據(jù)位第一位以后的定時周期設(shè)置為一個位的時間,保證每一位數(shù)據(jù)都在中間采樣,與傳統(tǒng)RS232串口傳輸方式不同,有利于降低傳輸?shù)恼`碼率。

數(shù)據(jù)傳輸時,先判斷Rx是否為OAh,即判斷是不是傳輸起始位,若Rx=OAh,表明數(shù)據(jù)開始傳輸;接著判斷XF0管腳的狀態(tài)是否為"O",若XF0=1,則數(shù)據(jù)傳輸錯誤,重新接收下一個數(shù)據(jù);若XF=0,則表示數(shù)據(jù)開始正常傳輸;然后將Rx-1,同步刷新Rx中的內(nèi)容,即Rx=Rx-1;同時,在TIMER0的周期寄存器和計數(shù)寄存器中存入定時整個位的時間常數(shù),開定時器0的中斷,定時時間一到,程序進入TIMER0的中斷服務(wù)子程序,再判斷Rx是不是終止位,若Rx為終止位,則開始繼續(xù)接收新的數(shù)據(jù),打開INT2,將TIMER0周期寄存器和計數(shù)寄存器中存放半位的時間參數(shù);若Rx不是終止位,則繼續(xù)接收數(shù)據(jù)位,直到Rx接收到終止位。

數(shù)據(jù)發(fā)送程序與數(shù)據(jù)接收程序原理相同,此處略。

串口引腳作為通用I/O口實現(xiàn)

1.硬件設(shè)計

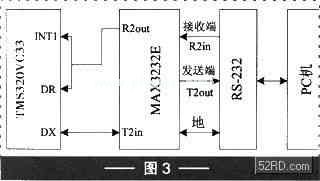

TMS320VC33微處理器的串口引腳也可作為通用I/O口,通過對I/0口的操作即可實現(xiàn)串行數(shù)據(jù)的接收和發(fā)送,將微處理器的數(shù)據(jù)接收引腳DR作為RS232的數(shù)據(jù)接收端,數(shù)據(jù)發(fā)送引腳DX作為RS232的數(shù)據(jù)發(fā)送端,電路結(jié)構(gòu)如圖3所示,圖中MAX3232E的R2out與TMS320VC33微處理器的lNT1和DR相連。

2.軟件設(shè)計

軟件設(shè)計與I/O口軟件原理相似,TMS320VC33微處理器串口寄存器將串口功能引腳DR、DX設(shè)置為通用I/O口功能,不實施串口功能,即DR、DX引腳的功能與圖1中XF0和XF1的功能相同,接收數(shù)據(jù)的流程與圖2原理相同。

需要說明兩點:①將圖1和圖3硬件電路相組合,即可實現(xiàn)一片TMS320VC33微處理器與兩臺微機的同時通信;②TMS320VC33微處理器共有10個引腳可配置為通用I/O口,因此,利用TMS320VC33微處理器的內(nèi)部和外部中斷源、2個定時器、1個串口定時器和軟件定時等方式,可巧妙地實現(xiàn)1片TMS320VC33微處理器與多臺微機同時通信。

串口功能實現(xiàn)

該方法直接利用TMS320VC33微處理器的串口功能實現(xiàn)通信。TMS320VC33微處理器的串行通信有固定數(shù)據(jù)速率和可變數(shù)據(jù)速率兩種類型,每種類型又分連續(xù)、標準和爆發(fā)三種方式。

1.硬件設(shè)計

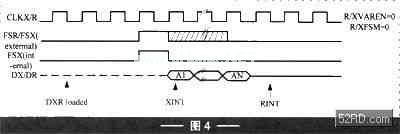

本文與RS232接口的通信方式采用固定速率的爆發(fā)方式,在該方式下,每個字的傳送都由幀同步(FSX/FSR)信號開始,后面開始為數(shù)據(jù)位,其時序如圖4所示。TMS320VC33微處理器在爆發(fā)方式接收數(shù)據(jù)時,從幀同步信號后開始接收數(shù)據(jù),并不再考慮FSR信號,在一幀信號傳輸?shù)淖詈笠晃粫r,F(xiàn)SR必須為低電平,否則將會被作為下一幀的幀同步信號位。

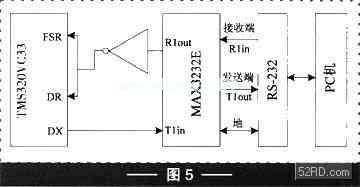

TMS320VC33微處理器與標準串口間的通信硬件結(jié)構(gòu)如圖5所示,同樣采用三線連接的電路。因PC起始位為低電平,TMS320VC33微處理器幀同步位為高電平,為使兩者統(tǒng)一,MAX3232E的R10ut信號經(jīng)一反相器后,再連接到DSP的DR和FSR引腳,同時加反相器后,數(shù)據(jù)相位和停止位都相應(yīng)變反,但是很容易用軟件方法還原數(shù)據(jù)信號。

2.軟件設(shè)計

軟件設(shè)計比前兩種方法更為簡單,只需將串口的相應(yīng)寄存器位設(shè)置好,然后開啟相應(yīng)中斷即可完成與PC的通信,此方

法在接收時采用幀同步信號,誤碼率較低,是一種比較實用的方法。

①在DSP接收時,接收信號同時連接到接收引腳DR和接收幀同步引腳FSR,故PC發(fā)送1幀信號的起始位是被用作接收幀同步信號,然后才開始接收數(shù)據(jù),而且FSR引腳在接收幀的最后一位時必須為低電平,以滿足TMS320VC33微處理器爆發(fā)方式串行通信的要求。PC采用上述發(fā)送幀格式,停止位反相后,正好滿足FSR的要求。

②在DSP發(fā)送時,TMS320VC33微處理器的字長只能是8、16、24或32位,且不需要起始位、結(jié)束位;RS232的字長只能是8位,且需要起始位和結(jié)束位。由圖5知,TMS320VC33微處理器的FSX采用內(nèi)部同步,DX引腳上為數(shù)據(jù)位,為符合PC接收的幀格式,需將數(shù)據(jù)位設(shè)置為16位,將最高位作為起始位、8位數(shù)據(jù)位、1位停止位、6位空閑位,即符合PC幀格式為10位的通信要求,同時空閑位不影響數(shù)據(jù)通信,同時也正是由于有空閑位,所以采用固定速率的爆發(fā)方式。

結(jié)論

本文的TMS320VC33微處理器與PC實現(xiàn)串口通信的方法可以為其它型號的高速DSP與PC之間實現(xiàn)通信提供參考。

另外,將MAX3232E芯片換成MAX485可實現(xiàn)DSP與RS-485接口的通信,即提高了數(shù)據(jù)傳輸速率,增加了傳輸距離,同時,增強了數(shù)據(jù)傳輸中抗干擾能力,對復(fù)雜環(huán)境的數(shù)據(jù)傳輸通訊有重要的應(yīng)用意義。