當(dāng)今手機(jī)的一個(gè)共同發(fā)展趨勢(shì)是LCD和相機(jī)總線的串行化,這是為了降低柔性PCB 成本,節(jié)省 PCB 空間,以及減少 EMI 組件。然而,在串行方案設(shè)計(jì)方面,人們可能認(rèn)為:這些串行化方案會(huì)增加額外的功耗,原因是增加了器件。本文將闡明若能降低基帶驅(qū)動(dòng)輸出,使其配合串化器輸入的較低驅(qū)動(dòng)需求,那么串行化方案能夠降低鏈路功耗。設(shè)計(jì)人員如能了解 LCD 或相機(jī)總線的這一 “功率轉(zhuǎn)折” 點(diǎn),就能降低設(shè)計(jì)功耗。

串行化趨勢(shì):

隨著手機(jī)需要實(shí)現(xiàn)的功能越來越多,且外形越來越復(fù)雜,人們開始采用串行化技術(shù)來達(dá)到手機(jī)的設(shè)計(jì)目標(biāo)。采用串行化技術(shù)就可使用較窄的柔性PCB (FPCB),減少PCB空間,省去一些不必要的 EMI 組件,通過使用較小的連接器來提高可靠性。采用串行化技術(shù),設(shè)計(jì)人員可以大幅減少通過 FPCB 發(fā)送的信號(hào)線數(shù)量,從而實(shí)現(xiàn)更小巧、更復(fù)雜的連接 設(shè)計(jì)。但即便有這些好處,人們還是心存疑慮:增加額外的器件來實(shí)現(xiàn)串行化方案,會(huì)不會(huì)導(dǎo)致系統(tǒng)功耗增加。鑒于手機(jī)設(shè)計(jì)有嚴(yán)格的功耗限制,因此,本文將討論采用串行化技術(shù)降低功耗的真實(shí)性。

并行實(shí)現(xiàn)方案:

圖1所示為一個(gè)典型的并行方案。

圖1:典型的并行方案。

在這個(gè)架構(gòu)中,基帶處理器 (baseband processor, BP) 驅(qū)動(dòng)電路的負(fù)載包括主PCB的走線、FPCB、FPCB連接器,以及翻蓋PCB上的走線和最終的顯示器負(fù)載。BP驅(qū)動(dòng)電路必須能夠直接采用 LVCMOS 信令來驅(qū)動(dòng)該負(fù)載。

采用RGB接口的顯示器可能需要高達(dá)24位的數(shù)據(jù),而這對(duì)WQVGA顯示來說就需要8MHz或更高的帶寬,具體要視顯示屏分辨率而定。顯示屏分辨率越高,顯示器接口所需的信號(hào)帶寬就越大。

串行方案:

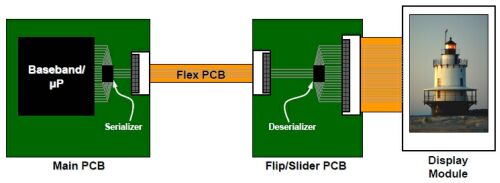

在串行顯示方案中,在主PCB和翻蓋PCB的數(shù)據(jù)通道上放置了一對(duì)器件。串化器位于主PCB上,將并行顯示數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù)流,并通過FPCB傳送到解串器。根據(jù)所采用的串行化架構(gòu)而定,可以把數(shù)個(gè)串行數(shù)據(jù)信號(hào)縮減為一對(duì)差分信號(hào)。解串器將串行數(shù)據(jù)流轉(zhuǎn)換成驅(qū)動(dòng)顯示器接口的并行數(shù)據(jù)流 (參見圖2)。

圖2:串行實(shí)現(xiàn)方案。

并行方案和串行方案有著重要的差別,而正是這些差別使得串行方案得以減少鏈路功耗。在主PCB上使用一個(gè)串化器后,BP 輸出驅(qū)動(dòng)電路的要求就大大降低,這是因?yàn)榇鬏斎氲尿?qū)動(dòng)負(fù)載比并行顯示器通道所需的低得多。采用串行接口后,BP還可降低輸出電壓,并允許串化器處理到顯示器驅(qū)動(dòng)電路的電平轉(zhuǎn)換。例如,顯示器工作電壓為2.7V,BP可將輸出到串化器的電壓降至1.8V。然后,解串器將產(chǎn)生顯示器所需的2.7V信號(hào)。

此外,大多數(shù)串行方案采用差分信令協(xié)議,類似于低壓差分信號(hào) (LVDS)。這種信號(hào)能大幅降低通過FPCB傳送數(shù)據(jù)所需的電壓振幅,還可減小信號(hào)鏈路的EMI。通過減小信號(hào)振幅,并因串行流中EMI減小而取消雙重屏蔽FPCB,串行方案就可以降低功耗。