CMOS RRO: 具有雙通道反饋的 RISO

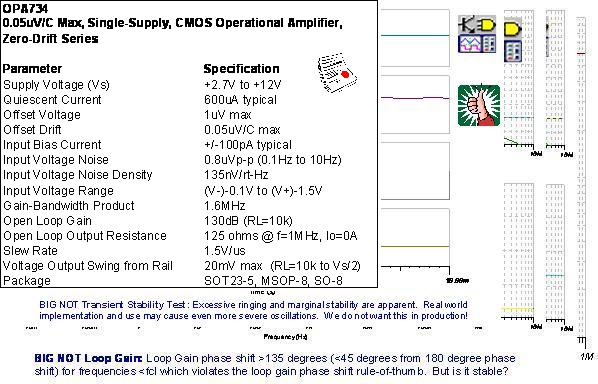

我們選擇用于分析具有雙通道反饋的 RISO 的CMOS RRO 為OPA734,,具體情況請參閱圖 10.38,。OPA734 是一款低漂移、低輸入失調(diào)電壓的運算放大器,,其能在 +2.7V~+12V 的電壓范圍內(nèi)工作,。這種極低的漂移(0.05uV/C)加上其超低的初始輸入失調(diào)電壓(1uV),使 OPA734 成為了單電源應(yīng)用中理想的參考緩沖放大器,。由于這并非是軌至軌 CMOS 輸入放大器,,因此,,我們有必要觀察輸入電壓范圍的技術(shù)規(guī)范[(V–)–0.1V 至(V+)–1.5V],。

圖 10.38 CMOS RRO 運算放大器的技術(shù)規(guī)范

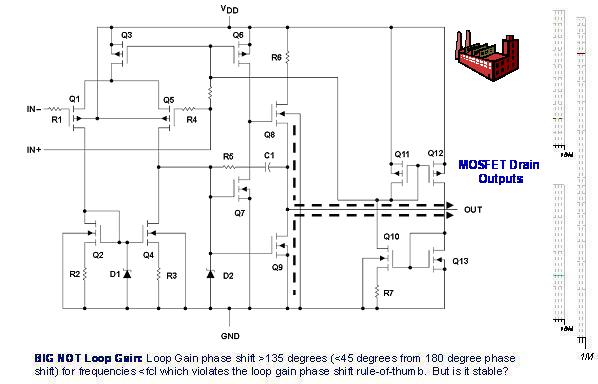

典型的 CMOS RRO 等效電路圖如圖 10.39 所示。從圖中可以看出,,運算放大器的輸出端連接至 MOSFET 的漏極,。這種漏極輸出運算放大器具備一個 Zo(同時具有阻性和容性的特點),要求我們運用某些相對于雙極發(fā)射極跟隨器略有不同的分析技術(shù),,如具有雙通道反饋的 RISO 電路示例,。

圖 10.39 典型的 CMOS RRO 運算放大器拓撲結(jié)構(gòu)

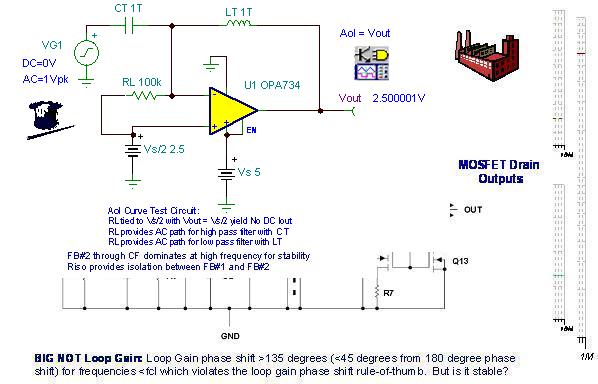

從圖 10

.40 中我們可以看出,CMOS RRO 參考緩沖電路的外觀與雙極發(fā)射極跟隨器示例中所采用的電路外觀一模一樣,。在本應(yīng)用示例中,,我們采用電壓為 5V 的單電源,,對 2.5V 的參考電路(該電路的電壓值低于輸入電壓范圍的技術(shù)規(guī)范[輸入電壓范圍:5V–1.5V =3.5V])進行緩沖。由于為了獲得良好的穩(wěn)定性,,在高頻時 FB#1 和 FB#2 將提供所需要的反饋,,因此,在 Vout 處,,可獲取準確的參考電壓,。Riso 將使兩條反饋電路單獨運行,互不干擾,。

圖 10.40 具有雙通道反饋的 RISO:CMOS RRO

由于在本應(yīng)用示例中,,我們采用的是單電源,因此,,我們將運用一些新技巧來獲取如圖 10.41所示的空載 Aol 曲線,。首先,我們需要確保在開展 DC 工作點分析之后的 OPA734 輸出信號處于工作的線性區(qū)域,。通常來說,,由于運算放大器的飽和輸出信號并非處在工作的線性區(qū)域,因此,,其未能提供恰當?shù)?AC 性能,。對于大多數(shù)運算放大器宏模型來說也是如此。在 DC 狀態(tài)時,,LT 為短路而 CT 為開路,。OPA734 的非反相輸入限制為 Vs/2 (2.5V)。因此,,輸出將為 Vs/2 (2.5V),。如圖所示的 RL 接線方式,在運算放大器的輸出端不存在 DC負載,。RL 以及 LT 為低通濾波器函數(shù)提供了一條 AC 通道,。這樣,在反饋電路中,,就可使 DC 處于短路狀態(tài)而 AC 處于開路狀態(tài),。務(wù)必提請注意的是,在進行 AC 分析前,,SPICE 必須開展 DC 閉環(huán)分析,,以找到電路的工作點。另外,,RL 以及 CT 為高通濾波器函數(shù)提供了一條 AC 通道,,這樣,使得我們能將 DC 開路電路和 AC 短路電路一起并入輸入端。而且,,LT 和 CT 按大數(shù)值等級選用,,以確保其在各種相關(guān)的 AC 頻率時,電路短路和開路情況下的正常運行,。

圖 10.41 Aol 測試示意圖:CMOS RRO

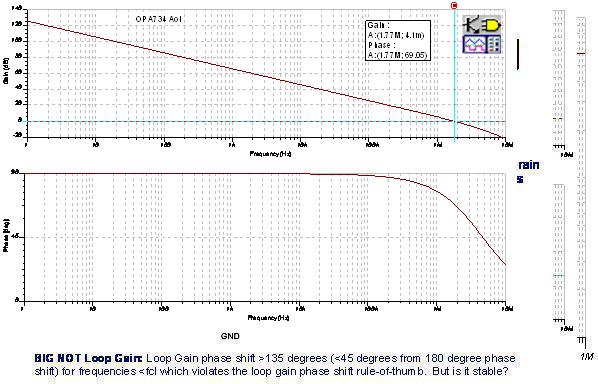

從 Tina SPICE 仿真測量得出的 OPA734 Aol 曲線如圖 10.42 所示,。測得的單位增益帶寬為 1.77MHz。

圖 10.42 Aol 測試結(jié)果:CMOS RRO

圖 10.43 由 Zo,、CCO,、 RCO、CL 改變 Aol 效應(yīng)的 TINA 電路

現(xiàn)在,,我們必須測量如圖 10.43 所示的 Zo(小信號 AC 開環(huán)輸出阻抗),。該 Tina SPICE 測試電路將測試空載 OPA734 的 Zo。請注意,,由于我們測試的是單電源電路,,因此將輸出信號調(diào)整至 Vs/2 (2.5V),以確保運算放大器輸出電流的正弦波位于工作的線性區(qū)域,。RL 以及 LT 為低通濾波器函數(shù)提供了一條 AC 通道,。這樣,在反饋電路中,,就可使 DC 處于短路狀態(tài)而 AC 處于開路狀態(tài),。由于 RL 限定在 Vout (2.5V) 和 Vs/2 (2.5V) 之間,所以 DC 工作點在輸出端顯示為 2.5V 或 Vs/2 伏,,這也就是說,,OPA734 沒有電流流入或流出。此時,,通過運用 1Apk AC 電流發(fā)生器(我們能夠掃視 10mHz 至 1MHz 的 AC 頻率范圍),,Zo 的測量工作能夠輕松完成。最后,,得出測量結(jié)果 Zo = Vout(如果將測量結(jié)果的單位從dB轉(zhuǎn)換為線性或?qū)?shù),,Vout 也就是以歐姆為單位的 Zo)。

圖 10.44 Zo,、開環(huán)輸出阻抗:CMOS RRO

從圖 10.44 中,,我們可以看出,,OPA734 Zo 是 CMOS RRO 運算放大器輸出級所獨有的特征。而且,這種輸出級的 Ro 在高頻時,,處于支配地位,。同時,Co 所呈現(xiàn)出的電容效應(yīng)在頻率低于 92Hz 時,,處于支配地位,。

根據(jù)前面圖表的仿真測試結(jié)果,我們在圖10.45中構(gòu)建了 OPA734 的 Zo 模型,。RO 直接測得為 129 歐姆,,fz 直接測得為 92Hz。根據(jù)測得的 fz 和 RO 數(shù)值,,我們可以輕松地計算出 CO 的數(shù)值(為 13.4uF),。最終完成了如圖所示的 Zo 模型。

圖 10.45 Zo 模型:CMOS RRO

圖 10.46:Zo 外部模型:CMOS RRO

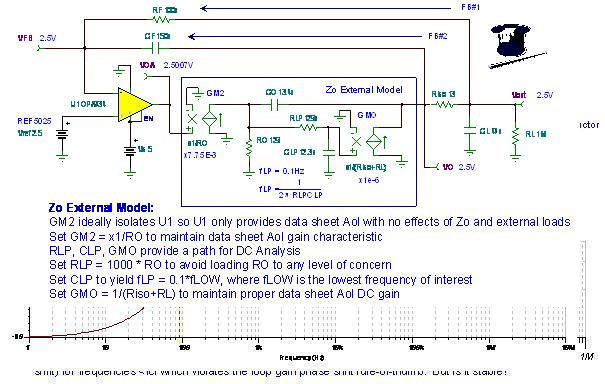

為了使 1/b分析的情況包含在?Zo 與 RISO,、CL,、CF 以及RF 之間相互作用的影響結(jié)果內(nèi),我們需將 Zo 從運算放大器的宏模型中分離出來,,以便于弄清楚電路中所需的節(jié)點,。這種構(gòu)思如圖 10.46 所示。另外,,U1 將提供產(chǎn)品說明書的 Aol 曲線,,并從 Riso、CL,、CF 以及 RF 的各種影響中得到緩沖,。

通過如圖 10.47 所示的 Zo 外部模型,我們能夠測量 Zo 與 Riso,、CL,、RF 以及 CF 之間的相互作用對

1/b的影響。RO 和 CO 是我們在前一張圖表中測出的參數(shù),。GM2 將 U1(OPA734 運算放大器宏模型)從 Zo 外部模型中隔離開來,。將 GM2 設(shè)置為 1/RO以保持適當?shù)?Aol 增益,目的是與最初的 OPA734 運算放大器宏模型和產(chǎn)品說明書中的 Aol 相匹配,。在 SPICE 進行 AC 分析前,,其必須開展 DC 分析。因此,,我們需確保擴展后的運算放大器模型,,將具備正確的 DC 工作點而無需使 U1 達到飽和狀態(tài)。為此,,我們在 CO 至 VO 之間添加了一條低頻通道,。GMO 將由 RO 兩端的電壓控制(該電壓與 VOA 相匹配),。將 GMO 設(shè)置為 1/RL 以維持 DC 狀態(tài)時的綜合增益水平,目的是與最初的 OPA734 Aol 相匹配,。另外,,一只低通濾波器由RLP 和 CLP形成,并設(shè)置為 0.1*fLOW(fLOW 是相關(guān)的最低頻率),。將 RLP 設(shè)置為 1000*RO,,以避免 RO 上出現(xiàn)負載或相互作用(影響),最終導(dǎo)致 Zo 傳輸函數(shù)發(fā)生錯誤,。

圖 10.47 Zo 外部模型詳圖:CMOS RRO

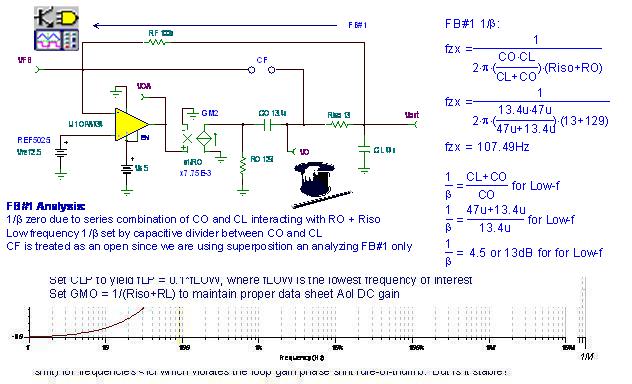

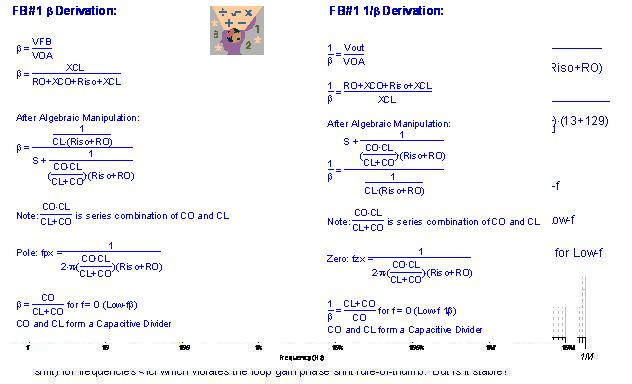

首先,,我們分析如圖 10.48 所示的 FB#1。請注意,,由于我們只分析 FB#1,,所以 CF 可視為處于開路狀態(tài)。接下來,,我們將分析 FB#2,。然后,通過采用疊加的方法,,將兩條反饋通道合并在一起,,求取最終的 1/b。分析結(jié)果如圖 10.48 所示,,有關(guān)的公式推導(dǎo)和具體細節(jié),,請參閱圖 10.49。我們發(fā)現(xiàn),,當 fzx="107".49Hz 時,,F(xiàn)B#1 1/b曲線上出現(xiàn)零點。低頻?1/b值為?4.5 或13dB,,并由介于 CO 和 CL 之間的電容分壓器確定,。如果改變電路以獲得增益,那么低頻?1/b值將大于1,。

圖 10.48 FB#1 分析:CMOS RRO

圖 10.49 FB#1 1/b公式推導(dǎo):CMOS RRO

FB#1b的公式推導(dǎo)如圖 10.49 左側(cè)所示,。由于 1/b是b的倒數(shù),所以?FB#1 1/b的計算結(jié)果可以輕而易舉的推導(dǎo)出來,,具體推導(dǎo)過程,,請參閱圖?10.49 右側(cè)。從圖中我們還發(fā)現(xiàn),,在b推導(dǎo)過程中的?pole, fpx 變成了 1/b推導(dǎo)過程中的?zero, fzx,。

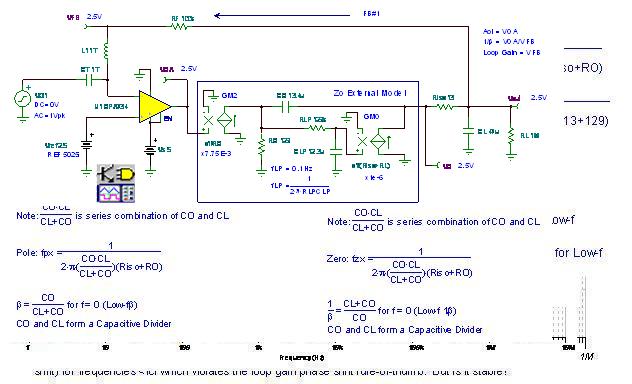

我們將采用如圖 10.50 所示的電路來開展 AC 分析:通過 Tina SPICE,找到 FB#1 的 1/b,,OPA177 的 Aol 以及只采用 FB#1 電路的環(huán)路增益,。

圖 10.50 FB#1 AC 電路分析:CMOS RRO

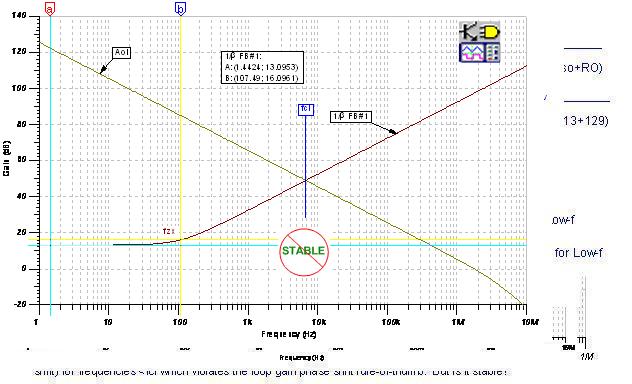

FB#1 1/b的結(jié)果標示在圖?10.51 中的?OPA734 Aol 曲線上,。在環(huán)路增益為零的 fcl 處,我們發(fā)現(xiàn),,接近速率為 40dB/decade:

[(Aol 曲線上的 –20dB/decade) – (FB#1 1/??曲線上的?+20dB/decade )= –40dB/decade 接近速率)]

為此,,接近速率的歷史數(shù)據(jù)表明了存在不穩(wěn)定性,。而且,,我們對 FB#1 的分析是基于 zero、fzx = 183.57Hz,,低頻 1/? = 13.09dB 的情況,。從圖 10.51 中可以看出,我們的一階分析準確推算出了 FB#1 1/b的數(shù)值,。

圖 10.51 FB#1 1/b 曲線:CMOS RRO

圖 10.52 FB#1 環(huán)路增益分析:CMOS RRO

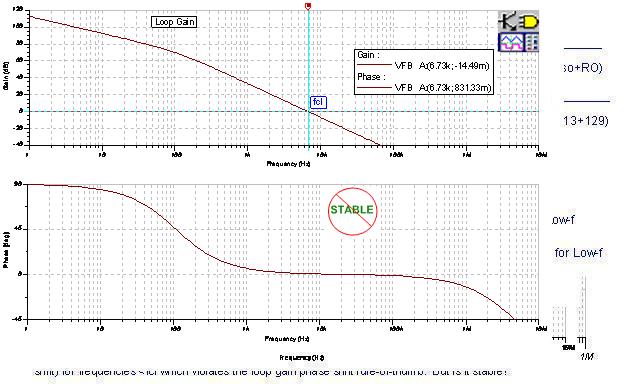

從圖 10.52 中我們發(fā)現(xiàn),,只配置 FB#1 的電路環(huán)路增益分析顯示,在環(huán)路增益為零的 fcl 處,,相位裕度接近零,。這樣,就明確證實了電路的不穩(wěn)定性,。通過觀察圖 10.51 中 Aol 曲線上的 FB#1 1/b標繪點,,可推算出環(huán)路增益曲線上的極點和零點。

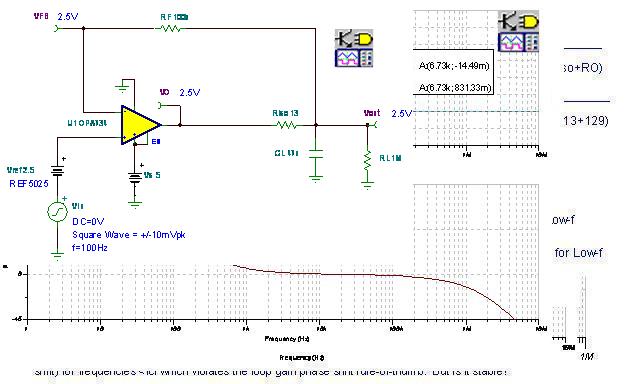

圖 10.53 FB#1 瞬態(tài)穩(wěn)定性測試電路:CMOS RRO

如果我們有任何疑問,,或如果只采用 FB#1 構(gòu)建參考緩沖電路,,此時,我們可運用圖 10.53 中的電路,,進行實際的瞬態(tài)穩(wěn)定性測試,。