引 言

近年來,嵌入式圖像采集技術(shù)得到快速發(fā)展,但由于嵌入式系統(tǒng)的處理、傳輸和存儲數(shù)據(jù)的資源有限,常成為系統(tǒng)采集速度的瓶頸,很難實現(xiàn)高速穩(wěn)定的采集。

SoPC" title="SoPC">SoPC是近幾年興起的一種用于嵌入式開發(fā)的片上系統(tǒng)可編程技術(shù),SoPC基于FPGA芯片,將處理器、存儲器、I/O口等模塊集成在一起,完成整個系統(tǒng)的主要邏輯功能,具有設(shè)計靈活、可剪裁、可擴充、可升級及軟、硬件在系統(tǒng)可編程的功能。由于SoPC平臺可以擁有微處理器系統(tǒng)豐富的軟件資源和出色的人機交互能力,同時又具備FPGA系統(tǒng)的快速硬件邏輯特性,實現(xiàn)了軟件系統(tǒng)和硬件系統(tǒng)的互補,因此發(fā)展前景非常廣闊,被認(rèn)為是未來嵌入式系統(tǒng)發(fā)展的方向。

在此試圖設(shè)計一種基于SoPC的自感知圖像采集系統(tǒng),使其能夠應(yīng)用于低成本、低功耗的微型嵌入式圖像監(jiān)控和采集系統(tǒng),以期在更多適合的應(yīng)用場合替代傳統(tǒng)基于PC的圖像監(jiān)控方案。在已見文獻報道中,基于SoPC的圖像采集系統(tǒng)設(shè)計大多只是把采集的數(shù)據(jù)緩沖在SDRAM或SRAM中,有些文獻則進一步提出將緩沖后數(shù)據(jù)直接通過并口傳輸給主控芯片,有的方案則是由USB接口或以太網(wǎng)接口輸出主機,另外有的文獻則提出直接將數(shù)據(jù)存儲到CF卡或硬盤中,而在SoPC系統(tǒng)直接實現(xiàn)SD卡的圖像采集數(shù)據(jù)文件存儲在國內(nèi)還未見報道。

另外還提出了一種新的適合在FPGA硬件實現(xiàn)的快速運動檢測算法,并和圖像采集、SD卡圖像數(shù)據(jù)存儲接口電路集成在同一FPGA芯片內(nèi)部。在此這一圖像采集系統(tǒng)的結(jié)構(gòu)、工作原理以及系統(tǒng)設(shè)計等加以介紹。

1 系統(tǒng)結(jié)構(gòu)及工作原理

該系統(tǒng)選用的。FPGA芯片是Altera公司CycloneⅡ" title="CycloneⅡ">CycloneⅡ系列的EP2C35" title="EP2C35">EP2C35。該芯片具有35 000個邏輯單元、672個引腳、475個用戶自定義I/O接口、35個嵌入式乘法器和4個鎖相環(huán)。FPGA芯片外接美光公司型號為MT9M011" title="MT9M011">MT9M011的130萬像素的CIS(CMOS圖像傳感器,分辨率為640×480時60幀/s)、Hynix公司的型號為HY57V641620HG的SDRAM(4 Banks×1 M×16 b),以及用來圖像顯示驗證的液晶屏等。

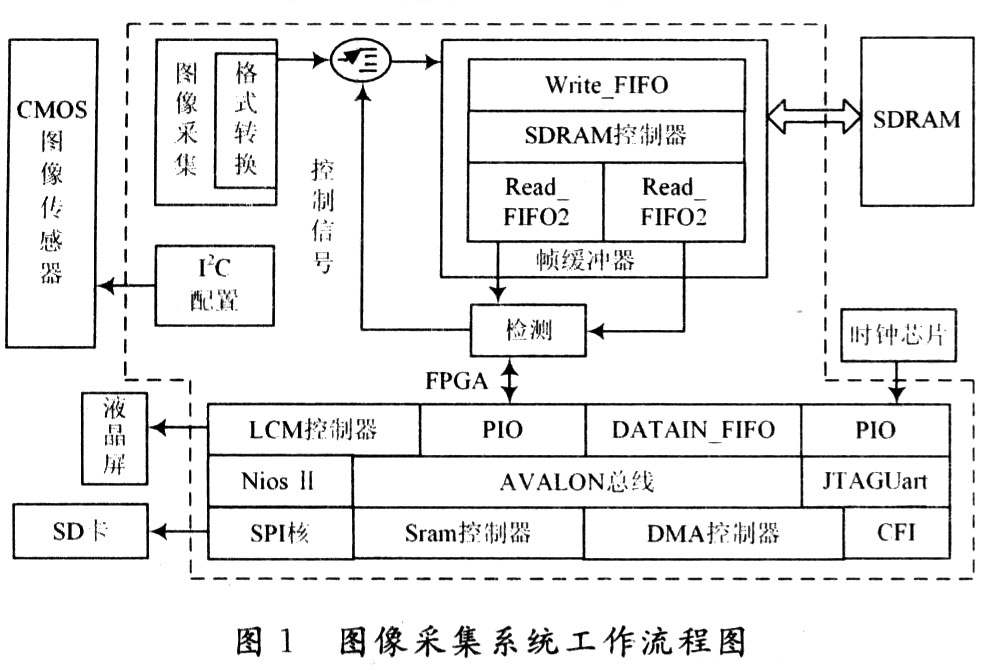

系統(tǒng)工作過程如圖1所示。CIS經(jīng)過I2C配置模塊的初始化后,輸出行場同步信號、像素時鐘和圖像數(shù)據(jù)。再將采集的數(shù)據(jù)轉(zhuǎn)換成RGB信號,幀緩沖模塊(Frame Buffer)每次將相鄰兩幀圖像數(shù)據(jù)寫入SDRAM,然后比較這兩幀圖像的差值,如果差值大于設(shè)定的閾值,就認(rèn)為檢測到了外界場景的運動,系統(tǒng)會自動將捕獲的圖像輸出到SD卡進行存儲。

2 系統(tǒng)模塊設(shè)計

2.1 采集模塊

2.1.1 CIS配置模塊

目前嵌入式采集系統(tǒng)大多仍采用模擬攝像頭,再經(jīng)過A/D轉(zhuǎn)換得到數(shù)字圖像信號。而相比較而言,CMOS圖像傳感器能夠直接輸出數(shù)字信號,而且其以體積小、功耗低、成本低的優(yōu)勢更適合應(yīng)用在嵌入式應(yīng)用領(lǐng)域,在該設(shè)計中采用130萬像素的CMOS圖像傳感器,其輸出圖像品質(zhì)已相當(dāng)接近CCD感應(yīng)器。MT9M011芯片內(nèi)部自帶時序發(fā)生器和ADC,使用時只需輸入一個時鐘信號(該設(shè)計采用25 MHz的時鐘信號),圖像數(shù)據(jù)便按行有效信號(LINE VALID)、場有效信號(FRAME VAL-ID)和像素時鐘(Pixel clock)時序關(guān)系一同發(fā)出。

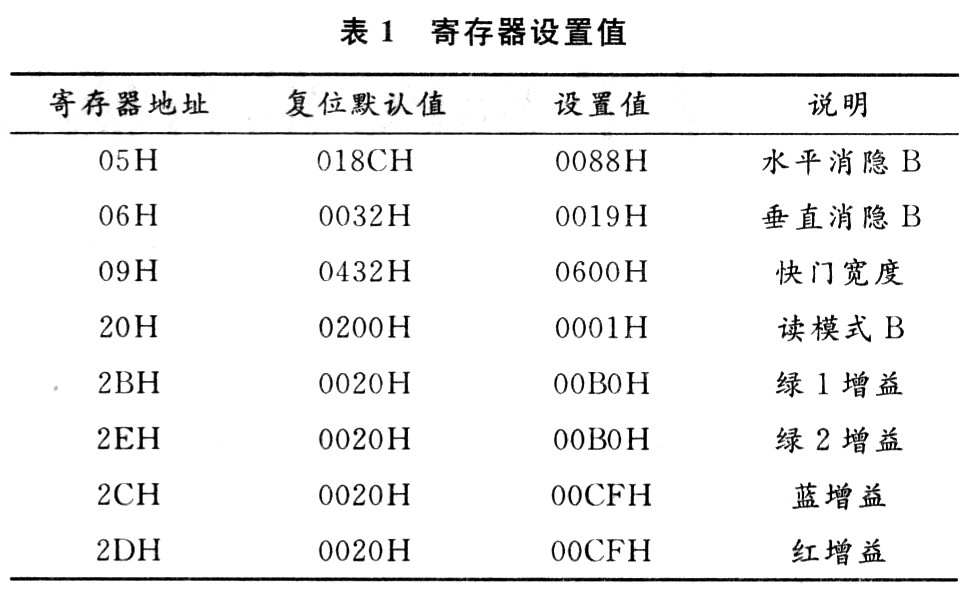

MT9M011上集成了I2C接口,其初始化由內(nèi)部的I2C總線來配置,通過編寫硬件描述語言來模擬I2C總線時序,從而配置各寄存器,其中,該設(shè)計需要配置的寄存器如表1所示。該模塊采用計數(shù)器建立一個狀態(tài)機,先寫器件地址,再寫寄存器地址,然后寫數(shù)據(jù)。另外還提供每幀圖像的控制信號以及圖像的行計數(shù)器和列計數(shù)器,為后續(xù)處理作準(zhǔn)備。

2.1.2 格式轉(zhuǎn)換模塊

MT9M011所輸出的圖像格式為Bayer格式,奇行由綠、紅像素交替構(gòu)成,偶行由藍、綠像素交替構(gòu)成。要想在顯示屏上顯示,必須將Bayer格式通過CFA插值濾波為RGB圖像數(shù)據(jù)。該模塊采用雙線性插值算法(BiIinear Interpolation),與高階B-spline和Cubic-spline等插補函數(shù)算法相比,圖像的像質(zhì)相差不大。但Bilincar的算法要簡單得多,不僅消耗的硬件資源相對要少,而且易于硬件實現(xiàn)。其算法原理是每個像素位置上缺少的彩色分量由3×3鄰域內(nèi)具有相同顏色分量的像素平均值獲得。

設(shè)計中調(diào)用移位寄存器IP核,將間隔為640的3個數(shù)作為輸出,這樣同時取到三行同一列的三個數(shù)據(jù),將這三個數(shù)據(jù)存入寄存器分別作兩次緩存延遲,從而得到3×3的鄰域數(shù)據(jù),根據(jù)配置模塊提供的行列計數(shù)的最低位來判斷該鄰域中間點所在行和列的奇偶性,從而計算出不同的RGB值。至此,每點圖像數(shù)據(jù)量變?yōu)樵瓉淼?倍。為了便于在液晶屏進行圖像顯示的驗證和SDRAM的緩存,在該模塊將RGB數(shù)據(jù)進行了抽樣處理,采用隔點隔行采樣使得每幀圖像分辨率降為320×240像素。

2.2 緩存模塊

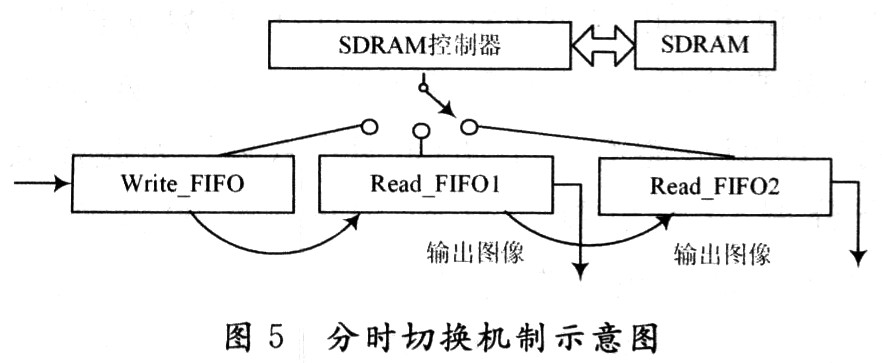

考慮到系統(tǒng)需要緩存的數(shù)據(jù)量較大,在各種隨機存儲器件中,SDRAM器件價格低、容量大、速度也較快,非常適合用于圖像采集系統(tǒng)。但SDRAM的控制邏輯比較復(fù)雜,要求有一個專門的控制器。 緩存模塊是由Sdram控制器,三個FIFO以及分時切換電路組成。SDRAM控制器負(fù)責(zé)外部SDRAM的讀/寫操作。三個FIFO中Write_FIFO用來數(shù)據(jù)輸入,Read_FIFO11和Read FIFO2用來數(shù)據(jù)輸出,容量均為512,位寬設(shè)為16 b。考慮到SDRAM只有16 b的位寬,輸入的RGB信號分別只取各自的最高5位。

2.2.1 SDRAM控制器

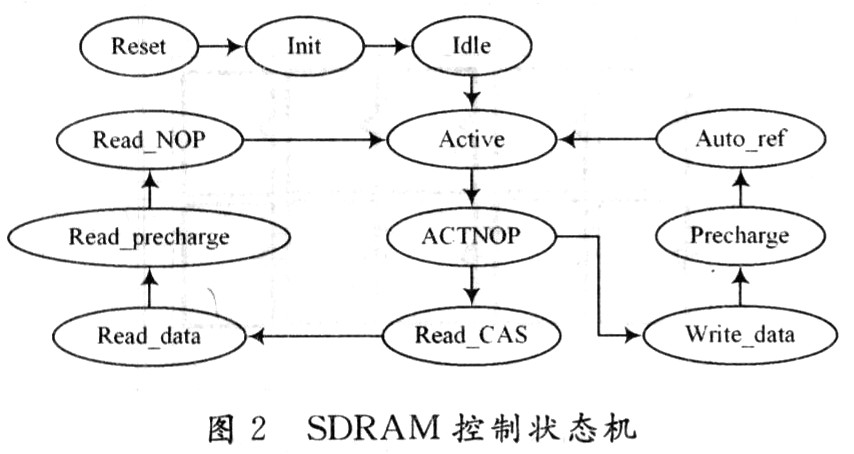

SDRAM控制器是由命令生成狀態(tài)機和數(shù)據(jù)通道兩個模塊構(gòu)成。系統(tǒng)的初始化、讀寫和刷新的控制采用有限狀態(tài)機來實現(xiàn)。如圖2所示,其狀態(tài)轉(zhuǎn)移系統(tǒng)復(fù)位后由復(fù)位狀態(tài)(Reset)進入初始化(Init)狀態(tài)。初始化包含初始化延時、初始化預(yù)充電、初始化刷新和初始化模式寄存器設(shè)置4個子狀態(tài)。初始化時將模式寄存器設(shè)置為長度為“1”的突發(fā)讀寫方式。設(shè)置完模式寄存器后,系統(tǒng)進入空閑狀態(tài)。當(dāng)3個FIFO半滿信號有效后。SDRAM控制器進入行激活狀態(tài),經(jīng)過兩個周期空操作(ActiveNOP)狀態(tài)后進入讀或者寫狀態(tài)。

讀數(shù)據(jù)過程由Read CAS狀態(tài)開始,經(jīng)過CAS延時,進入Read_Data狀態(tài)。突發(fā)計數(shù)器從Read_CAS態(tài)開始計數(shù),當(dāng)計數(shù)到讀寫請求的突發(fā)長度時,狀態(tài)機進入Read_Precharge狀態(tài)將打開的行關(guān)閉。在圖像采集中,用突發(fā)方式存完一行后,下一次存取的將是不同的行。根據(jù)這一特點,在SDRAM控制器中進行了優(yōu)化,在讀寫操作完成后執(zhí)行自動預(yù)充電,將打開的行關(guān)閉,將預(yù)充電的時間隱藏在數(shù)據(jù)訪問中,從而提高了SDRAM訪問的速度。寫操作過程由Write_Data和Write_Precharge狀態(tài)組成。當(dāng)激活一行完成后,進入到Write_Data狀態(tài),突發(fā)計數(shù)器對周期計數(shù),計數(shù)到突發(fā)長度時,狀態(tài)機進入Write_Precharge狀態(tài)將打開的行關(guān)閉。需要注意的是Read_Precharge和Write_Precharge后都需要兩個空操作才能再打開新的一行。

由于圖像數(shù)據(jù)流的連續(xù)性,每隔65 μs就有一行數(shù)據(jù)輸入,因此在SDRAM控制器中沒有必要再設(shè)置刷新計數(shù)器,而是在響應(yīng)圖像采集數(shù)據(jù)請求后將采集的一行數(shù)據(jù)存入SDRAM后對SDRAM進行刷新。由于HY57V641620HG要求在65 ms內(nèi)完成4 096次刷新,該設(shè)計驗證時按照每幀圖像(320×240)×(60幀/s)格式采集,需要在采集一行后完成[1/(60×240)/64]×4 096△4.4次刷新,因此需執(zhí)行5次刷新操作。在Write_Precharge完成后,如果寫操作是由FIFO半滿信號有效引起的,狀態(tài)機將進入自動刷新狀態(tài),完成5次刷新操作后回到Idle狀態(tài)。如圖3所示,數(shù)據(jù)通路模塊受OE信號的控制,使數(shù)據(jù)的進出和相應(yīng)的操作指令在時序上同步。OE為1時,數(shù)據(jù)可由DQ腳寫入SDRAM,OE為0時,數(shù)據(jù)可從SDRAM的DQ讀出。

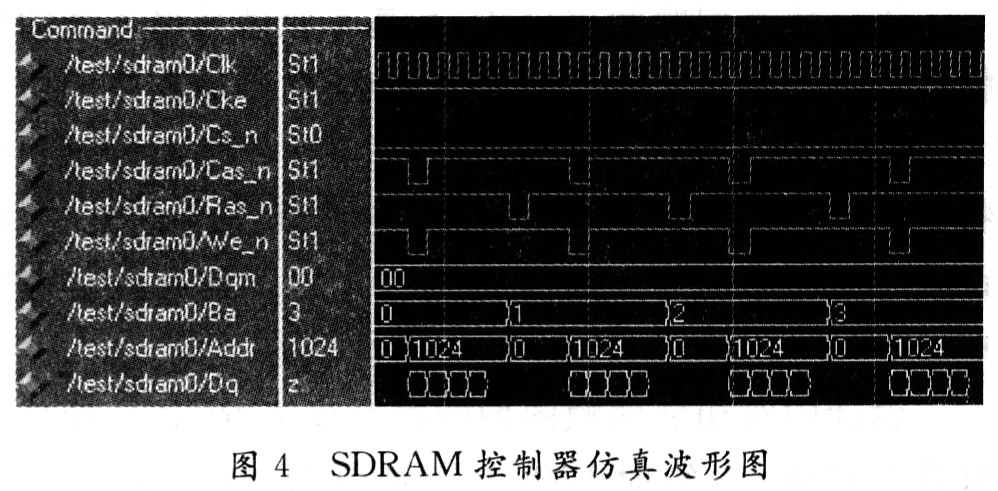

經(jīng)測試SDRAM控制器滿足設(shè)計要求,在Model-Sim6.0中其時序仿真波形圖如圖4所示。

2.2.2 幀存分時切換機制

Write_FIFO,Read_FIFO1和Read_FIFO2都是16 b位寬,而SDRAM只有16 b的數(shù)據(jù)位寬,三個FIFO都要訪問SDRAM,這就涉及到相互競爭的問題,在同一時刻只能有一個訪問SDRAM。為此需要設(shè)計一個分時切換機制。由于SDRAM的操作時鐘為100 MHz,而采集像素時鐘為25 MHz,經(jīng)過抽樣后時鐘頻率更是大大降低。在一次采集周期內(nèi),SDRAM完全可以和三個FIFO的接口輪流切換,從而不會影響采集的速度。

如圖5所示,其工作過程為:

(1)圖像經(jīng)格式轉(zhuǎn)換模塊輸出,寫入Write_FIFO的輸入端口。

(2)當(dāng)控制電路檢測到Write_FIFO中讀出端的數(shù)據(jù)量大于256(三個FIFO容量均為512 word)時,產(chǎn)生寫命令,并擁有寫互斥鎖。SDRAM控制器接到命令,以100 MHz時鐘將256個數(shù)據(jù)寫入SDRAM。

(3)Write_FIFO輸出256個數(shù)據(jù)后,讀出端的數(shù)據(jù)量小于256,并且由于Read_FIFO1中初始狀態(tài)的輸入端數(shù)據(jù)小于256,Read_FIFO1擁有讀互斥鎖,產(chǎn)生讀命令,SDRAM控制器接到命令,以100 MHz時鐘將256個數(shù)據(jù)讀出,并寫入Read_FIFO1。

(4)當(dāng)Read_FIFO1收到256個數(shù)據(jù),其輸入端數(shù)據(jù)大于256,并且由于Read_FIFO2中初始狀態(tài)的數(shù)據(jù)小于256,Read_FIFO2擁有讀互斥鎖,產(chǎn)生讀命令,SDRAM控制器將256個數(shù)據(jù)讀出,并寫入Read_FIFO2。

(5)這樣就完成了一次操作,之后就是循環(huán)操作。地址信號也是由控制電路產(chǎn)生,每經(jīng)過一次讀寫,地址增量為256,這樣就可以保持信號的連續(xù)性。

(6)Write_FIFO在一定周期內(nèi)向SDRAM中連續(xù)寫入兩幀連續(xù)圖像;Read+FIFO1根據(jù)SDRAM中的地址讀取其中的一幀圖像數(shù)據(jù);而Read_FIFO2讀取另一幀圖像數(shù)據(jù)。

通過這個機制,三個FIFO中始終都有數(shù)據(jù),不會發(fā)生讀空、寫滿情況,使得存儲器兩端的數(shù)據(jù)讀/寫方便,只要在write FIFO的輸入端和Read—FIF01、Read FIFO2的輸出端進行操作就行,在時鐘的上升沿將數(shù)據(jù)寫入或輸出,實現(xiàn)了異步方式。

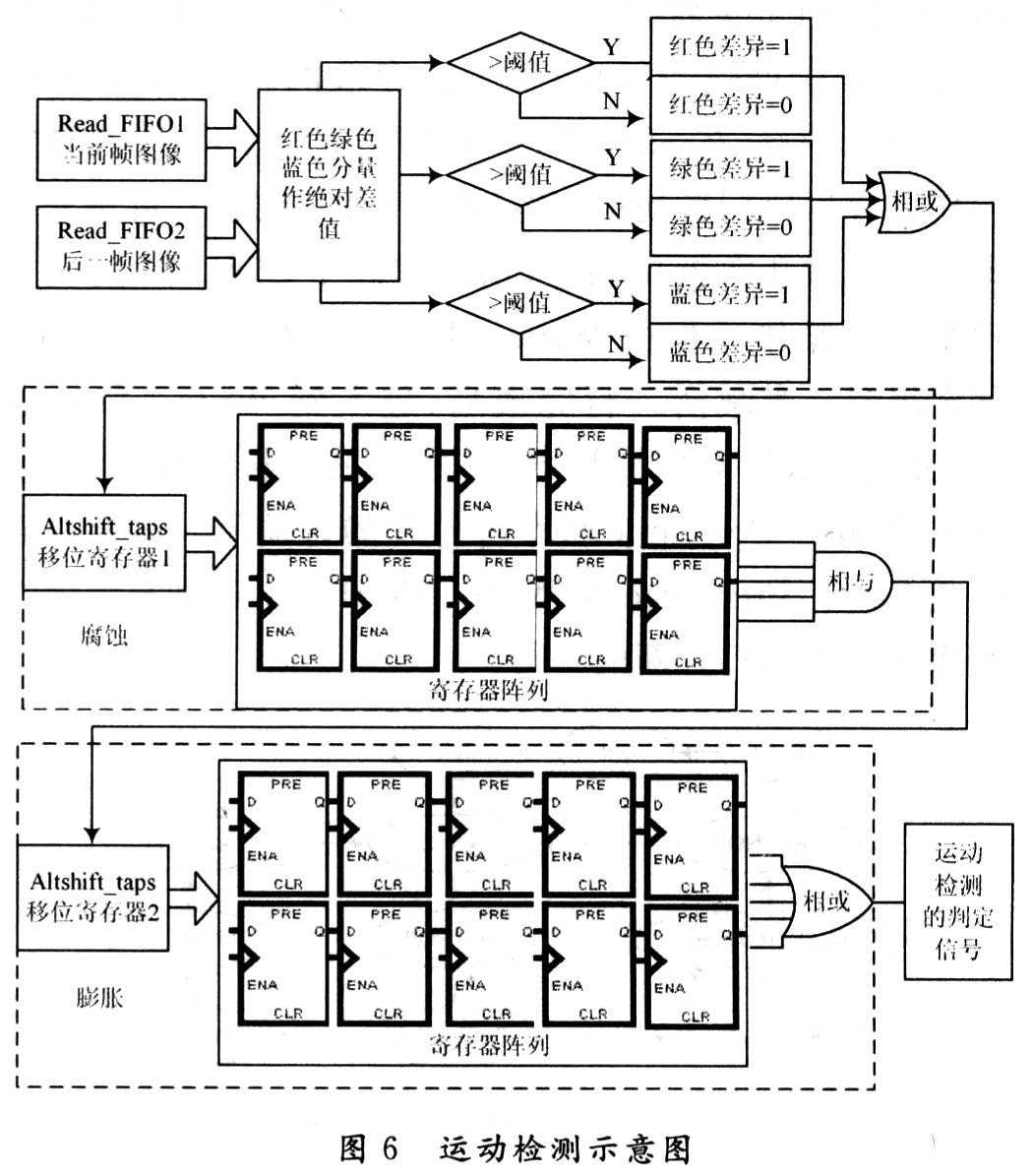

3 運動檢測模塊

該模塊采用幀間差分法,其基本原理是將連續(xù)的兩幀或幾幀的圖像對應(yīng)的像素值相減,在環(huán)境亮度變化不大的情況下,如果對應(yīng)像素值相差很小,則認(rèn)為此處景物是靜止的,如果圖像區(qū)域某處的像素值變化很大,可認(rèn)為這是由于圖像中運動物體引起的。其算法實現(xiàn)簡單,能夠適應(yīng)各種動態(tài)環(huán)境,穩(wěn)定性較好。

設(shè)計中對相鄰兩幀圖像的每個像素RGB分量分別取絕對差值。當(dāng)絕對差值大于閾值時(這里取經(jīng)驗值16),就認(rèn)為存在差異,如果做比較的兩個像素的RGB分量只要有一個分量有差異,則令此點的數(shù)值為1,這樣就得到一幅320×240像素大小的二值差值圖像。然后傳統(tǒng)處理方法是統(tǒng)計值為1的點的個數(shù),如果其數(shù)量超過預(yù)設(shè)值,就認(rèn)為兩幅圖像有差異。這種方法設(shè)計簡單,但是準(zhǔn)確率還不夠高,為此該設(shè)計提出了一種改進的算法,引入了圖像處理常用的兩種操作腐蝕和膨脹。腐蝕與膨脹是一對逆運算,如果先腐蝕再膨脹,便構(gòu)成了開運算。一般來說,開運算能夠去除孤立的小點,毛刺和小橋(即連通兩塊區(qū)域的小點)。而總的位置和形狀不變。

對上述二值圖像進行開運算處理,可以消除小顆粒的噪聲的干擾,從而盡可能降低誤判和漏判。

設(shè)計流程如圖6所示,通過調(diào)用ALTSHIFTTAPS IP核,并利用輸出TAPS,構(gòu)建一個11×11像素大小的圖塊作為結(jié)構(gòu)元素,然后腐蝕:

(1)用11×11的結(jié)構(gòu)元素,掃描圖像的每一個像素;

(2)用結(jié)構(gòu)元素與其覆蓋的二值圖像做“與”操作;

(3)如果都為1,結(jié)果圖像的該像素為1,否則為0。

接著再將上述結(jié)果作為第二個ALTSHIFTTAPS的輸入,再次構(gòu)建11×11個像素的結(jié)構(gòu)元素,然后進行膨脹處理:

(1)用11×ll的結(jié)構(gòu)元素,掃描圖像的每一個像素;

(2)用結(jié)構(gòu)元素與其覆蓋的二值圖像做“或”操作;

(3)如果都為0,結(jié)果圖像的該像素為0,否則為1。

最后得到運動判定信號DETECT,并用這個信號控制數(shù)據(jù)寫入過程,一旦判定信號為1,就啟動后續(xù)的圖像存儲過程。

4 SD卡圖像存儲模塊

(1)接口電路模塊。在各種存儲設(shè)備中,SD卡不僅小巧,而且功耗很低,另外市面上常見SD卡的容量可達到2 GB以上,因此非常適合用于對體積和功耗要求嚴(yán)格的嵌入式圖像存儲。該設(shè)計選用APACER公司的一款高速SD卡(傳輸速率為150X,容量4 GB)。為了增強系統(tǒng)的可擴展性,該設(shè)計在FPGA芯片中嵌入Altera公司新近推出的第二代高性能NiosⅡ軟核處理器,其處理能力超過200 MIPS,并在NiosⅡ中完成SD卡驅(qū)動程序設(shè)計。前端的采集緩存電路與NiosⅡ系統(tǒng)之間的數(shù)據(jù)和控制信號由定制的接口模塊完成。

定制IP核DATAIN_FIFO是在SoPC Builder環(huán)境下完成(如圖7所示),DATAIN_FIFO寫端口的時鐘信號、寫請求信號同步于SDRAM控制模塊的ReadFIFO1,而DATAIN_FIFO的讀端口的時鐘、讀請求信號則由CPU控制。以上信號除了waitrequest之外,都由Avalon交換結(jié)構(gòu)自動產(chǎn)生和控制。waitrequest信號可以直接連接到異步FIFO的rdempty輸出,當(dāng)FIFO讀空之后,waitrequest有效,插入等待周期,一直到從端口的數(shù)據(jù)準(zhǔn)備好才輸出readdata。開始和結(jié)束采集控制信號由DETEcT信號和DMA中斷信號決定,確保采集到的數(shù)據(jù)剛好為一幀320×240圖像。

由于NiosⅡ系統(tǒng)提供了成熟的SPI接口,所以設(shè)計中采用SPI總線協(xié)議模式來讀寫SD卡。因為MMC卡在復(fù)位階段要求SPI的時鐘頻率要小于等于400 kHz,為了提高讀寫速度,本設(shè)計設(shè)計的接口不再兼容MMC卡,其設(shè)置SPI的SCK引腳的輸出頻率在數(shù)據(jù)傳輸時設(shè)為25 MHz。

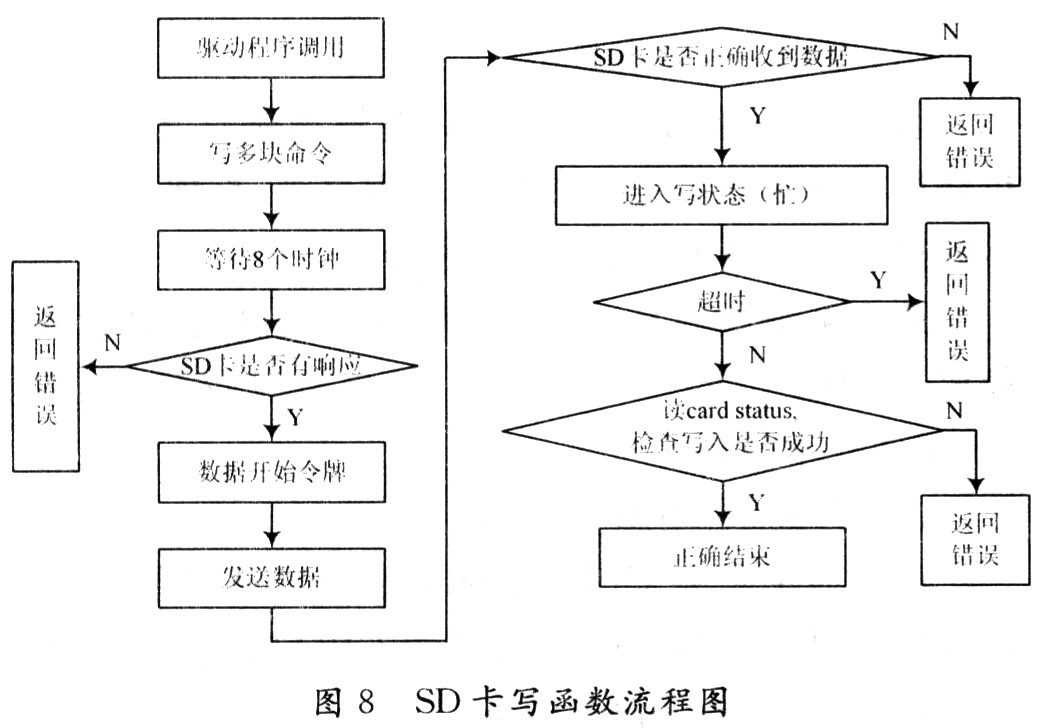

(2)BMP圖像文件創(chuàng)建程序。為提高程序運行速度。并考慮到該系統(tǒng)的實際需要,程序只實現(xiàn)了寫B(tài)MP圖像文件功能。程序主要由SD卡操作驅(qū)動接口函數(shù)和文件系統(tǒng)層組成。

驅(qū)動函數(shù)目的是為文件系統(tǒng)層提供所需的SD卡初始化函數(shù)和SD卡寫多塊數(shù)據(jù)函數(shù)。圖8是SD卡寫函數(shù)流程圖示意圖。當(dāng)寫函數(shù)接收到主程序的寫文件指令后,就向SD卡發(fā)送多塊寫命令,卡將發(fā)送給主機一個應(yīng)答令牌,并且等待主機發(fā)送一個發(fā)送數(shù)據(jù)塊來,當(dāng)應(yīng)答R1為0時,說明可以發(fā)送數(shù)據(jù),塊大小設(shè)置為512 B。數(shù)據(jù)塊之后附有16位的CRC校驗,因為CRC校驗計算占用了很大部分發(fā)送的時間,該系統(tǒng)采用自定義用戶指令對這部分進行了加速處理。

要使寫入SD卡的數(shù)據(jù)在裝有Windows或Linux操作系統(tǒng)的上位機中得到正確訪問,需要在SD卡上創(chuàng)建它們支持的文件系統(tǒng)。考慮到FAT12目前已經(jīng)很少使用,在此設(shè)計的文件系統(tǒng)只支持FAT16和FAT32。并且將整個卡作為一個分區(qū)處理。

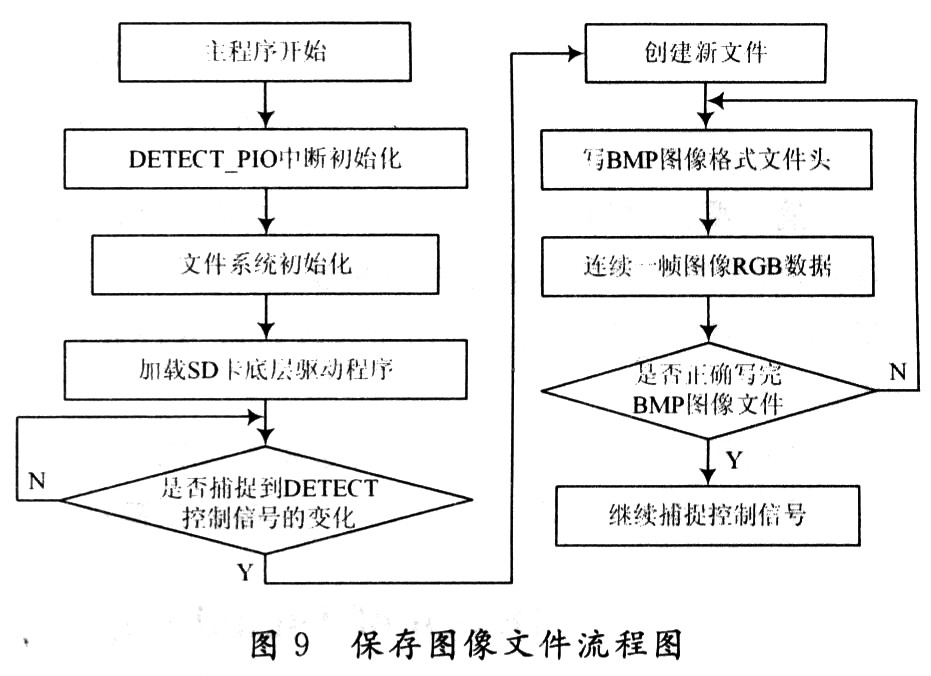

圖9是系統(tǒng)的軟件工作主要流程圖。在主程序中,系統(tǒng)啟動后,先進行初始化操作,包括中斷初始化、文件系統(tǒng)初始化和SD卡底層驅(qū)動的初始化。隨后系統(tǒng)進入主循環(huán)等待狀態(tài),一旦檢測到DETECT_PIO電平的變化就暫停SDRAM數(shù)據(jù)寫入,以防SDRAM緩存的圖像數(shù)據(jù)被覆蓋,同時根據(jù)當(dāng)前的時間創(chuàng)建一個BMP格式的文件,然后往里填寫文件頭和文件信息頭,隨后連續(xù)寫一幀RGB數(shù)據(jù)。文件創(chuàng)建完畢后系統(tǒng)繼續(xù)處于檢測等待狀態(tài),并恢復(fù)SDRAM數(shù)據(jù)寫入。

5 系統(tǒng)評價

該設(shè)計在自制核心實驗板上(見圖10)進行了軟、硬件仿真和調(diào)試,調(diào)試環(huán)境參數(shù)設(shè)定如下:采集時鐘頻率為25 MHz,NiosⅡ時鐘頻率為100 MHz、每幀圖像大小為320×240像素。調(diào)試結(jié)果如下:系統(tǒng)采集速度在60幀/s左右。對五米之內(nèi)場景動態(tài)變化的響應(yīng)時間在5 ms左右,SD卡保存單幀圖像時間約為9 s(每幀圖像數(shù)據(jù)量是153 600 B),連續(xù)工作一個星期無任何故障發(fā)生。結(jié)果表明該系統(tǒng)圖像采集和處理速度超過一般的以軟件實現(xiàn)為主的嵌入式圖像采集方案(如ARM處理器系統(tǒng))。由于核心處理器采用單芯片方案,采集系統(tǒng)比較穩(wěn)定,同時其功耗大大低于多芯片方案。

6 結(jié) 語

在此提出一種基于SoPC技術(shù)的圖像檢測、采集和儲存的一體化單芯片控制新型系統(tǒng)集成方案,并實現(xiàn)了原型系統(tǒng),該系統(tǒng)的主要特點是處理速度快、功耗低、穩(wěn)定可靠。

該設(shè)計可以在進一步工作中移植嵌入式操作系統(tǒng)μCLinux,以實現(xiàn)復(fù)雜的多任務(wù)操作。因此該設(shè)計既可作為獨立的解決方案應(yīng)用于便攜式原位觀測系統(tǒng)中,同時以其良好的擴展性,也可作為一個子系統(tǒng)應(yīng)用于大型圖像處理系統(tǒng)的前端部分。