與其它存儲器" title="存儲器">存儲器技術(shù)相比,DDR" title="DDR">DDRSDRAM" title="SDRAM">SDRAM具有出眾性能、很低的功耗以及更具競爭力的成本。可與以前的SDRAM技術(shù)相比,DDRx存儲器需要一個更復(fù)雜的電源管理新架構(gòu)。本文探討了DDR電源管理架構(gòu)的理想選擇。

雙PWM控制器

現(xiàn)在市面上有各種DDR電源IC,如集成MOSFET的ML6553/4/5、適用于大功率系統(tǒng)的FAN5066和FAN5068、DDRx和先進配置及電源接口(ACPI)的組合等。另一種器件FAN5236是專門為DDRx存儲器系統(tǒng)的一體化供電要求而設(shè)計的器件,這個單片IC集成了一個VDDQ開關(guān)控制器,一個VTT開關(guān)控制器和一個VREF線性緩沖器。

VDDQ開關(guān)可以輸出5~24V范圍內(nèi)的任何電壓,但VTT的開關(guān)則不同,它由VDDQ電源供電,并與VDDQ開關(guān)同步動作。這兩個開關(guān)的輸出都可在0。9~5。5V范圍內(nèi)變化。由于VDDQ總線信號線的驅(qū)動電壓為2。5V(DDR)或1。8V電壓(DDR2),VTT的端接電壓為1。25V(DDR)或0。9V(DDR2),所以在VTT和VDDQ之間存在一定程度的功率循環(huán)。將VTT與VDDQ分離,就可以將其間的功率循環(huán)以及由此產(chǎn)生的損耗降到最低。VTT開關(guān)在待機模式下也可以關(guān)閉。

雙PWM控制器的應(yīng)用

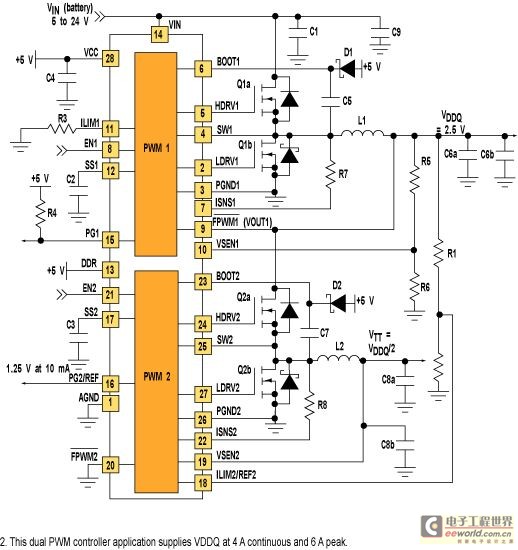

圖2中給出了一個連續(xù)電流為4A、峰值電流為6A的VDDQ典型應(yīng)用,表中也列出了其材料清單。請注意,在圖2中,外部的矩形代表FAN5236雙脈寬調(diào)制器(PWM),其中標有PWM1和PWM2的小矩形代表IC內(nèi)部的兩個轉(zhuǎn)換開關(guān)。另外還需要注意的是,在表中FAN5236被稱為DDR控制器,元件名為U1。可以很容易地對這個電路進行修改,通過分壓器R5/R6,將VDDQ設(shè)置為1.8V,將VTT設(shè)置到0.9V,以適用DDR2應(yīng)用。

設(shè)置輸出電壓FAN5236PWM控制器的內(nèi)部基準電壓為0。9V,其輸出由分壓器分壓到VSEN腳(R5和R6),因此輸出電壓為:0。9V/R6=(VDDQ×0。9V)/R5。