與其它存儲(chǔ)器技術(shù)相比,DDRSDRAM具有出眾性能、很低的功耗以及更具競(jìng)爭(zhēng)力的成本。可與以前的SDRAM技術(shù)相比,DDRx存儲(chǔ)器需要一個(gè)更復(fù)雜的電源管理新架構(gòu)。本文探討了DDR電源管理架構(gòu)的理想選擇。

與其它存儲(chǔ)器技術(shù)相比,DDRSDRAM具有出眾性能、很低的功耗以及更具競(jìng)爭(zhēng)力的成本,目前已普遍應(yīng)用在桌面電腦和便攜計(jì)算應(yīng)用中。

最初,DDR的數(shù)據(jù)傳輸速率只有266MBps,而普通SDRAM的速率只有133MBps。隨后,DDR數(shù)據(jù)傳輸速率增加400MBps。第二代DDR,即2004年初登場(chǎng)的DDR2,將數(shù)據(jù)速率從400MBps提高到667MBps,而同時(shí)還進(jìn)一步降低了功耗。

目前,第一代DDR仍在存儲(chǔ)器市場(chǎng)中占主流地位,但DDR2正在快速地?fù)尩檬袌?chǎng)份額,并可望在2005年底兩者的市場(chǎng)份額將出現(xiàn)轉(zhuǎn)折點(diǎn)。但不論DDR內(nèi)存多么受歡迎,與以前的SDRAM技術(shù)相比,DDRx存儲(chǔ)器需要一個(gè)更復(fù)雜的電源管理新架構(gòu)。

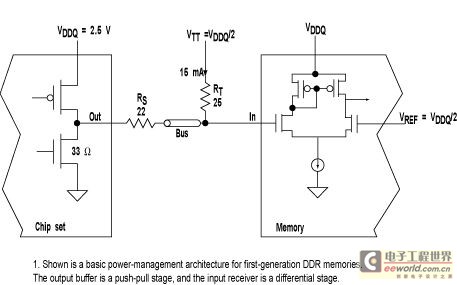

DDR電源管理架構(gòu)圖1給出了第一代DDR存儲(chǔ)器的基本電源管理架構(gòu)。在DDR存儲(chǔ)器中,輸出緩沖器是推挽級(jí),而輸入吸收器是差動(dòng)級(jí),這就需要一個(gè)參考電壓的偏置中點(diǎn)VREF,從而需要一個(gè)能提供和吸收電流的輸入電壓終端。

最新的特性(提供和吸收電流)使DDRVTT終端與PC主板上的其它終端有所不同。在連接CPU和存儲(chǔ)器通道集線器(MCH)的前端系統(tǒng)總線中,它們的差別特別值得注意。由于該終端接到正電壓上,因而只要求具有吸收電流的能力,所以DDRVTT終端不能夠重復(fù)利用或適應(yīng)以前的VTT終端,而是需要新的電源設(shè)計(jì)。

第一代DDR存儲(chǔ)器的邏輯門(mén)由2。5V電源供電。在芯片組任何輸出緩沖器與存儲(chǔ)器模塊相應(yīng)的輸入吸收器之間,一般可以找到需要正確端接電阻RT和RS的一條走線或者走線分支(參見(jiàn)圖1)。當(dāng)考慮所有阻抗(包括輸出緩沖器的阻抗)時(shí),每個(gè)端接線都可吸收或提供±16。2mA的電流。對(duì)于發(fā)送器和吸收器之間走線比較長(zhǎng)的系統(tǒng),必須在走線兩端端接電阻,以使電流增加一倍。

DDR邏輯所要求的2。5VVDDQ的誤差為+200mV。為保持噪聲容限,VTT必須以±3%的精度跟隨VDDQ變化,且必須等于VDDQ/2,大約為1。25V,精度±3%。最終VREF必須與VTT相差+40mV。這些跟隨要求以及VTT必須能夠提供和吸收電流的要求,給DDR存儲(chǔ)器的供電帶來(lái)了獨(dú)特挑戰(zhàn)。

最壞情況下的電流消耗

VTT終端:假設(shè)128MB存儲(chǔ)器系統(tǒng)有128位總線、8個(gè)數(shù)據(jù)選通、8個(gè)屏蔽位、8個(gè)VCC位、40條地址線(兩組20條地址線),則共有192個(gè)信號(hào)/電源線。每條線消耗電流16。2mA,則最大電流消耗為192×16。2mA=3。11A。

VDDQ電壓峰值:VTT吸收電流時(shí)VDDQ供應(yīng)電流,因此VDDQ的電流是單向的,因此其最大電流就等于VTT的最大電流3。11A。。

平均功耗:一個(gè)128MB存儲(chǔ)器模塊一般由8個(gè)128Mb的器件組成,平均消耗990mW功率,除去VTT終端消耗的功率,IDDQ從VDDQ抽取的平均電流為IDDQ=PDDQ/VDDQ=990mW/2。5V=0。396A。

同樣,終端電阻消耗的平均功率PTT為660mW,從VTT抽取的電流ITT為ITT=PTT/VTT=660mW/1。25V=0。528A。