0 引言

當(dāng)今的高速中央處理器(CPU)在提供極高的性能的同時(shí),對(duì)于其供電電源的各項(xiàng)指標(biāo)的要求也達(dá)到了前所未有的高度。更高速的CPU需要更低的核心電壓,卻需要更大的功率,因此供電電路必須提供極大的電流。更好的解決核心電壓的供電問(wèn)題已經(jīng)成為電壓變換模塊和PC主板設(shè)計(jì)者面臨的極大挑戰(zhàn)。

l Intel相關(guān)規(guī)范對(duì)CPU核心電壓的要求

Intel早期的CPU,如Pentium 2、Pentium 3都遵循Intel的VRM(Voltage Regulation Module)8.1~8.4電源規(guī)范,其最大輸出電流值為22.6A。Tualatin核心的Pcntium 3及Celeron CPU則開(kāi)始引入VRM8.5標(biāo)準(zhǔn),其最大輸出電流值為28AIntel在推出Willamette、NorthWood核心的Pentium4時(shí)引入了VRM9.O標(biāo)準(zhǔn),其規(guī)定的最大輸出電流為70A。隨著Prescott核心Pentium 4的推出,VRM規(guī)范也更新到了VRD(Voltage Regulator Down)10.O,電流最大值也達(dá)到了91A。為了配合更高頻率更高性能的CPU,200

5年4月Intel推出了VRDl0.1規(guī)范,對(duì)LGA775 Socket的CPU的供電電源的規(guī)格指標(biāo)進(jìn)行了細(xì)致的規(guī)定,這是對(duì)臺(tái)式機(jī)CPU供電電源要求極高的電源規(guī)范,其要求列舉如下:

(1)連續(xù)負(fù)載電流(ICCTDC)為115A;

(2)最大輸出電流(ICCMAX)為125A;

(3)輸出的電壓值由VID[5:0]指定,范圍為O.837 5~1.6V.以0.0125V為步進(jìn);

(4)負(fù)載線斜率(loadline slope)阻抗R0為1.00mΩ;

(5)最大電壓紋波VRIPPLE為±5mV;

(6)最大電壓上沖波峰VOS_MAX為50mv,其最長(zhǎng)持續(xù)時(shí)間為25μs。

這里只是列舉了最為重要的幾個(gè)規(guī)定,VRDl0.1規(guī)范還有其他的許多內(nèi)容,限于篇幅,這罩不再一一列舉。由上述內(nèi)容可見(jiàn),高性能CPU對(duì)于供電電源電路的輸出功耗需求越來(lái)越大,在VRDl0.1中要求輸出功耗甚至高達(dá)170W以上。同時(shí)對(duì)于電壓的精確性和穩(wěn)定性的要求也達(dá)到了非常苛刻的地步,在大功率、大電流的情況下還要保持非常穩(wěn)定和精準(zhǔn)的負(fù)載線斜率。在VRDl0.O之前,CPU核心電壓供電電路一般都是由三相或兩相的PWM控制方式,這種方式已經(jīng)無(wú)法滿足100A以上的大電流需求。本文的設(shè)計(jì)使用了4相PWM控制,可以滿足VRDl0.1的嚴(yán)格要求,以下詳細(xì)敘述之。

2 大功率CPU核心電壓電路的設(shè)計(jì)

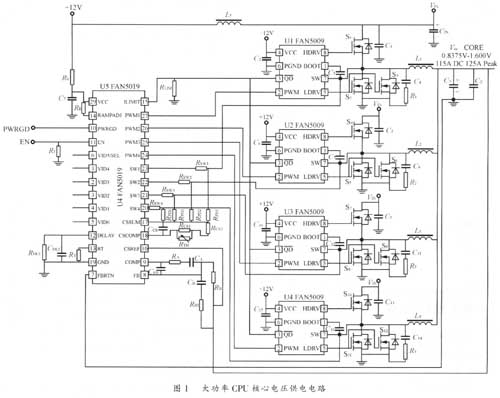

圖l所示即為本文提出的滿足VRD101要求的大功率CPU核心電壓供電電路。它使用了仙童(Fairchild)公司的FAN50192—4相PWM電源控制器做為豐控制芯片。FAN5019控制4個(gè)Fairchild的FAN5009 MOSFET驅(qū)動(dòng)器。FAN5009驅(qū)動(dòng)開(kāi)關(guān)外接的高端和低端M0SFET,然后通過(guò)電感與電容器件的充、放電對(duì)VCCCORE進(jìn)行供電。

FAN5019是一款多相(最高支持4相)DC/DC控制器,專為產(chǎn)生高電流、低電壓的CPU核心電壓而設(shè)計(jì)。本設(shè)計(jì)中,它以并行的方式同時(shí)驅(qū)動(dòng)四個(gè)PWM通道,而且以交叉開(kāi)關(guān)的方式來(lái)減少輸入、輸出的紋波電流,這樣可以達(dá)到減少外圍器件,降低成本的目的。FAN5019采用了溫度補(bǔ)償電感器電流檢測(cè)技術(shù),來(lái)滿足VRDl0.1規(guī)則的負(fù)載線技術(shù)要求,而一般的PWM控制器都是采用RDS(ON)或感應(yīng)電阻器來(lái)測(cè)量電流和設(shè)置負(fù)載線,精度無(wú)法滿足要求。如圖1所示,F(xiàn)AN5019的VID[5:0]輸入與VRDl0.l規(guī)范定義完全一致,可以控制輸出0.8375~1.600V以12.5mV步進(jìn)的電壓,另外它還具有短路保護(hù),電流上限可調(diào),過(guò)壓保護(hù)等增加安全可靠性的技術(shù)。FAN5019向每個(gè)FAN5009送出PWM控制信號(hào),而FAN5009通過(guò)內(nèi)部電路將其轉(zhuǎn)換為可以正確驅(qū)動(dòng)高端和低端M0SFET的信號(hào)輸出。FAN5009可以同時(shí)驅(qū)動(dòng)高端和低端的MOSFET,其內(nèi)置啟動(dòng)二極管,因此無(wú)需在外圍電路中再添加二極管。

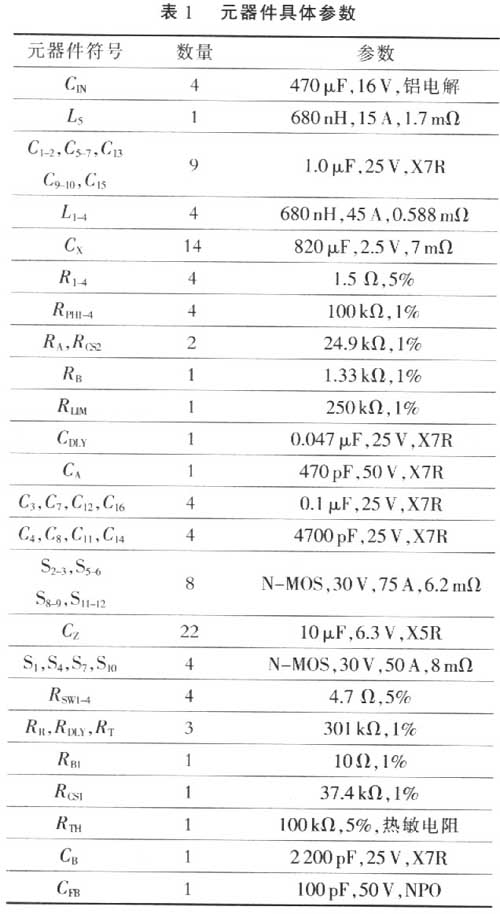

本設(shè)計(jì)的輸入電壓VIN為12V,額定輸出電壓VVID為1.500V,占空比D(Duty Cycle)為O.125,負(fù)載線斜率阻抗R0為1.OmΩ,ICCTDC大于115A,ICCMAX為125A,最大輸出功耗為172.5W,最大電壓紋波VRRIPLE為±5mV,每相的開(kāi)關(guān)頻率fSW設(shè)定為228kHz。外圍元器什的具體參數(shù)如表l所列。

3 重要器件的選擇與布局布線規(guī)則

3.1 功率MOSFET的選擇

在選擇高端和低端功率MOSFET時(shí),主要考慮如下幾個(gè)方面:

(1)較低的RDS(ON),應(yīng)小于1OmΩ;

(2)盡可能高的導(dǎo)通電流:

(3)額定VDDS應(yīng)該大于15V。

在選擇低端MOSFET時(shí),RDS(ON)是最重要的考慮因素,因?yàn)樵谡9ぷ鲿r(shí),低端的MOSFET導(dǎo)通時(shí)間較長(zhǎng),因而功率消耗較大。因此在本設(shè)計(jì)中.每相在低端都使用了兩個(gè)FDD6682,其導(dǎo)通電流為75A,在VGS為10V時(shí)(正常工作狀態(tài)),RDS(ON),為6.2mΩ,額定VDDS為30V。對(duì)高端的MOSFET而言,門電荷Qg也是重要的考慮因素,要求其越低越好,否則會(huì)影響開(kāi)關(guān)速度進(jìn)而影響功耗。因此在每相高端都使用了一個(gè)FDD6696,其導(dǎo)通電流為50A,在VGS為lOV時(shí),RDS(ON)為8.0mΩ,額定VDDS為30V,門電荷為17nC,可以完令滿足沒(méi)計(jì)的要求。

3.2 輸出電感的選擇

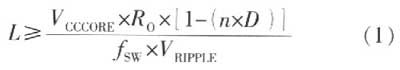

輸出電感有3個(gè)主要指標(biāo),電感量L、額定電流值Irated和直流電阻RDCR,電感的額定電流值是電感線圈的飽和電流或過(guò)熱電流中較小的值。為使4相的輸出電流總量大于等于125A,每相的輸出電感額定電流應(yīng)大于等于31.25A。電感量的取值與工作頻率,紋波電流等因素都有一定的相關(guān),可以根據(jù)式(1)進(jìn)行計(jì)算:

式中:VCCCORE為輸出電壓;RO負(fù)載線斜率電阻;n為相數(shù);D為每一相的占空比;fSW開(kāi)關(guān)頻率;VRIPPLE為最大紋波電壓。

根據(jù)前面提到的設(shè)計(jì)參數(shù),可以計(jì)算得輸出電感的電感量應(yīng)該大于658nH。電感的直流電阻RDCR最好取值在R0的O.5倍到l倍之間,這是因?yàn)椋姼械腞DCR會(huì)用來(lái)監(jiān)測(cè)每相的輸出電流,如果RDCR值太小,會(huì)引起較大的測(cè)量誤差,影響設(shè)計(jì)的正常運(yùn)行,如果RDCR值太大,又會(huì)造成較大的能量損耗,影響設(shè)計(jì)的效率。因此,我們選用了線藝電子(Coilcraft)公司的電感SER2009—681ML,其額定電流為45A,電感量為680 nH,直流電阻為0.588mΩ,完全滿足設(shè)計(jì)對(duì)輸出電感的要求。

3.3 布局布線

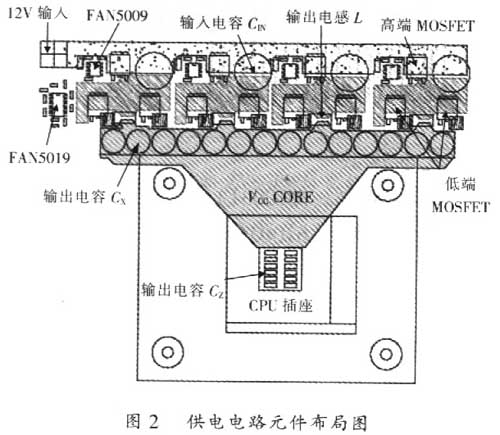

布局布線對(duì)電路穩(wěn)定性、精確性的最終實(shí)現(xiàn)起著至關(guān)重要的作用,圖2是本設(shè)計(jì)在4層PCB上的布局圖,遵循如下的布局布線規(guī)則。

(1)輸入電容CIN必須放置在盡量靠近高端MOSFET的漏極,其陰極應(yīng)該放置在靠近低端MOSFET的源極,且每柑都應(yīng)該至少放置一個(gè)輸入電容。

(2)每相的FAN5009驅(qū)動(dòng)器應(yīng)該靠近各相的MOSFET。

(3)FAN5019應(yīng)該放置在靠近COUT但是遠(yuǎn)離CIN的陰極和低端MOSFFT的源極處。其周圍的元件應(yīng)該放置在盡量靠近它的位置,并且它們與FAN5019之間應(yīng)該用盡量粗的線來(lái)連接。FB和CSSUM兩個(gè)引腳的線是最為重要的,應(yīng)盡量短,且遠(yuǎn)離其他線。FAN5019及其周圍的元件應(yīng)該使用獨(dú)立的模擬地平面(包括其底下的PCB電源層平面)來(lái)接地。

(4)因?yàn)樵O(shè)計(jì)的電流非常大,因此在PCB各層之間傳輸電流時(shí)要盡可能多州穿孔以減小電流通路的電阻和電感效應(yīng),粗略的估算方法是1mm直徑的穿孔可以允許3A電流。穿孔還可以幫助IC散熱。

(5)輸出電容CX及CZ應(yīng)該盡町能靠近CPU的插座或CPU引腳。

(6)供電電路相關(guān)的PCR走線都應(yīng)該盡可能的寬,并且保持各自間距,以避免EMI問(wèn)題。

(7)布局應(yīng)合理緊湊,并且充分考慮散熱問(wèn)題。

4 實(shí)驗(yàn)結(jié)果

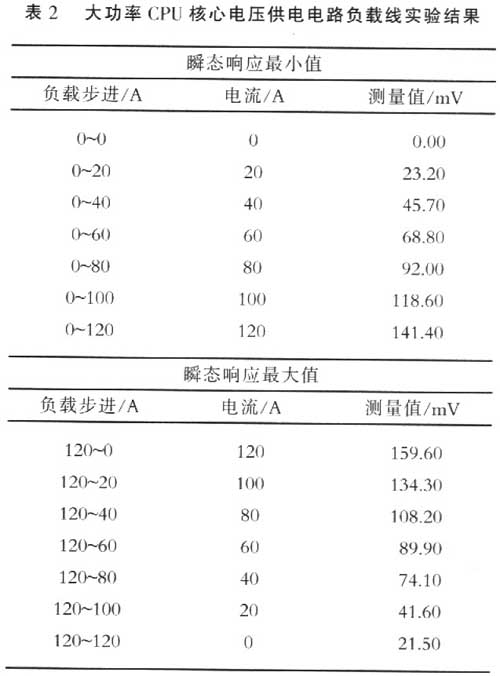

本文介紹的大功率CPU供電電路經(jīng)過(guò)PCB樣板制作和調(diào)試,已經(jīng)達(dá)到正常工作的要求,表2為實(shí)驗(yàn)測(cè)量樣板的輸出電壓負(fù)載線的結(jié)果。實(shí)驗(yàn)使用了Intel公司的Voltage Transient Test Tool進(jìn)行電壓瞬態(tài)響應(yīng)的測(cè)試,測(cè)試節(jié)點(diǎn)為L(zhǎng)GA775CPU插座的U27與V27引腳,VCCOORE=1.500V。從實(shí)驗(yàn)結(jié)果可見(jiàn)此電路的設(shè)計(jì)可以達(dá)到VRDlO.1要求。

5 結(jié)語(yǔ)

應(yīng)用FAN5019設(shè)計(jì)的大功率CPU核心電壓供電電路,不僅可以用于高性能臺(tái)式機(jī)CPU,也可以用于工作站、服務(wù)器的CPU供電,因此具有相當(dāng)?shù)膶?shí)用價(jià)值。