在FPGA系統(tǒng)中,實(shí)現(xiàn)對(duì)外部A/D數(shù)據(jù)采集電路的控制接口邏輯,由于其邏輯功能不是很復(fù)雜,因此可采用自定義的方式。采用這種方法進(jìn)行設(shè)計(jì)有兩種途徑。①?gòu)能浖先?shí)現(xiàn)。這種方案將NIOS處理器作為一個(gè)主控制器,通過(guò)編寫程序來(lái)控制數(shù)據(jù)轉(zhuǎn)換電路。由于NIOS處理器的工作頻率相對(duì)于外部設(shè)備來(lái)說(shuō)要高出許多,故此種方法會(huì)造成CPU資源極大的浪費(fèi);②用FPGA 的邏輯資源來(lái)實(shí)現(xiàn)A/D采集電路的控制邏輯。FPGA有著豐富的邏輯資源和接口資源,在其中實(shí)現(xiàn)并行的數(shù)據(jù)采集很少會(huì)受到硬件資源的限制,在功能上,設(shè)計(jì)的接口控制邏輯相當(dāng)于一個(gè)主控制器,它是針對(duì)具體的外部電路而實(shí)現(xiàn)的,容易滿足要求、又能節(jié)約資源,提高系統(tǒng)性能。因此,采用硬件邏輯去實(shí)現(xiàn)控制將是一種較好的方式。

設(shè)計(jì)方案

通過(guò)對(duì)系統(tǒng)需求進(jìn)行仔細(xì)分析,此模塊的功能設(shè)計(jì)可分為數(shù)據(jù)采集控制邏輯、數(shù)據(jù)接口、數(shù)據(jù)處理邏輯三部分,其整體功能框架圖如圖1。

圖1 模塊功能框圖

說(shuō)明:AVALON總線主要是用于連接片內(nèi)處理器與外設(shè),以構(gòu)成可編程單芯片系統(tǒng)。

功能描述

- 數(shù)據(jù)采集控制邏輯:產(chǎn)生A/D轉(zhuǎn)換需要的控制信號(hào)。

- 數(shù)據(jù)接口:提供一個(gè)外部A/D采集的數(shù)據(jù)流向AVALON總線的數(shù)據(jù)通道,主要是完成速度匹配,接口時(shí)序轉(zhuǎn)換。

- 數(shù)據(jù)處理單元:此部分主要是提供一些附加功能,如檢測(cè)外部信號(hào)或內(nèi)部其它單元的工作狀態(tài),進(jìn)行簡(jiǎn)單信息處理。

設(shè)計(jì)分析

數(shù)據(jù)采集控制邏輯

在此以典型的模數(shù)轉(zhuǎn)換芯片ADC0804為例,進(jìn)行電路設(shè)計(jì),ADC0804的數(shù)據(jù)寬度為8位,數(shù)據(jù)轉(zhuǎn)換時(shí)間最快為100ms,轉(zhuǎn)換時(shí)鐘信號(hào)可以由內(nèi)部施密特電路和外接RC電路構(gòu)成的震蕩器產(chǎn)生,也可以直接由外部輸入,其頻率范圍:100KHz~1460KHz。在本設(shè)計(jì)中ADC0804的時(shí)鐘為最大輸入頻率,控制信號(hào)時(shí)序如圖2。

圖2 ADC0804控制信號(hào)時(shí)序圖

由ADC0804的時(shí)序可知,轉(zhuǎn)換過(guò)程由一個(gè)寫信號(hào)啟動(dòng),轉(zhuǎn)換完成后,輸出INTR信號(hào),此時(shí)可以讀取數(shù)據(jù)。之后即可

進(jìn)入下一個(gè)轉(zhuǎn)換周期。由ADC0804的轉(zhuǎn)換時(shí)間可知,其最大采集頻率為10KHz,只要用戶設(shè)置的采樣頻率不超過(guò)這個(gè)數(shù)值,ADC0804就可以正常的工作。因此設(shè)計(jì)時(shí)要注意兩點(diǎn):①寫信號(hào)的頻率要低于ADC0804的最大轉(zhuǎn)換頻率;②在寫信號(hào)之后至少要有100ms的時(shí)延,才能輸出讀信號(hào)。

在此,提出兩種方法來(lái)實(shí)現(xiàn)ADC0804的控制信號(hào)時(shí)序:①主動(dòng)模式—控制電路啟動(dòng)A/D轉(zhuǎn)換后,在INTR信號(hào)的作用下,輸出讀信號(hào),同時(shí)從ADC0804的數(shù)據(jù)總線上讀入數(shù)據(jù),之后輸出一個(gè)寫信號(hào),開始下一次轉(zhuǎn)換。②被動(dòng)模式—ADC0804的讀寫信號(hào)完全由控制電路按照固定的時(shí)序產(chǎn)生,與其自身輸出無(wú)關(guān)。

數(shù)據(jù)接口

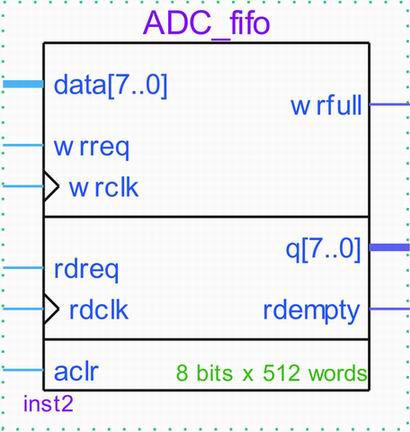

相對(duì)于AVALON總線信號(hào)來(lái)說(shuō),A/D采樣的速率非常低,而且,AVALON總線的接口信號(hào)和ADC0804數(shù)據(jù)輸出的接口信號(hào)時(shí)序不一致。因此,要實(shí)現(xiàn)滿足要求的數(shù)據(jù)通道,要做到兩點(diǎn):①數(shù)據(jù)緩沖,實(shí)現(xiàn)速率匹配;②信號(hào)隔離,實(shí)現(xiàn)接口時(shí)序的轉(zhuǎn)換。解決這兩點(diǎn),可以將兩端口通過(guò)一個(gè)異步的FIFO連接,該FIFO應(yīng)該是可以在不同的時(shí)鐘信號(hào)下進(jìn)行異步的讀寫。這樣的一個(gè)FIFO的實(shí)現(xiàn)可以在Quartus-II里面用ALTERA公司提供的FIFO Core進(jìn)行定制。在本設(shè)計(jì)中,定制的FIFO模塊如圖3。

圖3 FIFO模塊

設(shè)計(jì)實(shí)現(xiàn)

圖4為在Quartus-II中設(shè)計(jì)實(shí)現(xiàn)的ADC0804數(shù)據(jù)采集接口控制模塊的原理圖。

圖4 A/D數(shù)據(jù)采集控制模塊原理圖

其中read、readdata、reset、irq分別與AVALON總線相同命名的信號(hào)線相連,readclk與AVALON總線中clk相連, AD_50與FPGA的系統(tǒng)時(shí)鐘相連,wr_n、rd_n、writedata分別與ADC0804的寫信號(hào)線、讀信號(hào)線、數(shù)據(jù)線相連。ADC0804控制信號(hào)產(chǎn)生單元的實(shí)現(xiàn),采用的是上文提到的被動(dòng)模式,該單元以固定的時(shí)序產(chǎn)生讀寫信號(hào),本設(shè)計(jì)使用的采樣頻率約為3200Hz,此頻率可以根據(jù)用戶的需要而設(shè)定( 不大于10KHz即可)。

當(dāng)系統(tǒng)加電后,wr_n輸出一個(gè)有效的寫信號(hào)啟動(dòng)A/D轉(zhuǎn)換,經(jīng)過(guò)足夠的時(shí)間后(T=327μs~328μs),輸出讀信號(hào),此時(shí)數(shù)據(jù)接口單元的寫允許信號(hào)wr_fifo變?yōu)橛行В瑫r(shí)外部A/D轉(zhuǎn)換器的讀允許信號(hào)也變?yōu)橛行В撕驛DC0804的數(shù)據(jù)端口上輸出有效數(shù)據(jù),在wr_clk的上升沿將A/D轉(zhuǎn)換器的數(shù)據(jù)讀入FIFO。控制邏輯單元的時(shí)序仿真圖如圖5。

由圖5可知,wr_fifo有效時(shí),ADC0804必須在wr_clk的上升沿到來(lái)之前在其數(shù)據(jù)端口輸出有效的數(shù)據(jù)。由于wr_clk的周期為1ms,ADC0804的輸出鎖存由其讀引腳rd控制,rd變?yōu)橛行Ъ纯奢敵鲇行У臄?shù)據(jù),故只要ADC0804的讀信號(hào)rd在外部輸入的作用下變?yōu)橛行У臅r(shí)間不超過(guò)500ns,讀操作就不會(huì)出現(xiàn)問(wèn)題。ADC0804的rd信號(hào)三態(tài)延時(shí)最大為200ns,典型值為125ns,因此控制信號(hào)產(chǎn)生邏輯單元滿足要求。

圖5 控制信號(hào)時(shí)序仿真

當(dāng)NIOS系統(tǒng)需要讀取數(shù)據(jù)時(shí),在read和readclk上出現(xiàn)的是系統(tǒng)AVALON總線上的讀時(shí)序。時(shí)序圖如圖6。

圖6 基本從端口讀傳輸

在AVALON總線中定義了兩種類型的信號(hào),一種是高電平有效,另一種是低電平有效。在本設(shè)計(jì)中選用的是高電平有效的類型。圖6是低電平有效的總線信號(hào),與之對(duì)應(yīng)的高電平有效的總線信號(hào)時(shí)序圖中,read在有效時(shí)為高電平對(duì)應(yīng)于圖6中的readn的低電平部分。而address,be-n和chipselect在此可以不與考慮,添加到AVALON總線時(shí),系統(tǒng)會(huì)自動(dòng)處理其連接問(wèn)題。

當(dāng)系統(tǒng)不讀取A/D轉(zhuǎn)換的數(shù)據(jù)時(shí),采集的數(shù)據(jù)由數(shù)據(jù)處理單元控制處理。數(shù)據(jù)處理單元實(shí)現(xiàn)了對(duì)外部信號(hào)量的異常檢測(cè),即,當(dāng)外部信號(hào)的幅值超出設(shè)定范圍時(shí),該單元產(chǎn)生一個(gè)

中斷信號(hào),通知CPU采取相關(guān)處理措施,否則,在FIFO滿的時(shí)候,將其內(nèi)容清空。

結(jié)語(yǔ)

經(jīng)測(cè)試,本設(shè)計(jì)可以不間斷無(wú)數(shù)據(jù)丟失的進(jìn)行數(shù)據(jù)采集,CPU可以主動(dòng)的讀取數(shù)據(jù),也可以在數(shù)據(jù)處理單元檢測(cè)到外部異常信號(hào)時(shí)被動(dòng)的獲取數(shù)據(jù),并且CPU讀取數(shù)據(jù)的操作極其簡(jiǎn)單,運(yùn)行時(shí)只占用很少的CPU資源,在此,謹(jǐn)希望本文能在如何設(shè)計(jì)NIOS系統(tǒng)外設(shè)方面給讀者以參考借鑒。