引 言

H.264標(biāo)準(zhǔn)作為新一代視頻編碼標(biāo)準(zhǔn),是面向多比特率的視頻編碼標(biāo)準(zhǔn),也稱JVT/AVC標(biāo)準(zhǔn),既可用于高碼率的HDTV和數(shù)字存儲(chǔ)系統(tǒng),也可用于低碼率的實(shí)時(shí)通信系統(tǒng)。在相同的圖像質(zhì)量情況下,H.264比H.263和MPEG一4可以節(jié)省20%~50%的碼率。就其基本檔次而言,編碼器的復(fù)雜度是H.263的10倍左右。H.264良好的網(wǎng)絡(luò)親和性和優(yōu)異的壓縮性能使其成為視頻應(yīng)用的首選,但其巨大的運(yùn)算量成為許多應(yīng)用的瓶頸。筆者基于NiosII設(shè)計(jì)了一種低碼率實(shí)時(shí)應(yīng)用的編碼系統(tǒng)。該系統(tǒng)充分利用FPGA的并行設(shè)計(jì)結(jié)構(gòu),對視頻數(shù)據(jù)采用高壓縮比的H.264標(biāo)準(zhǔn)編碼,能很好地滿足低碼率實(shí)時(shí)編碼的要求。

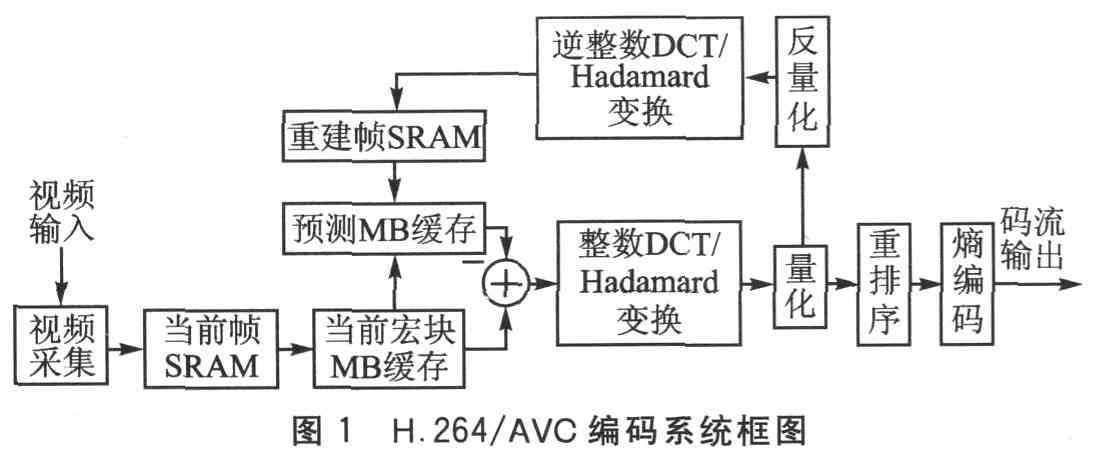

1 H.264編碼系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

根據(jù)H.264/AVC編碼器原理及結(jié)構(gòu),同時(shí)考慮到現(xiàn)有硬件資源的限制以及該設(shè)計(jì)的應(yīng)用需求,設(shè)計(jì)了圖1所示的H.264/AVC編碼系統(tǒng)結(jié)構(gòu)。

攝像頭攝入的視頻圖像首先經(jīng)過視頻采集模塊處理,并將當(dāng)前幀的圖像數(shù)據(jù)存入SRAM。然后,以宏塊MB(macroblock)為單元,從SRAM中讀取原始圖像,并根據(jù)MB所在圖像幀內(nèi)的位置,讀取重建幀中的參考像素進(jìn)行幀內(nèi)預(yù)測,并將預(yù)測宏塊與當(dāng)前宏塊像素做差即可得到預(yù)測殘差。接下來,對殘差圖像進(jìn)行整數(shù)DCT變換或Had—amard變換,并對變換輸出進(jìn)行量化。量化輸出的殘差圖像一方面通過反變換和反量化處理生成重建圖像供幀內(nèi)預(yù)測作為參考,另一方面經(jīng)過重排序、熵編碼處理得到最終的圖像壓縮碼流輸出。

根據(jù)H.264/AVC標(biāo)準(zhǔn),將所設(shè)計(jì)的整個(gè)編碼系統(tǒng)從結(jié)構(gòu)上劃分為圖像采集、幀內(nèi)預(yù)測、變換量化、熵編碼等幾個(gè)主要部分。各個(gè)模塊之間通過流水線的方式進(jìn)行處理,可以有效地提高硬件的執(zhí)行效率。

2 基于Cyclone II FPGA的H.264編碼器的實(shí)現(xiàn)

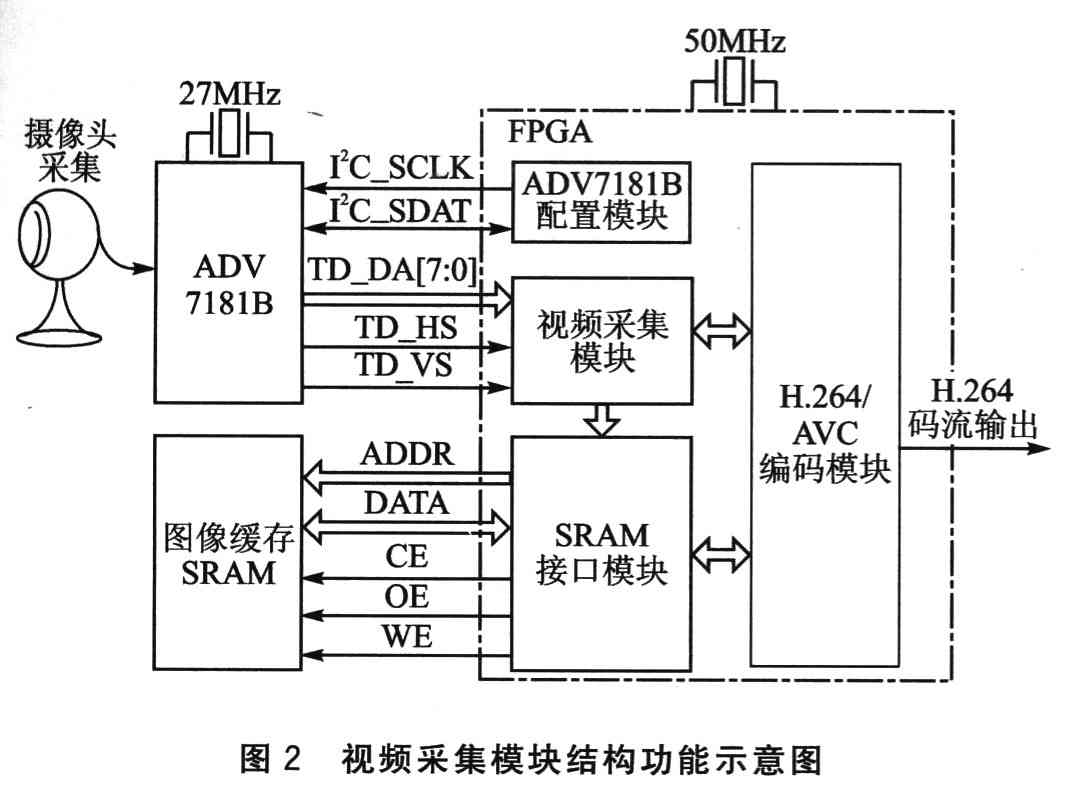

系統(tǒng)采用SOPC的設(shè)計(jì)方式,主要由視頻采集模塊、NiosII處理器系統(tǒng)組成。采用Altera公司的DE2開發(fā)板為開發(fā)平臺(tái),將視頻采集、NiosII處理器集成到一個(gè)SOPC系統(tǒng)中。其中NiosII處理器系統(tǒng)要承擔(dān)圖像采集控制、圖像的H.264壓縮編碼工作。為了保證實(shí)時(shí)性,在充分分析H.264軟件算法運(yùn)行時(shí)間后,采用自定義模塊對H.264編碼器關(guān)鍵算法進(jìn)行硬件加速。

2.1 視頻采集模塊

視頻采集是視頻圖像處理、傳輸?shù)那疤幔杉降臄?shù)字視頻圖像好壞將直接影響到視頻處理的結(jié)果。圖2給出了圖像處理系統(tǒng)的視頻采集結(jié)構(gòu)。

ADI公司的多制式視頻解碼芯片ADV7181B對采集的視頻圖像進(jìn)行模數(shù)轉(zhuǎn)換。ADV7181B可以自動(dòng)檢測諸如NTSC、PAL和SEC0M制式的基帶視頻信號,并將其轉(zhuǎn)換為基于4:2:2取樣的16/8位兼容的CCIR601/CCIR656格式的數(shù)字視頻信號;具有6路模擬視頻輸入端口,且采用單一的27 MHz晶振時(shí)鐘輸入;用戶可以通過兩線的I2C接口對ADV7181B的工作模式進(jìn)行配置。

系統(tǒng)上電時(shí),首先使用I2C模塊對ADV7181B的內(nèi)部寄存器進(jìn)行配置。由于攝像頭輸出的是PAL制式的模擬視頻信號,因此需要相應(yīng)地將ADV7181B配置為PAL制式的模擬視頻信號輸入,并將其轉(zhuǎn)換為CCIR656格式的數(shù)字視頻信號。ADV7181B將轉(zhuǎn)換得到的實(shí)時(shí)數(shù)字視頻圖像的亮度信號、色度信號(TD_DAT)以及行、場同步信號(TD_HS/VS)同時(shí)輸入到FPGA芯片中,通過圖像采集模塊提取需要的數(shù)字圖像信息,并將其轉(zhuǎn)存至AlteraDE2開發(fā)板提供的具有512 KB存儲(chǔ)容量的SRAM中,用于緩存待處理圖像幀。

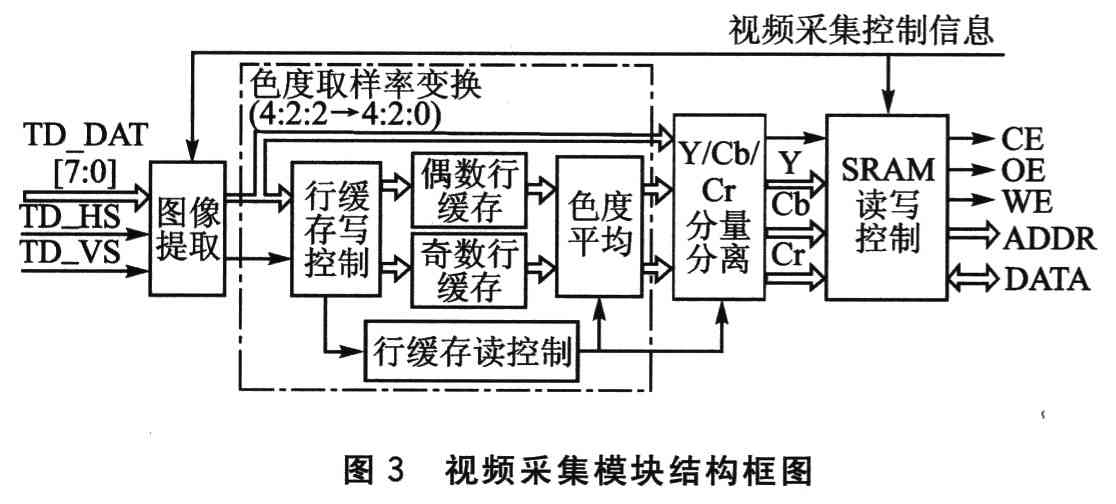

下面介紹圖像采集模塊的設(shè)計(jì)與實(shí)現(xiàn)方法。

根據(jù)上面對視頻采集部分硬件結(jié)構(gòu)的分析,設(shè)計(jì)了圖3所示的視頻采集模塊結(jié)構(gòu)框圖。可以看出,圖像采集模塊主要包含圖像提取、色度取樣率變換、Y/Cb/Cr圖像分量分離以及圖像緩存SRAM讀寫控制等單元。

其中圖像提取子模塊在H.264/AVC編碼模塊的視頻采集控制信息的控制下,從ADV7181B轉(zhuǎn)換輸出的PAL制數(shù)字視頻圖像中提取需要的圖像數(shù)據(jù)。攝像頭采集的實(shí)際圖像大小為768×576像素的隔行掃描視頻輸入信號,其中基數(shù)場和偶數(shù)場在時(shí)間上先后輸入。由于系統(tǒng)處理的圖像大小為320×240像素,因此需要對輸入的數(shù)字視頻進(jìn)行截取,以滿足系統(tǒng)的處理要求。

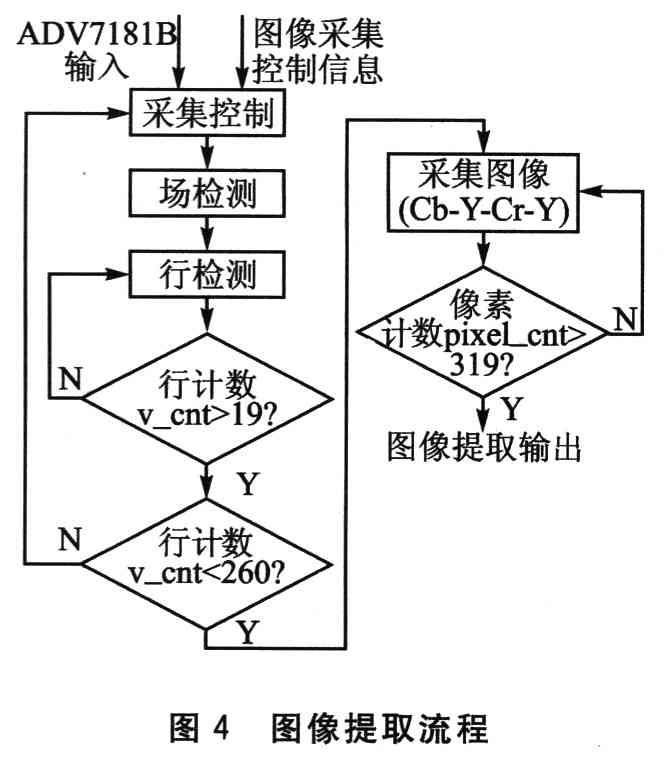

考慮到在一幀圖像中的頂場與底場數(shù)據(jù)差異不大,因此在對圖像進(jìn)行截取時(shí),僅對底場中間240行的連續(xù)320個(gè)相鄰像素點(diǎn)進(jìn)行提取,以輸出320×240像素的視頻圖像數(shù)據(jù)。其具體提取流程如圖4所示。

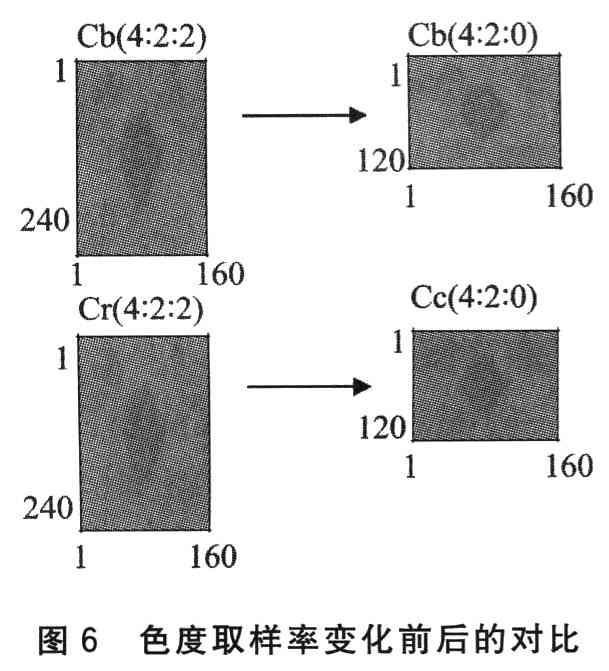

H.264/AVC支持對色度取樣為4:2:O格式的逐行或隔行掃描數(shù)字圖像進(jìn)行處理,因此需要對提取的數(shù)字圖像進(jìn)行色度取樣率變換。通過對相鄰奇數(shù)行和偶數(shù)行的色度圖像分量進(jìn)行簡單的平均,可實(shí)現(xiàn)由4:4:4向4:2:O的色度取樣率變換,如圖5所示。

經(jīng)過取樣率變換后的圖像數(shù)據(jù)需要根據(jù)Y/Cb/Cr圖像類型在SRAM中分片區(qū)緩存,以方便后續(xù)的H_264的編碼處理。圖6給出了實(shí)際圖像的色度分量在取樣率變換前后的效果。