摘 要:針對(duì)印染設(shè)備多單元同步控制中動(dòng)態(tài)性和穩(wěn)定性的問題,,提出一種基于DSP和FPGA的嵌入式同步控制器設(shè)計(jì)方案。DSP作為運(yùn)算控制的核心,,負(fù)責(zé)控制算法的實(shí)現(xiàn),;FPGA作為數(shù)據(jù)采集模塊的核心,負(fù)責(zé)數(shù)據(jù)采集的實(shí)現(xiàn),。該系統(tǒng)具有結(jié)構(gòu)靈活,,通用性強(qiáng)的特點(diǎn),且大大減少了系統(tǒng)的外圍接口器件,,降低了成本。采用Bang-Bang控制和數(shù)字PID控制相結(jié)合的雙??刂扑惴?,滿足了系統(tǒng)響應(yīng)快速性和穩(wěn)定性的要求,提高了可靠性,,具有很高的實(shí)用價(jià)值,。

關(guān)鍵詞:嵌入式;同步控制,;DSP,;FPGA

在印染機(jī)械設(shè)備生產(chǎn)加工過程中,各個(gè)傳動(dòng)單元分別由獨(dú)立的電機(jī)驅(qū)動(dòng),。為了保證整機(jī)各單元同步協(xié)調(diào)工作,,提高產(chǎn)品質(zhì)量,需要設(shè)計(jì)相應(yīng)的同步控制器,。多單元同步傳動(dòng)是印染機(jī)械設(shè)備同步控制的關(guān)鍵,,但由于交流電機(jī)嚴(yán)重的非線性,系統(tǒng)的動(dòng)態(tài)特性和相應(yīng)的參數(shù)受外界擾動(dòng)因素的影響,,增加了實(shí)際同步控制的難度,,降低了實(shí)際的控制精度。傳統(tǒng)的控制方案設(shè)計(jì)如帶轉(zhuǎn)換式松緊架的同步系統(tǒng)可靠性差,,控制精度不高,,難以獲得滿意的控制效果,又由于系統(tǒng)要求快速同步動(dòng)態(tài)跟隨,,不允許有大的超調(diào),。因此提出一種基于DSP和FPGA的嵌入式控制器,以提高系統(tǒng)的動(dòng)態(tài)跟隨速度和同步性能,。該控制裝置可直接嵌入電控裝置內(nèi),,實(shí)時(shí),、高性能地完成控制功能。

1 系統(tǒng)的總體控制策略

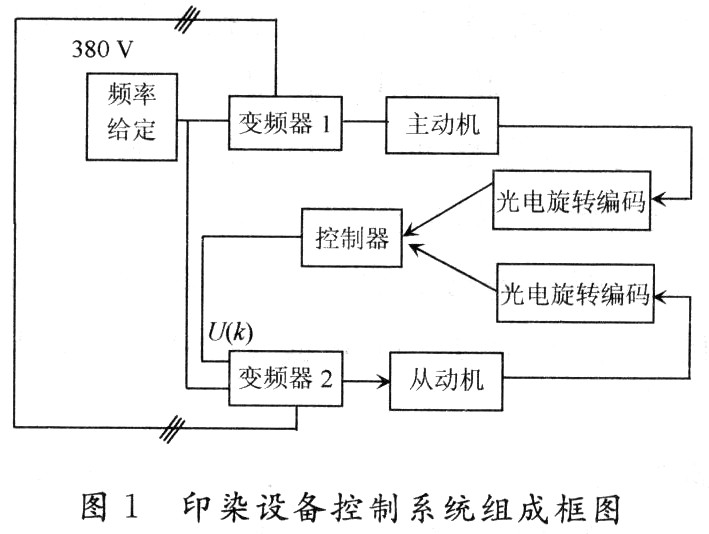

大多數(shù)印染設(shè)備根據(jù)工藝要求都采用聯(lián)合機(jī)方式組成多單元同步拖動(dòng)系統(tǒng),,主電機(jī)的速度作為各從動(dòng)電機(jī)的給定速度,,各從動(dòng)單元分別由各自的異步電機(jī)拖動(dòng),系統(tǒng)要求各單元電機(jī)保持同步運(yùn)轉(zhuǎn),,即各從動(dòng)電機(jī)線速度始終保持與主電機(jī)速度一致,,或保持一定的比例關(guān)系。為了驗(yàn)證控制方案的可行性,,以雙單元(主動(dòng)機(jī),、從動(dòng)機(jī))交流同步拖動(dòng)系統(tǒng)為例進(jìn)行了研究。印染設(shè)備控制系統(tǒng)組成框圖如圖1所示,。

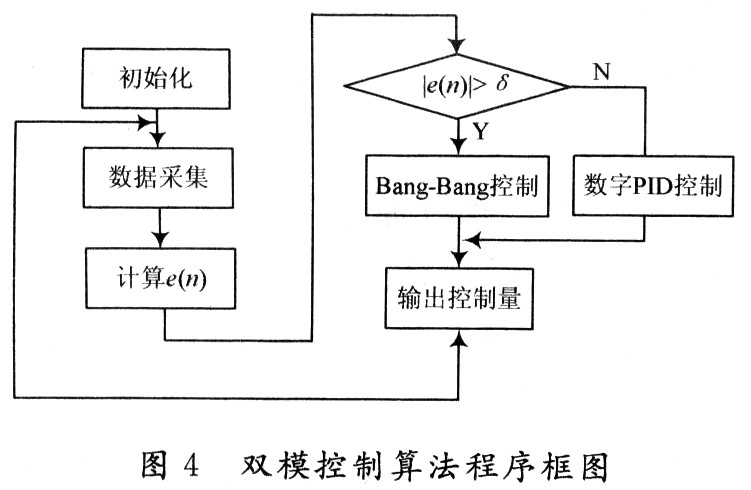

主動(dòng)機(jī)和從動(dòng)機(jī)分別由變頻器1和變頻器2供電,。同軸安裝光電旋轉(zhuǎn)編碼器,光電旋轉(zhuǎn)編碼器將主從動(dòng)機(jī)的轉(zhuǎn)速信號(hào)轉(zhuǎn)換成脈沖信號(hào),,并送給控制器進(jìn)行處理,,經(jīng)過控制算法,輸出數(shù)字控制量到從動(dòng)機(jī)的變頻器,,改變其運(yùn)行頻率,,調(diào)整從動(dòng)機(jī)的轉(zhuǎn)速,使之與主動(dòng)機(jī)保持同步,。由以上分析可知,,主從動(dòng)機(jī)保持同步是控制器設(shè)計(jì)的關(guān)鍵??刂破骱诵挠?6位的微處理器(DSP)和現(xiàn)場(chǎng)可編程門陣列(FPGA)組成,。基于DSP+FPGA的嵌入式同步控制器,,具有結(jié)構(gòu)靈活,,通用性強(qiáng)的特點(diǎn),適用于模塊化設(shè)計(jì),,可大大減少系統(tǒng)的外圍器件,,降低成本。DSP作為運(yùn)算控制的核心,,主要完成電機(jī)啟停,,控制算法的實(shí)現(xiàn)和各類接口處理等;FAPG作為數(shù)據(jù)采集模塊的核心,,負(fù)責(zé)數(shù)據(jù)采集和鍵盤接口電路的實(shí)現(xiàn),。為了使印染設(shè)備各單元同步協(xié)調(diào)工作,提高系統(tǒng)的響應(yīng)速度,,對(duì)各單元電機(jī)的線速度采用雙??刂频姆椒?,即將Bang-Bang控制與PID控制結(jié)合起來使用。在|e|>δ(δ為某一常數(shù))時(shí),,實(shí)行Bang-Bang控制,,以最快的速度使調(diào)節(jié)參數(shù)逼近給定值;在|e|<δ時(shí),,實(shí)行數(shù)字PID調(diào)節(jié),,以消除系統(tǒng)的調(diào)節(jié)偏差。這樣即可加快控制過程,,又可保證系統(tǒng)超調(diào)較小,,從而取得良好的動(dòng)態(tài)品質(zhì)。

2 系統(tǒng)主要硬件組成

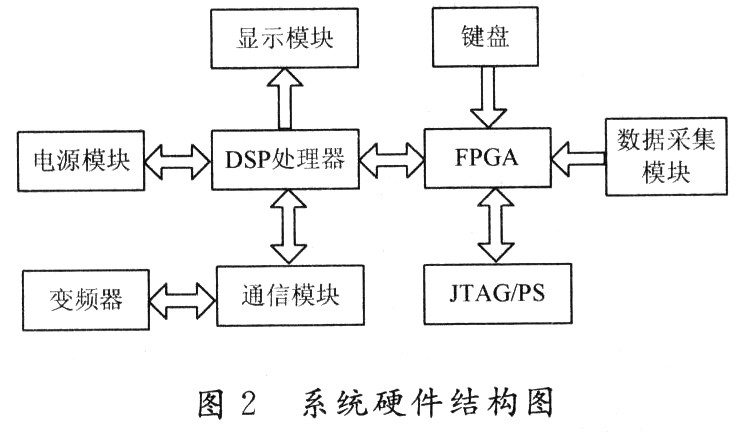

嵌入式控制器的硬件結(jié)構(gòu)如圖2所示,。DSP為系統(tǒng)的核心單元,,它對(duì)采集的各種參數(shù)進(jìn)行運(yùn)算、分析和顯示,,并可通過通信模塊與本地帶485接口的儀表通信,。選用TI公司的TMS320LF2407A型DSP芯片,它采用高性能靜態(tài)CMOS技術(shù),,供電電壓降為3.3 V,功耗小,,具有30 MIPS的執(zhí)行速度,,使得指令周期縮短到33 ns,提高了控制器的實(shí)時(shí)控制能力,;片內(nèi)有高達(dá)32 KB的FLASH程序存儲(chǔ)器,。16位TMS320LF2407A型DSP芯片具有采樣速度快,浮點(diǎn)處理速度高,,穩(wěn)定性好等特點(diǎn),。DSP的特殊結(jié)構(gòu)和優(yōu)良性能滿足了系統(tǒng)的需要。

FPGA采用Altera公司的FLEX系列芯片EPFl0Kl0LC84,,具有高密度,,低成本,低功率等特點(diǎn),,可支持多電壓I/O接口,,是在PAL,GAL,,EPLD等可編程邏輯器件的基礎(chǔ)上發(fā)展起來的,,非常適于時(shí)序、組合等邏輯電路的應(yīng)用場(chǎng)合,。FPGA作為一個(gè)外部協(xié)處理器使用,,通過總線與DSP處理器連接,,主要實(shí)現(xiàn)的功能是脈沖計(jì)數(shù)、鍵盤掃描等,。FPGA最大的特點(diǎn)是它的內(nèi)部邏輯在線的可重構(gòu)性,。當(dāng)應(yīng)用需求發(fā)生變化時(shí),對(duì)FPGA重新進(jìn)行編程,,即可改變其邏輯行為,,大大提高了系統(tǒng)的開放性和可重構(gòu)性。FPGA的高速性和靈活性也保證了系統(tǒng)的實(shí)時(shí)性,,并且簡(jiǎn)化了系統(tǒng)的外圍電路,,降低了成本。

顯示模塊采用G35LCD屏,,通過總線與DSP的連接,,通過配置相關(guān)寄存器,編寫調(diào)用相關(guān)應(yīng)用程序接口函數(shù)即可顯示待測(cè)參數(shù),、運(yùn)行狀態(tài)及其他輔助信息,。通信模塊由RS 485接口電路組成,可以用它將控制器和變頻器連接在一起,。通過通信實(shí)現(xiàn)由控制器設(shè)定和修改變頻器的參數(shù),,以監(jiān)視其工作狀態(tài)。為了便于實(shí)現(xiàn)現(xiàn)場(chǎng)調(diào)試,、數(shù)據(jù)輸入和命令傳送等控制功能,,該系統(tǒng)設(shè)計(jì)了一個(gè)4×4的矩陣鍵盤。采用FPGA來完成鍵盤接口電路,,可節(jié)省I/O資源,,減輕處理器負(fù)擔(dān),提高系統(tǒng)的整體性能,。數(shù)據(jù)采集模塊用2個(gè)旋轉(zhuǎn)編碼器把電機(jī)轉(zhuǎn)速轉(zhuǎn)換為數(shù)字脈沖,,由FPGA記錄脈沖值,DSP通過中斷讀取數(shù)值,。經(jīng)運(yùn)算處理后,,經(jīng)通信模塊輸出控制量U(k)到各從動(dòng)機(jī)的變頻器,通過變頻器調(diào)節(jié)從動(dòng)機(jī)的轉(zhuǎn)速,,使其不斷跟隨主動(dòng)機(jī)轉(zhuǎn)速的變化而實(shí)現(xiàn)同步,。以上設(shè)計(jì)提高了系統(tǒng)的靈活性和通用性,降低了開發(fā)成本,,可作為一個(gè)獨(dú)立模塊與嵌入式系統(tǒng)連接,。

3 系統(tǒng)主要軟件設(shè)計(jì)

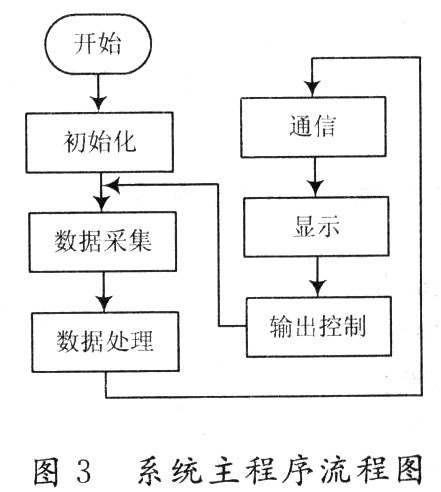

這里的程序采用模塊化設(shè)計(jì),軟件主要包括主程序,、數(shù)據(jù)采集程序,、通信子程序,、顯示子程序、雙??刂扑惴ǔ绦虻?。初始化程序主要完成各個(gè)寄存器的清零、定時(shí)器的初始化等,。數(shù)據(jù)采集程序主要完成各電機(jī)轉(zhuǎn)速的測(cè)量,,顯示子程序主要完成各輸入量和各設(shè)定值的顯示。雙??刂瞥绦蛑饕脕硖岣呦到y(tǒng)的響應(yīng)速度和穩(wěn)定性能,。主程序和雙模控制程序如圖3,、圖4所示,。

4 試驗(yàn)驗(yàn)證

為了驗(yàn)證控制方案的可行性,在實(shí)驗(yàn)室以雙單元異步電機(jī)(主動(dòng)機(jī),、從動(dòng)機(jī))交流同步拖動(dòng)系統(tǒng)為對(duì)象進(jìn)行了模擬實(shí)際系統(tǒng)的實(shí)驗(yàn),。主電機(jī)型號(hào)Y90S-4;額定功率1.1 kW,;額定電壓380 V,;額定電流2.8 A;額定轉(zhuǎn)速1 400 rad/min,;接法Y,;頻率50 Hz;從動(dòng)機(jī)型號(hào)Y80-4,;額定功率0.75 kw;額定電壓380 V,;額定電流7 A,;額定轉(zhuǎn)速1 450 rad/min;接法Y,;頻率50 Hz,。選用直流發(fā)電機(jī)2臺(tái),分別由2臺(tái)三相異步電動(dòng)機(jī)拖動(dòng),,加變阻箱后作為電動(dòng)機(jī)的負(fù)載,。兩臺(tái)變頻器對(duì)兩臺(tái)三項(xiàng)異步電動(dòng)機(jī)進(jìn)行驅(qū)動(dòng)。光電編碼器將從動(dòng)機(jī)的轉(zhuǎn)速信號(hào)轉(zhuǎn)換成脈沖信號(hào),,并送給控制器進(jìn)行處理,。

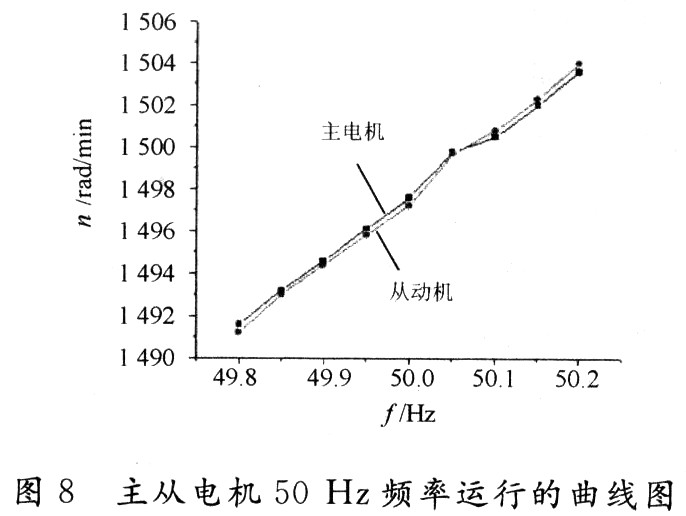

試驗(yàn)測(cè)得兩電機(jī)的轉(zhuǎn)速后繪制的曲線如圖5~圖8所示。

結(jié)果顯示,,系統(tǒng)運(yùn)行過程中,,主從電機(jī)低頻段的跟隨精度稍差,,而高頻段的跟隨精度較高。主從電機(jī)在較寬的調(diào)速范圍內(nèi)都能達(dá)到很好的同步性能,,動(dòng)態(tài)過程的同步控制效果也較好,,達(dá)到了預(yù)期的效果。

5 結(jié) 語(yǔ)

研究表明,,系統(tǒng)采用基于DSP和FPGA的嵌入式同步控制器后,,對(duì)于多單元同步系統(tǒng)的動(dòng)態(tài)同步性能有了明顯的改善,運(yùn)行穩(wěn)定,,無波動(dòng),,達(dá)到了各分單元同步傳動(dòng)的控制要求,兼顧了系統(tǒng)響應(yīng)的快速性和穩(wěn)定性的要求,,且控制精度高,,具有很高的實(shí)用價(jià)值。