1 引言

偵察與監(jiān)視在軍事斗爭(zhēng)中的地位舉足輕重。在各種偵察/監(jiān)視技術(shù)中,航空偵察占有重要的地位,可見(jiàn)光偵察是一種重要的偵察形式,無(wú)人偵察機(jī)顯示出了廣闊的發(fā)展前景,現(xiàn)代科學(xué)技術(shù)的發(fā)展為現(xiàn)代航空偵察與監(jiān)視技術(shù)帶來(lái)了新的發(fā)展契機(jī)。

航空偵察一個(gè)主要的途徑就是利用高性能高速攝像機(jī)進(jìn)行航空拍照,采集各種圖像信息。然而,數(shù)字化的偵察圖像分辨率高、信息量大,使后續(xù)的處理、傳輸、存儲(chǔ)等過(guò)程的實(shí)現(xiàn)變得極為困難,從而給機(jī)載圖像/視頻系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)帶來(lái)了巨大的挑戰(zhàn)。為了解決這些問(wèn)題,本文基于某型高速相機(jī),利用低成本FPGA,構(gòu)建了一個(gè)高性能的圖像采集存儲(chǔ)系統(tǒng),完成對(duì)高分辨率、高幀率偵察圖像的采集和存儲(chǔ)。

2 某型高速相機(jī)簡(jiǎn)介[1]

系統(tǒng)選擇的高速相機(jī)是一款高分辨率、高速度線掃數(shù)字相機(jī),其圖像傳感器采用先進(jìn)的CCD(Charge-Coupled Device)圖像傳感器,采用了世界尖端水平的高靈敏度掃描成像技術(shù)——高速率的TDI(Time Delay and Integration)技術(shù)、多重曝光技術(shù)并加強(qiáng)藍(lán)色響應(yīng),從而使該型相機(jī)可提供比單輸出線掃相機(jī)更好的靈敏度特性,總的數(shù)據(jù)傳輸率可高達(dá)200MB/s。

相機(jī)接口主要包括后面板上的六個(gè)接口:其中四個(gè)為數(shù)據(jù)輸出接口,每個(gè)接口包括16位數(shù)據(jù)信號(hào),1位數(shù)據(jù)同步信號(hào),1位同步時(shí)鐘信號(hào),信號(hào)的電平輸出格式為L(zhǎng)VDS電平格式;另外兩個(gè)接口分別為控制信號(hào)接口和電源接口。在控制信號(hào)的作用下,相機(jī)同步輸出包含同步時(shí)鐘信號(hào)(STROBE)和水平同步信號(hào)(LVAL)在內(nèi)的 8×8bit標(biāo)準(zhǔn)的灰度圖像數(shù)據(jù),圖像分辨率可選擇為4096×30`72(本系統(tǒng)采用分辨率)和2048×3072。

相機(jī)控制接口信號(hào)中,行觸發(fā)信號(hào)(EXSYNC)至關(guān)重要。它負(fù)責(zé)圖像數(shù)據(jù)的觸發(fā)輸出,行觸發(fā)信號(hào)的上升沿觸發(fā)數(shù)據(jù)并指示數(shù)據(jù)有效。相機(jī)觸發(fā)要求此信號(hào)存在下降沿,最小觸發(fā)頻率為300HZ。

3 系統(tǒng)硬件設(shè)計(jì)及工作原理

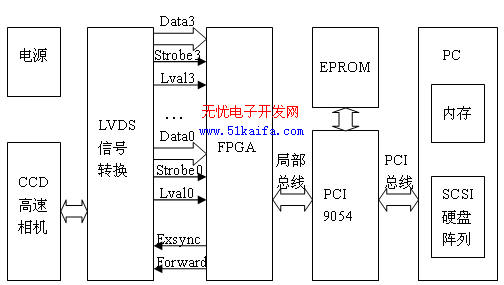

本設(shè)計(jì)硬件系統(tǒng)主要包括電平轉(zhuǎn)換,數(shù)據(jù)接收預(yù)處理和數(shù)據(jù)采集存儲(chǔ)三個(gè)部分。圖1為系統(tǒng)硬件原理框圖。在總線結(jié)構(gòu)上,系統(tǒng)采用了滿足高速數(shù)據(jù)傳輸?shù)腜CI總線結(jié)構(gòu),PCI9054是PLX公司推出的一種32位33MHz的PCI總線主控I/O加速器,它采用多種先進(jìn)技術(shù),使復(fù)雜的PCI接口應(yīng)用設(shè)計(jì)變得相對(duì)簡(jiǎn)單。

從資源和成本方面考慮,F(xiàn)PGA選用Altera公司的低成本Cyclone系列芯片-EP1C6Q240C8。存儲(chǔ)介質(zhì)則選用SCSI磁盤(pán)陣列,它能滿足高速、大數(shù)據(jù)量的存儲(chǔ)。

圖1 系統(tǒng)原理框圖

系統(tǒng)工作原理:

系統(tǒng)上電,首先完成一系列初始化工作:PC通過(guò)底層驅(qū)動(dòng)配置PCI9054的寄存器,使之處于正常工作模式(C模式)[2]; FPGA上電,配置用戶電路(此時(shí),F(xiàn)PGA內(nèi)部邏輯和PCI9054都處于等待狀態(tài))。

PC應(yīng)用程序啟動(dòng)后,向PCI9054發(fā)送數(shù)據(jù)傳輸指令,PCI9054收到數(shù)據(jù)傳輸指令,通過(guò)LOCAL BUS通知FPGA開(kāi)始工作:FPGA產(chǎn)生行觸發(fā)信號(hào)(EXSYNC),觸發(fā)相機(jī)進(jìn)行拍照、傳輸數(shù)據(jù)。然后,PCI9054進(jìn)入工作狀態(tài),開(kāi)始采集數(shù)據(jù),并將數(shù)據(jù)存儲(chǔ)到磁盤(pán)陣列。FPGA內(nèi)部邏輯和PC應(yīng)用程序通過(guò)行計(jì)數(shù)判斷一幀圖像傳輸完畢,相繼進(jìn)入等待狀態(tài)。但是,PC應(yīng)用程序在接收完一幀圖像,進(jìn)入等待狀態(tài)后,延續(xù)一定時(shí)間,會(huì)自動(dòng)觸發(fā)下一個(gè)數(shù)據(jù)傳輸指令通知FPGA開(kāi)始下一幀圖像傳輸。

3.1 電平格式轉(zhuǎn)換

PCI9054芯片電平格式為3.3V LVTTL格式,相機(jī)輸出信號(hào)的電平格式為L(zhǎng)VDS格式,基于系統(tǒng)總體需要,有必要在進(jìn)行圖像預(yù)處理前將LVDS相機(jī)輸出信號(hào)轉(zhuǎn)換成LVTTL格式電平。

3.2 數(shù)據(jù)接收預(yù)處理

FPGA完成圖像預(yù)處理功能。FPGA是以并行運(yùn)算為主導(dǎo)的芯片,處理速度更快。數(shù)據(jù)預(yù)處理過(guò)程包括:數(shù)據(jù)緩沖、位并轉(zhuǎn)換。

數(shù)據(jù)緩沖[3]:相機(jī)利用4個(gè)通道輸出圖像數(shù)據(jù),每個(gè)端口的數(shù)據(jù)傳輸以本端口時(shí)鐘為參考,傳輸過(guò)程中由于各種差異如傳輸電纜的長(zhǎng)度不同,使得各個(gè)端口的時(shí)鐘信號(hào)產(chǎn)生相對(duì)的相位漂移,從而使四個(gè)端口數(shù)據(jù)輸出不完全同步,這不利于圖像數(shù)據(jù)的同步采集。為消除數(shù)據(jù)異步,F(xiàn)PGA內(nèi)部設(shè)計(jì)了由4個(gè)FIFO組成的數(shù)據(jù)緩沖器組。每個(gè)端口的有效數(shù)據(jù)寬度為16bit,傳送一行4096個(gè)數(shù)據(jù)需用512個(gè)時(shí)鐘周期,因此FIFO深度設(shè)為512個(gè)字。相機(jī)送來(lái)的4個(gè)LVAL信號(hào)為各對(duì)應(yīng)通道寫(xiě)使能信號(hào), 4個(gè)STROBE信號(hào)作為對(duì)應(yīng)通道寫(xiě)時(shí)鐘。FIFO輸出端采用系統(tǒng)時(shí)鐘(15MHz)作為統(tǒng)一的數(shù)據(jù)同步時(shí)鐘,并設(shè)計(jì)一個(gè)讀請(qǐng)求信號(hào),當(dāng)FIFO半滿時(shí)讀取數(shù)據(jù),經(jīng)過(guò)緩存的數(shù)據(jù)以與系統(tǒng)時(shí)鐘同步的64bit寬度格式輸出。

位并轉(zhuǎn)換:PCI9054芯片LOCAL端的有效數(shù)據(jù)位數(shù)有兩種選擇:8bit和32bit(可更改9054寄存器設(shè)置,為了保證數(shù)據(jù)采集速度,本系統(tǒng)設(shè)置為32bit)。但是相機(jī)的輸出數(shù)據(jù)通過(guò)緩沖之后仍然為64bit,為了滿足PCI9054數(shù)據(jù)采集位數(shù)要求,必須將64bit數(shù)據(jù)進(jìn)行位并轉(zhuǎn)換,變成32bit傳輸。本系

統(tǒng)設(shè)計(jì)在FPGA內(nèi)部將數(shù)據(jù)的高32bit和低32bit分別送入二選一BUSMUX的輸入端,系統(tǒng)時(shí)鐘的電平選

擇數(shù)據(jù)輸出。64bit數(shù)據(jù)轉(zhuǎn)化成32bit數(shù)據(jù)傳輸,但數(shù)據(jù)率變成原來(lái)的兩倍(30M/s)。

3.3 數(shù)據(jù)采集存儲(chǔ)

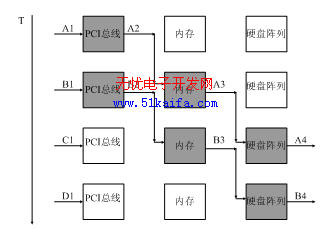

對(duì)于整個(gè)系統(tǒng)來(lái)說(shuō),存儲(chǔ)系統(tǒng)的持續(xù)存儲(chǔ)速度是個(gè)至關(guān)重要的參數(shù)。數(shù)據(jù)的采集存儲(chǔ)采用微機(jī)為主體,在其PCI總線上掛載一塊SCSI的接口卡和9054接口卡,9054接口卡用于數(shù)據(jù)采集,SCSI接口卡上掛載兩個(gè)SCSI硬盤(pán),組成RAID-0的硬盤(pán)陣列,這樣可以大大提高硬盤(pán)的持續(xù)存儲(chǔ)速度。利用PCI9054進(jìn)行數(shù)據(jù)采集時(shí),數(shù)據(jù)的傳輸路徑為:PCI總線-內(nèi)存-硬盤(pán)陣列。現(xiàn)有兩種傳輸方案可供選擇:第一種為單線采集存儲(chǔ),顯然,這種方案會(huì)降低數(shù)據(jù)的的采集速度。本系統(tǒng)選用第二種方案:流水線存儲(chǔ),如圖2所示。理論上,流水線方式的數(shù)據(jù)采集速度應(yīng)該是單線采集的兩倍。

圖2 流水線存儲(chǔ)時(shí)序示意圖

4 部分軟硬件程序設(shè)計(jì)

3.4 PCI9054 Local Bus 硬件驅(qū)動(dòng)

PCI9054局部總線是外設(shè)(FPGA)和9054之間通信的橋梁。9054圖像數(shù)據(jù)的采集需要使9054局部總線信號(hào)滿足一定的時(shí)序要求,保證數(shù)據(jù)傳輸?shù)耐剑葱枰狥PGA端硬件驅(qū)動(dòng)。驅(qū)動(dòng)是用Verilog HDL代碼編寫(xiě)的一個(gè)狀態(tài)機(jī),代碼如下[2][4]:

always @ (posedge CLK)

begin

casex (CurrentState)

1'b0: begin

if (!LLADS_)

begin LLREADY <= 1; CurrentState <= 1; end

else begin LLREADY <= 0; end

end

1'b1: begin

if (LLBLAST_) //突發(fā)循環(huán)重復(fù)

begin LLREADY <= 1; CurrentState <= 1; end

else //最后一個(gè)循環(huán)

begin LLREADY <= 0; CurrentState <= 0; end

end

default:

CurrentState <= 0;

Endcase end

assign LLREADY_ = (LLREADY) ? 1'b0 : 1'b1;

4.2 PCI9054驅(qū)動(dòng)層和應(yīng)用層設(shè)計(jì)

系統(tǒng)所用PCI采集卡非windows標(biāo)準(zhǔn)硬件,驅(qū)動(dòng)程序需要自行開(kāi)發(fā),這里使用WDM編程。為了提高速度采用雙線程操作。由于寫(xiě)磁盤(pán)比較慢,如果等寫(xiě)完磁盤(pán)再讀local bus顯然效率太低,所以啟動(dòng)雙線程雙buffer讀寫(xiě)數(shù)據(jù)[5]。

部分程序代碼:

BOOL GetData()

{ ……

//創(chuàng)建等待驅(qū)動(dòng)中斷線程以及寫(xiě)文件線程

hEvent_Disk=GreateEvent(NULL,TRUE,TRUE,NULL); hEvent_Mem = CreateEvent(NULL,TRUE,FALSE,NULL);

_beginthread(WaitForDataThread,0,NULL); _beginthread(WriteDiskThread,0,NULL);

//啟動(dòng)DMA傳輸

SetDma(); BlockDmaLocalToPci(dmabuffer, BLOCK_ONE_DMA);

}

void WaitForDataThread(void * pParam)

{}

void WriteDiskThread(void * pParam)

{}

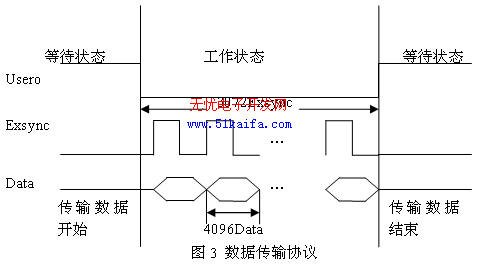

4.3 數(shù)據(jù)傳輸指令生成

PC應(yīng)用程序產(chǎn)生數(shù)據(jù)傳輸指令,觸發(fā)數(shù)據(jù)傳輸。指令的產(chǎn)生是通過(guò)9054在PC端的底層驅(qū)動(dòng),設(shè)置9054 LOCAL端USERO管腳電平,使FPGA進(jìn)入工作狀態(tài),并產(chǎn)生相機(jī)行觸發(fā)信號(hào)(EXSYNC),觸發(fā)相機(jī)拍照傳輸數(shù)據(jù)。USERO信號(hào)為高電平時(shí),F(xiàn)PGA和9054都處于等待狀態(tài);USERO下降沿觸發(fā)數(shù)據(jù)傳輸,使FPGA和9054進(jìn)入工作狀態(tài);數(shù)據(jù)傳輸完畢,USERO拉高。時(shí)序如圖3。

5 系統(tǒng)測(cè)試及工程考慮

本系統(tǒng)測(cè)試微機(jī)環(huán)境為:CPU,Pentium(R) 4. 2.40GHz;內(nèi)存,333MHz,512MB/s;北橋芯片,845PE;操作系統(tǒng),Windows Server 2003;SCSI硬盤(pán)空間,120G。

系統(tǒng)測(cè)試結(jié)果:圖像單線穩(wěn)定存儲(chǔ)速率為37.2 MB/s ,流水線穩(wěn)定存儲(chǔ)速率為71.2MB/s;持續(xù)記錄時(shí)間為25分鐘。

工程考慮:系統(tǒng)速度主要限制于兩個(gè)瓶頸,一是硬盤(pán)本身,二是PCI總線。本系統(tǒng)雖然采用了高速硬盤(pán),但還有一個(gè)操作效率的問(wèn)題。數(shù)據(jù)從FPGA到PCI9054的傳輸介質(zhì)采用一般硬盤(pán)線,此類(lèi)硬盤(pán)線的上限頻率為33M,限制數(shù)據(jù)采集速度;同時(shí)由于系統(tǒng)需要通過(guò)PCI總線轉(zhuǎn)移數(shù)據(jù),而計(jì)算機(jī)的PCI總線多為32位、33MHz的總線,這個(gè)總線的理論數(shù)據(jù)為132MB/s,當(dāng)總線上僅僅有一個(gè)設(shè)備時(shí),實(shí)測(cè)實(shí)際總線持續(xù)傳輸速率在100MB/s以下,當(dāng)總線上再掛載磁盤(pán)適配器時(shí),總線的數(shù)據(jù)傳輸速率會(huì)更低。系統(tǒng)穩(wěn)定性主要取決于FPGA內(nèi)部邏輯的容錯(cuò)性和微機(jī)的穩(wěn)定性。在高速存儲(chǔ)的環(huán)境下,微機(jī)系統(tǒng)容易死機(jī),因此微機(jī)選擇具有高穩(wěn)定性的Windows Server 2003操作系統(tǒng)作為圖像采集的存儲(chǔ)環(huán)境。