引言

LVDS" title="LVDS">LVDS (低電壓差分信號" title="信號">信號)是一種能滿足超高速數(shù)據(jù)傳輸" title="數(shù)據(jù)傳輸">數(shù)據(jù)傳輸的新技術(shù),它具有低電壓、低輻射、低功耗、低成本和內(nèi)含時鐘等優(yōu)點,尤其適用于有一定傳輸距離要求的低功耗高速數(shù)據(jù)傳輸。由于用LVDS接口傳輸信號必須先進(jìn)行LVDS和TTL的轉(zhuǎn)換,所以在LVDS接口處使用專用LVDS收發(fā)器芯片不僅提高了成本,而且增大了PCB板的面積;而用千兆網(wǎng)卡傳輸則需要使用幀同步" title="同步">同步字,并且在接收" title="接收">接收端需要對接收到的數(shù)據(jù)進(jìn)行同步字校驗。為此,本文在全彩LED控制系統(tǒng)信號傳輸中采用了與高速時鐘采樣" title="采樣">采樣進(jìn)行同步接收的LVDS傳輸方案,從而省去了同步字和控制信號,且增加了板子的集成度,并使整個系統(tǒng)信號傳輸穩(wěn)定,成本降低。

1 基于LVDS的數(shù)據(jù)傳輸硬件設(shè)計

1.1 全彩LED控制系統(tǒng)

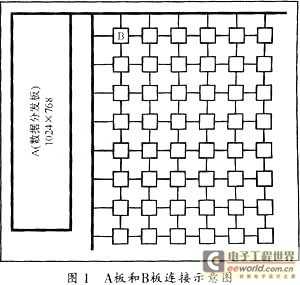

全彩是指顯示屏上每像素的顏色顯示采用24bit,共顯示16 777 216種顏色。而現(xiàn)今許多圖形顯示只支持8 bit顏色值,只能顯示256種顏色。本設(shè)計的全彩LED屏可與計算機(jī)VGA顯示屏實時同步輸出顯示,并可任意播放圖片、文字、廣播、電視、錄像、VCD以及各種三維動畫。此外還能完全適應(yīng)戶外各種惡劣性環(huán)境(如防腐,防水,防潮,防雷,抗震等)。LED屏的顯示采用1024×768像素,數(shù)據(jù)量為1024×768×60(幀)×24=1132462080 bit,每個掃描板能控制128×128像素,所以完整顯示A板的數(shù)據(jù)需要8×6=48塊掃描板,A板的LVDS信號一共使用6路,每路四對(CLOCK+R-C-BDATA(3對));B板則使用兩路,一路輸入,一路輸出,每路都由(CLOCK+R-G-BDATA (3對))構(gòu)成。圖1所示是A板和B板的連接示意圖,其中A板為數(shù)據(jù)分發(fā)板,B板為掃描板。

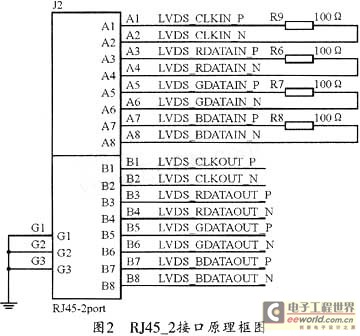

1.2 LVDS信號傳輸連接電路

圖2為RJ45_2接口電路連接圖。使用LVDS信號傳輸時,在接收端應(yīng)有4個100Ω的匹配電阻與差分線阻抗相匹配,以減少阻抗不匹配所導(dǎo)致的共模噪聲增加和電磁干擾(EMI)。值得注意的是,在走線時,差分線的長度應(yīng)該保持一致,且差分線應(yīng)彼此盡量靠近以減少反射,并應(yīng)盡量減少信號路徑中的過孔數(shù)量與阻抗的不均勻,此外,還要把LVDS和TTL信號層分開以防止串?dāng)_。

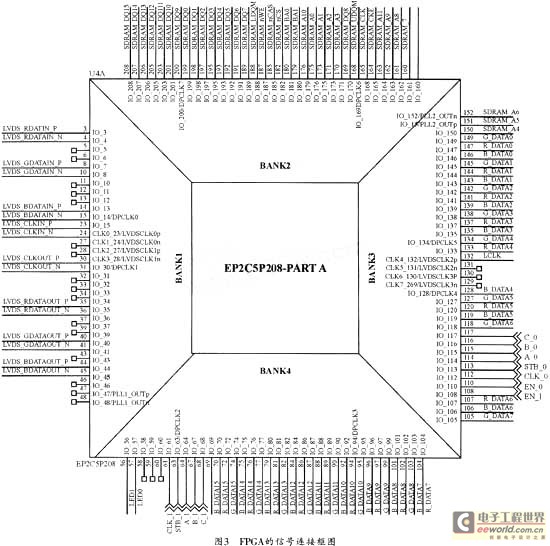

圖3為FPGA的連接電路。本全彩LED控制系統(tǒng)之所以選用FPGA作為測試平臺,其原因首先是FPGA可以快速轉(zhuǎn)向最終原型,其次是它的可再編程能力強(qiáng),可以通過軟件而不是硬件來滿足設(shè)計的改進(jìn),而最重要的一點則是因為FPGA提供了大量的資源,包括SDRAM驅(qū)動、ZBT SRAM驅(qū)動和快速傳輸邏輯接口(LVDS)等。EP2C5Q208C8一共有208個管腳,分成4個BANK,BANK1的I/O接口用于差分信號線,BANK2上的I/O接口與SDRAM相連接,BANK3和BANK4用來連接LED顯示屏的數(shù)據(jù)和控制信號。

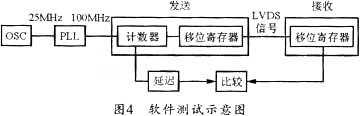

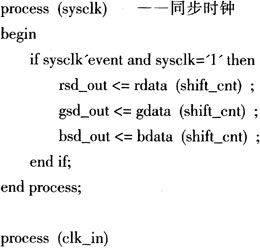

2 基于LVDS的傳輸軟件

硬件電路連好之后,便可用VHDL語言編寫相應(yīng)的測試代碼。可通過計數(shù)器生成RGB數(shù)據(jù)信號,然后把數(shù)據(jù)從FPGA經(jīng)差分線輸出,再經(jīng)過10米長的雙絞線輸入到FPGA,從而檢驗LVDS信號傳輸?shù)姆€(wěn)定性,其示意圖如圖4所示。部分VHDL代碼如下:

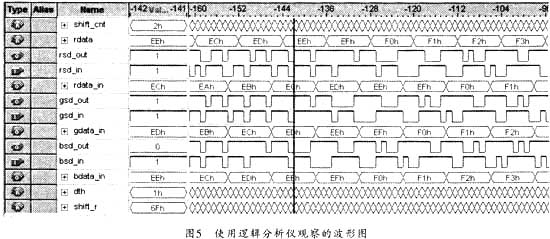

圖5所示是用邏輯分析儀觀察到的波形圖。從圖5可以看出,通過LVDS信號線可使此系統(tǒng)在10米處穩(wěn)定地傳輸100 Mbps的信號。

3 結(jié)束語

高速信號傳輸對PCB板上信號的穩(wěn)定性要求越來越高,為此,本文給出了用LVDS信號進(jìn)行高速數(shù)據(jù)傳輸?shù)姆桨福⒁殉晒ν瓿蓽y試。結(jié)果表明:在10米傳輸距離上,該方案可以穩(wěn)定地傳輸高達(dá)100 MBps的數(shù)據(jù)信號,成本低,功耗低和集成度高。