文獻(xiàn)標(biāo)識碼: A

文章編號: 0258-7998(2014)08-0044-04

隨著科學(xué)技術(shù)的高速發(fā)展,高速處理器、多媒體以及網(wǎng)絡(luò)技術(shù)等要求傳輸?shù)臄?shù)據(jù)量越來越大,需要的傳輸速度越來越快,尤其是現(xiàn)在許多設(shè)備要求具有長距離傳送數(shù)據(jù)的能力,以確保可以傳輸千米以上的距離[1]。普通的并行總線由于自身的劣勢,無法適用于長距離數(shù)據(jù)傳輸?shù)南到y(tǒng)中。

基于串行器/解串器構(gòu)架的LVDS解決方案具有使用簡單、傳輸速度高、抗干擾能力較強(qiáng)和使用節(jié)點(diǎn)少等特點(diǎn),因此可以采用該方案來實(shí)現(xiàn)遠(yuǎn)程高速數(shù)據(jù)傳輸功能[2]。但在一些惡劣的環(huán)境(如超遠(yuǎn)距離或高干擾環(huán)境)中,LVDS數(shù)據(jù)仍然可能出現(xiàn)信號衰減或嚴(yán)重失真。基于此,本文給出了一種針對LVDS遠(yuǎn)程傳輸的延展卡的設(shè)計(jì)方案,將雙絞線傳輸和光纖傳輸相結(jié)合,使數(shù)據(jù)傳輸距離可達(dá)幾千米遠(yuǎn)。

1 系統(tǒng)方案設(shè)計(jì)

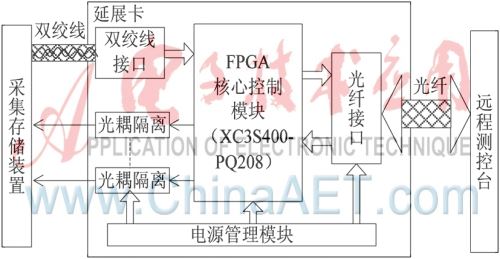

設(shè)計(jì)要求信號以400 Mb/s的速度傳輸2 km以上的距離。根據(jù)設(shè)計(jì)需求和方案合理性,采集存儲系統(tǒng)到延展卡之間采用100 m雙絞線通信,延展卡與遠(yuǎn)程測控臺之間采用2 km光纖通信。總體設(shè)計(jì)如圖1所示,分為FPGA核心控制模塊、雙絞線接口模塊、光纖接口模塊、光耦隔離模塊、電源管理模塊等幾部分。系統(tǒng)指令由光模塊接收,并通過光耦隔離并行發(fā)出;數(shù)據(jù)由雙絞線傳輸并通過光模塊轉(zhuǎn)發(fā)。

圖1 系統(tǒng)總體設(shè)計(jì)

2 硬件設(shè)計(jì)中的關(guān)鍵點(diǎn)

2.1 雙絞線接口設(shè)計(jì)

雙絞線傳輸伴隨著信號大幅度衰減。圖2中波形1為一組隨機(jī)LVDS信號通過100 m電纜傳輸后的波形。顯然有部分電平越不過零點(diǎn)門限,在接收端加上電纜均衡器CLC014,將之與SN65LV1224搭配使用,可以解決這個(gè)問題。CLC014最大可以均衡120 m的第五類未屏蔽雙絞線。

圖2 無均衡器時(shí)波形(上)與加均衡器后波形(下)

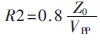

如圖3所示為添加均衡器后的雙絞線接收模塊電路,R1和R2為匹配電阻,可參照公式

計(jì)算阻值。本系統(tǒng)雙絞線特性阻抗Z0為100 Ω,R1、R2的阻值根據(jù)輸出電平調(diào)整為25 Ω。隔直電容C1的容值為0.01 μF,為經(jīng)雙絞線衰減后的信號提供交流耦合。CLC014的輸出取自輸出晶體管的集電極,由正電源通過二極管和50 Ω的電阻建立PECL電平,從而獲得理想的輸出波形。電阻R3為媒質(zhì)終端匹配電阻,阻值為100±20 Ω,用于防止信號在媒質(zhì)終端發(fā)生反射,減少電磁,布局時(shí)要靠近接收器輸入端放置。圖2中波形2為增加均衡器之后的信號波形,可見波形恢復(fù)正常,高低電平明顯。

圖3 雙絞線接收

2.2 光纖接口設(shè)計(jì)

光模塊選用OCM3723,其輸入信號電平范圍為1.5~2.3 V,而LVDS串化器SN65LV1023的輸出幅值約800 mV,所以需要增加驅(qū)動器CLC006,將信號增強(qiáng)到2 V之后再輸入光模塊。接收命令時(shí),解串器SN65LV1224與均衡器CLC014搭配,將光模塊輸出的命令信號重新組構(gòu),并恢復(fù)其強(qiáng)度。光纖接收與發(fā)送部分電路如圖4所示。

(a)光纖接收

(b)光纖發(fā)送

圖4 光纖接收與光纖發(fā)送電路

OCM3723屬于LVPECL接口電平,而CLC014和CLC006屬于PECL接口電平,所以采用交流耦合方式連接。PECL/LVPECL的輸出共模電壓需固定在VCC-1.3 V上,直流偏置電阻需提供14 mA到地的通路,所以R4=(VCC-1.3 V)/14 mA,當(dāng)VCC=3.3 V時(shí),R4=142 Ω,應(yīng)用中為了讓輸出波形達(dá)到最佳,R4可以從142 Ω~200 Ω之間選取。PECL/LVPECL輸入直流偏壓要固定在VCC-1.3 V上,輸入阻抗應(yīng)等于傳輸線路阻抗,可列出方程 =VCC-1.3 V且R5||R6=50 Ω,當(dāng)VCC=3.3 V時(shí),R5=82 Ω,R6=130 Ω。因?yàn)镃LC014輸入和CLC006輸出在其芯片內(nèi)部有偏置電路,所以無需設(shè)計(jì)外部偏置網(wǎng)絡(luò)。

=VCC-1.3 V且R5||R6=50 Ω,當(dāng)VCC=3.3 V時(shí),R5=82 Ω,R6=130 Ω。因?yàn)镃LC014輸入和CLC006輸出在其芯片內(nèi)部有偏置電路,所以無需設(shè)計(jì)外部偏置網(wǎng)絡(luò)。

光纖發(fā)送端和接收端數(shù)據(jù)波形如圖5所示。可以看出通過2 km光纖之后,信號波形仍然比較標(biāo)準(zhǔn)。對比雙絞線端接收的數(shù)據(jù)波形,不難發(fā)現(xiàn)光纖比雙絞線的傳輸效果好很多。

(a)光纖發(fā)送端 (b)接收端

(橫軸坐標(biāo)為50 ns/格,縱軸坐標(biāo)為500 mV/格)

圖5 數(shù)據(jù)波形

2.3 光耦隔離接口設(shè)計(jì)

因?yàn)橄到y(tǒng)指令切換的頻率較數(shù)據(jù)傳輸?shù)乃俾实偷枚啵詾榱撕喕娐罚黾又噶顐鬏數(shù)目煽啃裕?jīng)過FPGA重組后的指令由5條并行線傳輸。指令接口部分采用高速10 MB/s光電耦合器HCPL-2631進(jìn)行電氣隔離,6.3 mA電流即可導(dǎo)通工作,雙通道單向傳輸,真正實(shí)現(xiàn)前后級互不干擾,提高了接口的可靠性。圖6所示為HCPL-2631的單路傳輸接口電路。當(dāng)FPGA接口為邏輯0時(shí),HCPL-2631內(nèi)部電路導(dǎo)通輸出低電平;當(dāng)FPGA接口為邏輯1時(shí),HCPL-2631內(nèi)部電路不導(dǎo)通,輸出高電平。

圖6 光耦隔離接口電路

3 邏輯設(shè)計(jì)中的關(guān)鍵點(diǎn)

3.1 防止指令誤判

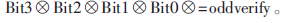

為了防止接收端指令的誤判,首先對指令進(jìn)行奇校驗(yàn)。設(shè)計(jì)時(shí)將指令中1的個(gè)數(shù)定為奇數(shù)個(gè)。接收指令的奇偶性判斷是通過對指令的各個(gè)數(shù)據(jù)位進(jìn)行異或操作(XOR)實(shí)現(xiàn)的,即:

只有當(dāng)oddverify為1時(shí),才認(rèn)為當(dāng)前傳輸?shù)氖怯行е噶?并用5位數(shù)組f_state重新定義當(dāng)前指令[3]。新定義的f_state指令信號需再經(jīng)過雙重計(jì)數(shù)器消抖才能最終輸出。外部計(jì)數(shù)器對所有有效指令進(jìn)行消抖計(jì)數(shù),而內(nèi)部計(jì)數(shù)器針對某一個(gè)指令進(jìn)行消抖計(jì)數(shù),消抖后的state指令為最終的5線指令。

圖7所示為部分指令判別的時(shí)序仿真圖。從圖中可以看出,“0110001111”經(jīng)過奇校驗(yàn)后被過濾,指令切換時(shí)出現(xiàn)的誤指令“0101100110”被外部計(jì)數(shù)器隔斷,之后傳輸中的誤碼指令“0110011111”也被內(nèi)部計(jì)數(shù)器過濾。

圖7 指令判別時(shí)序仿真圖

3.2 LVDS接口時(shí)鐘與采集速率匹配問題

LVDS接口時(shí)鐘是固定的,而采集設(shè)備的采集速率根據(jù)需求可控,二者速度不匹配,所以數(shù)據(jù)鏈路中經(jīng)常出現(xiàn)傳輸空白;如果數(shù)據(jù)采用間歇式傳輸,則LVDS芯片中斷后再同步會有500 μs的數(shù)據(jù)丟失。

針對這一問題,設(shè)計(jì)中引入無效數(shù)與有效數(shù)交替發(fā)送的模式。當(dāng)鏈路中無數(shù)據(jù)傳輸時(shí),F(xiàn)PGA自編譯無效數(shù)據(jù),使鏈路保持通信狀態(tài)。LVDS芯片有10位數(shù)據(jù)管腳,有效數(shù)據(jù)占用了其中的低8位,高2位作為區(qū)別有效數(shù)和無效數(shù)的標(biāo)志位。定義“01”為有效數(shù)標(biāo)志,“00”為無效數(shù)標(biāo)志。實(shí)驗(yàn)證明無效數(shù)發(fā)送“00011111”同步穩(wěn)定性高,原因可能是“00011111”配合標(biāo)志位“00”正好構(gòu)成同步碼“0000011111”,而LVDS芯片同步的過程就是不斷識別同步碼的過程。所以這樣不但解決了速度匹配問題,也提高了系統(tǒng)數(shù)據(jù)鏈路的可靠性。

3.3 光纖接口LVDS失鎖問題

光模塊與LVDS接收模塊之間連續(xù)傳輸“FF”數(shù)據(jù)出現(xiàn)失鎖,表現(xiàn)為SN65LV1224的鎖存標(biāo)志LOCK出現(xiàn)高電平脈沖。經(jīng)分析,交流耦合電路中的耦合電容隔斷了信號的直流分量,因此LVDS接收端只能觀察到輸入信號的前后沿。當(dāng)數(shù)據(jù)1連續(xù)出現(xiàn)時(shí),電容會造成接收端電壓下降,信號產(chǎn)生抖動[4]。所以連續(xù)傳輸“FF”數(shù)據(jù)容易造成LVDS失鎖。一種高效的解決辦法是使用8B/10B編碼實(shí)現(xiàn)直流平衡,或者選用帶有8B/10B編碼的串/并轉(zhuǎn)換芯片[5]。為了配合前端邏輯設(shè)計(jì),同時(shí)考慮到只有傳輸“FF”時(shí)才會出現(xiàn)失鎖的情況,本設(shè)計(jì)中采取的優(yōu)化措施是將“FF”數(shù)據(jù)轉(zhuǎn)變?yōu)椤?F”數(shù)據(jù)發(fā)送,即將二進(jìn)制8位數(shù)據(jù)“11111111”轉(zhuǎn)變?yōu)椤?0011111”發(fā)送,且高兩位標(biāo)志位定義為“10”,發(fā)送的10位LVDS數(shù)據(jù)為“1000011111”,這與同步碼數(shù)據(jù)近似。光纖數(shù)據(jù)鏈路中共有3種數(shù)據(jù)類型,圖8為優(yōu)化后的數(shù)據(jù)編碼發(fā)送流程圖。經(jīng)過大量測試,優(yōu)化后的數(shù)據(jù)編碼方式能夠有效解決LVDS失鎖的問題。

4 試驗(yàn)方法與測試

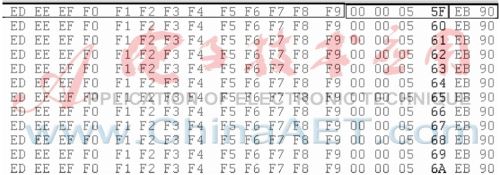

針對總體設(shè)計(jì)方案,配合數(shù)據(jù)采集存儲裝置和遠(yuǎn)程測控臺,對系統(tǒng)進(jìn)行惡劣環(huán)境下數(shù)據(jù)傳輸?shù)男阅軠y試,雙絞線長度為100 m,光纖長度為2 km。采集存儲裝置啟動自發(fā)數(shù)模式,測試數(shù)據(jù)幀格式為:1~250 B是0~249的遞加數(shù),251~254 B是32 bit二進(jìn)制幀計(jì)數(shù),255~256 B為同步字EB 90。圖9所示為上位機(jī)接收到的部分?jǐn)?shù)據(jù)截圖,幀結(jié)構(gòu)嚴(yán)格對齊。采用上位機(jī)分析軟件對數(shù)據(jù)進(jìn)行分解,分解報(bào)告顯示傳輸數(shù)據(jù)無誤碼,無丟幀。

圖9 測試數(shù)據(jù)部分截圖

基于LVDS技術(shù)的遠(yuǎn)程數(shù)據(jù)傳輸延展卡的設(shè)計(jì)充分發(fā)揮了雙絞線、光纖以及光電耦合器的接口傳輸優(yōu)勢,并且解決了速度匹配和光纖接口LVDS芯片易失鎖的問題,有效保證了指令的可靠下發(fā)以及數(shù)據(jù)傳輸?shù)臏?zhǔn)確性,成功將數(shù)據(jù)傳輸距離擴(kuò)展至幾千米遠(yuǎn)。該卡抗擾能力強(qiáng),傳輸穩(wěn)定性高,為高速數(shù)據(jù)超遠(yuǎn)距離傳輸開辟了新的領(lǐng)域。

參考文獻(xiàn)

[1] 劉利生,蘇淑靖,張凱琳.基于LVDS的遠(yuǎn)程數(shù)據(jù)傳輸系統(tǒng)[J].儀表技術(shù)與傳感器,2011(12):38-39.

[2] 姚永興,焦新泉,馬培嬌.高可靠性遠(yuǎn)程數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)[J].計(jì)算機(jī)測量與控制,2011,19(8):1968-1971.

[3] 劉欣,張會新.基于LVDS總線的分布式數(shù)據(jù)綜合器測試系統(tǒng)[J].科學(xué)技術(shù)與工程,2013,13(34):10354-10358.

[4] 劉泳銳,張彥軍,劉龍飛.8b/10b編碼實(shí)現(xiàn)LVDS交流耦合傳輸中的直流平衡[J].科學(xué)技術(shù)與工程,2012,12(35):9693-9696,9701.

[5] 何林飛,田佳月,張曉林.基于光纖傳輸?shù)亩嗦犯咚贁?shù)據(jù)采集系統(tǒng)[J].電子技術(shù)應(yīng)用,2013,39(3):77-79.

(收稿日期:2014-03-27)

作者簡介:

甄國涌,男,1971年生,副教授,碩士生導(dǎo)師,主要研究方向:測試系統(tǒng)集成技術(shù)與應(yīng)用軟件技術(shù)。

瞿林,男,1989年生,碩士研究生,主要研究方向:電路與系統(tǒng)、高速數(shù)據(jù)采集。

劉東海,男,1982年生,碩士研究生,主要研究方向:高速數(shù)據(jù)采集。