文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)03-0044-04

0 引言

由于基于ΣΔ調(diào)制技術(shù)的ΣΔ模數(shù)轉(zhuǎn)換器(ADC)易于與數(shù)字芯片集成,并且對(duì)于器件的失配不是很敏感,所以是目前高性能無(wú)線(xiàn)通信和傳感器微弱信號(hào)檢測(cè)電路的首選[1]。采用過(guò)采樣技術(shù)和噪聲整形技術(shù)的調(diào)制器是限制ΣΔ ADC性能的關(guān)鍵模塊,所以設(shè)計(jì)高性能的ΣΔ調(diào)制器是實(shí)現(xiàn)高精度的ΣΔ ADC的必經(jīng)途徑。目前關(guān)于ΣΔ調(diào)制器的研究主要集中于兩階~四階結(jié)構(gòu),這是由于高階的調(diào)制器面臨穩(wěn)定性問(wèn)題。在設(shè)計(jì)低階的調(diào)制器時(shí)可以通過(guò)提高過(guò)采樣率來(lái)部分提高性能[2-3]。然而提高系統(tǒng)過(guò)采樣率會(huì)提高對(duì)運(yùn)放帶寬的要求,增加系統(tǒng)的功耗。在消費(fèi)電子領(lǐng)域,對(duì)于芯片的功耗有一定的限制,所以在較低的功耗下設(shè)計(jì)一種高性能的調(diào)制器很有意義。本文的目標(biāo)是在較低的功耗下設(shè)計(jì)出一種適用于加速度傳感器的高性能ΣΔ調(diào)制器電路。通過(guò)參數(shù)優(yōu)化和建模仿真,在較低的采樣頻率下實(shí)現(xiàn)一種五階單環(huán)一位結(jié)構(gòu)的ΣΔ調(diào)制器電路。利用根軌跡法分析和驗(yàn)證該高階系統(tǒng)的穩(wěn)定性,通過(guò)版圖后仿真結(jié)果顯示提出的五階結(jié)構(gòu)實(shí)現(xiàn)了較高的性能,滿(mǎn)足系統(tǒng)設(shè)計(jì)要求。

1 系統(tǒng)設(shè)計(jì)

圖1是設(shè)計(jì)的五階ΣΔ調(diào)制器原理框圖,該調(diào)制器采用前饋單環(huán)一位結(jié)構(gòu),該結(jié)構(gòu)能夠減小積分器的輸出擺幅,降低對(duì)運(yùn)放的性能和設(shè)計(jì)指標(biāo)要求,提高了系統(tǒng)的線(xiàn)性度。同時(shí)采用前饋結(jié)構(gòu)使得積分器輸出擺幅大大減小,能夠降低系統(tǒng)的功耗,有利于低功耗的設(shè)計(jì)目標(biāo)。表1是經(jīng)過(guò)優(yōu)化的調(diào)制器的各級(jí)系數(shù),包括前饋系數(shù)和各個(gè)積分器的增益因子。

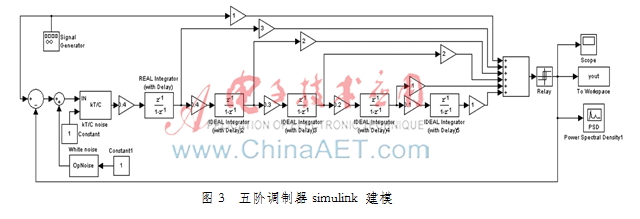

雖然提高階數(shù)能夠提高系統(tǒng)的性能,但是高階系統(tǒng)存在嚴(yán)重的穩(wěn)定性問(wèn)題。為了驗(yàn)證系統(tǒng)的穩(wěn)定性,可以在MATLAB中求解噪聲傳遞函數(shù)的根軌跡曲線(xiàn)來(lái)判斷系統(tǒng)的穩(wěn)定性,結(jié)果如圖2所示。仿真結(jié)果顯示該高階系統(tǒng)是條件穩(wěn)定的,當(dāng)量化器的增益小于0.525時(shí),極點(diǎn)進(jìn)入單位圓外,系統(tǒng)出現(xiàn)穩(wěn)定性問(wèn)題,所以量化器的輸入存在一個(gè)穩(wěn)定范圍,也即調(diào)制器的輸入信號(hào)不能太大,否則會(huì)導(dǎo)致系統(tǒng)不穩(wěn)定。在MATLAB中搭建該五階調(diào)制器的行為級(jí)模型,如圖3所示。其中包含運(yùn)放熱噪聲和第一級(jí)積分器的kT/C噪聲模型,而且在第一級(jí)積分器模型中引入了有限增益帶寬等非理想因素,以便更真實(shí)地模擬實(shí)際調(diào)制器電路的仿真結(jié)果。由于加速度計(jì)傳感器的應(yīng)用頻帶較低,一般在幾百赫茲以?xún)?nèi),所以在過(guò)采樣率為125的情況下,圖3中的調(diào)制器的采樣頻率可以大大降低。在輸入信號(hào)幅度為-1.94 dBFS,信號(hào)頻率488.24 Hz,采樣頻率為250 kHz的條件下,圖3中的65 536點(diǎn)輸出位流頻譜如圖4所示,實(shí)現(xiàn)了大于18位的精度,滿(mǎn)足了加速度計(jì)接口電路中關(guān)于后級(jí)高精調(diào)制器的帶寬和精度要求。

2 電路實(shí)現(xiàn)和版圖后仿

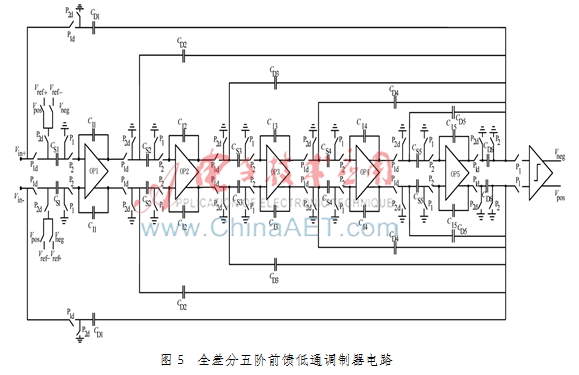

本設(shè)計(jì)的五階低通ΣΔ調(diào)制器電路采用開(kāi)關(guān)電容電路實(shí)現(xiàn),如圖5所示。在設(shè)計(jì)時(shí)采用全差分結(jié)構(gòu)來(lái)消除電路的偶次諧波分量,從而提高整體電路的性能。整體電路由五級(jí)積分器電路、前饋求和電路以及動(dòng)態(tài)鎖存比較器等組成,并由控制時(shí)序P1、P1d、P2、P2d控制開(kāi)關(guān)的開(kāi)啟和關(guān)斷。其中P1d和P2d分別是P1、P2的延遲時(shí)序,這樣設(shè)計(jì)的目的是減小開(kāi)關(guān)關(guān)斷時(shí)的電荷注入引起的噪聲[4]。由于采用了高階調(diào)制結(jié)構(gòu),后級(jí)積分器的噪聲可以經(jīng)過(guò)前級(jí)整形,所以第一級(jí)積分器決定著整體的性能,后級(jí)積分器的帶寬和增益等參數(shù)可以適當(dāng)降低[5]。前饋求和電路采用簡(jiǎn)單的無(wú)源開(kāi)關(guān)電容電路,減小芯片面積和功耗。求和電路在P1相求和,比較器對(duì)輸入差分信號(hào)比較輸出;求和電路在P2相復(fù)位,比較器輸出鎖存。本設(shè)計(jì)的量化范圍Vpp=1.65 V,分辨率為N=18,OSR=125。根據(jù)建模仿真結(jié)果選取CS1=4 pF,第一級(jí)積分器的運(yùn)放積分電容為10 pF。由于后級(jí)電路的噪聲可以通過(guò)前級(jí)抑制,后級(jí)積分器電路的采樣電容可以大大減小,故積分器的負(fù)載電容也等比例減小。

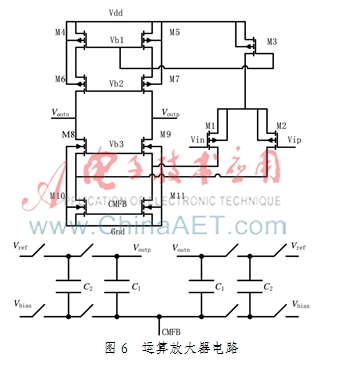

運(yùn)放的有限增益會(huì)改變積分器的極點(diǎn)位置,產(chǎn)生積分泄露,也就改變了系統(tǒng)的噪聲傳遞函數(shù)的極點(diǎn)。通過(guò)行為級(jí)仿真掃描可以確定運(yùn)放的直流增益需大于60 dB才能保證系統(tǒng)的精度。為了簡(jiǎn)化設(shè)計(jì),選擇一級(jí)折疊共源共柵放大器來(lái)實(shí)現(xiàn)積分器電路,運(yùn)放的電路圖如圖6所示。在第一級(jí)積分器負(fù)載電容為10 pF時(shí),仿真得到的運(yùn)放電路直流增益為78 dB,單位增益帶寬約為12 MHz,相位裕度為66°,擺率為15.7 V/μs,功耗約為1.4 mW。后級(jí)積分器的負(fù)載電容等比例縮放,對(duì)運(yùn)放的增益和帶寬要求也大大降低,因此可以降低功耗。后級(jí)4個(gè)運(yùn)放在負(fù)載電容等比例縮小的情況下總體功耗小于1.5 mW。由于采用了一位量化,所以用比較器來(lái)實(shí)現(xiàn)調(diào)制器電容中的一位量化器,實(shí)現(xiàn)輸出數(shù)字信號(hào)。動(dòng)態(tài)比較器具有電路簡(jiǎn)單、速度較快、功耗低的特點(diǎn)。

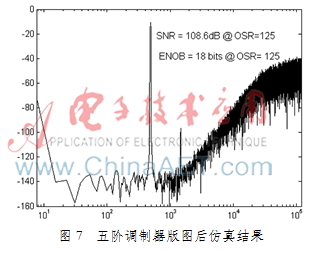

設(shè)計(jì)的五階低通ΣΔ調(diào)制器電路采用CHRT 0.35 μm CMOS工藝實(shí)現(xiàn),系統(tǒng)工作在3.3 V的電源電壓下。通過(guò)提取出版圖寄生參數(shù),在Spectre下進(jìn)行后仿驗(yàn)證,輸入信號(hào)幅度為500 mV的差分正弦信號(hào),信號(hào)頻率488.28 Hz,系統(tǒng)的采樣頻率為250 kHz。將瞬態(tài)仿真的位流導(dǎo)出到MATLAB下進(jìn)行頻率分析,65 536點(diǎn)的FFT結(jié)果如圖7所示。系統(tǒng)的信噪比達(dá)到108.6 dB,有效位數(shù)約為18位,總體功耗3.4 mW。由于開(kāi)關(guān)和運(yùn)放的非線(xiàn)性以及版圖的對(duì)稱(chēng)性問(wèn)題導(dǎo)致圖7中出現(xiàn)了3次諧波失真。

3 結(jié)束語(yǔ)

本文在CHRT 0.35 μm CMOS工藝下實(shí)現(xiàn)了一種用于加速度計(jì)信號(hào)檢測(cè)的高精度ΣΔ調(diào)制器。后仿真結(jié)果表明在1 kHz的信號(hào)帶寬內(nèi),實(shí)現(xiàn)了約18位的有效位數(shù),整體功耗只有3.4 mW。通過(guò)后仿真結(jié)果和行為級(jí)建模的結(jié)果對(duì)比可以證明設(shè)計(jì)的五階單環(huán)調(diào)制器電路實(shí)現(xiàn)了設(shè)計(jì)目標(biāo),達(dá)到了性能要求。

參考文獻(xiàn)

[1] 范軍,黑勇,陳鋮穎.一種采用斬波——穩(wěn)零技術(shù)的低功耗Σ-Δ調(diào)制器的設(shè)計(jì)[J].微電子學(xué)與計(jì)算機(jī),2011,28(11):76-80.

[2] 劉燕娟,程?hào)|方.用于電池電量測(cè)量的Delta-Sigma調(diào)制器設(shè)計(jì)[J].微電子學(xué)與計(jì)算機(jī),2013,30(7):82-85.

[3] Chen Hsinliang,Chen Po-sheng,Chiang Jen-shiun.A low-offset low-noise sigma-delta modulator with pseudorandom chopper-stabilization techniques[J].IEEE Transactions on circuits and systems-I:Regular Papers,2009,56(12):2533-2543.

[4] LEE K L,MEYER R G.Low-distortion switched-capacitor filter design techniques[J].IEEE Journal of Solid-State Circuits,1985,SC-20(6):1103-1112.

[5] 張永來(lái).18位精度音頻Sigma-Delta ADC的設(shè)計(jì)[D].哈爾濱:哈爾濱工業(yè)大學(xué),2013.