文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)04-0116-03

中文引用格式:彭海,高俊雄,王耘波.一種應(yīng)用于生物識(shí)別領(lǐng)域的AES算法[J].電子技術(shù)應(yīng)用,2015,41(04):116-118

0 引言

生物識(shí)別技術(shù)方便、快捷、安全可靠,已被廣泛應(yīng)用于部隊(duì)、政府機(jī)關(guān)、高檔小區(qū)等對(duì)安全系數(shù)要求較高的場(chǎng)合,并且呈快速發(fā)展的趨勢(shì)。然而隨著生物識(shí)別技術(shù)的大量應(yīng)用,人們對(duì)生物識(shí)別技術(shù)的安全性和隱私問題的關(guān)注也越來越多[1]。生物識(shí)別技術(shù)一般對(duì)生物特征(如指紋、虹膜等)進(jìn)行取樣,提取其唯一特征并且轉(zhuǎn)化為特征模板,根據(jù)特征模板進(jìn)行匹配。特征模板就像生物識(shí)別技術(shù)里的“鑰匙”,一旦被修改將直接影響其識(shí)別結(jié)果。因此,采集模板時(shí)利用AES加密算法對(duì)模板數(shù)據(jù)進(jìn)行加密,進(jìn)行識(shí)別時(shí)取出加密后的模板并將其解密。這種以AES算法實(shí)現(xiàn)對(duì)模板數(shù)據(jù)的加密可大大提高生物識(shí)別的安全性。生物識(shí)別系統(tǒng)在識(shí)別時(shí)往往要遍歷所有模板,而由于用戶基數(shù)龐大,數(shù)據(jù)庫中一般存在大量的特征模板,因此系統(tǒng)對(duì)解密的速度要求非常高。

AES加密算法由美國國家標(biāo)準(zhǔn)與技術(shù)研究所(NIST)在2002年建立,它可以使用128 bit、192 bit或256 bit密鑰,并用128 bit(16 B)分組加密和解密數(shù)據(jù)。現(xiàn)階段AES加密主要通過軟件編程或硬件邏輯實(shí)現(xiàn)。采用軟件編程實(shí)現(xiàn)的方法具有成本低、靈活的特點(diǎn),但軟件實(shí)現(xiàn)的AES易被修改,且速度較慢;采用硬件邏輯實(shí)現(xiàn)的AES加密算法除了高效和安全外,還保證了很高的速度,所以在生物識(shí)別領(lǐng)域十分適用。本文主要論述了在FPGA硬件平臺(tái)下實(shí)現(xiàn)的一種大吞吐量256 bit密鑰的AES算法,因AES加密與解密的過程基本相同,故主要論述了AES算法的解密過程在FPGA上的實(shí)現(xiàn)。

1 AES算法簡介

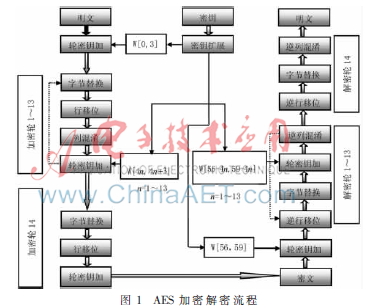

AES算法是基于置換和代替的。置換是指數(shù)據(jù)的重新排列,而代替是用一個(gè)單元數(shù)據(jù)替換另一個(gè)。圖1顯示了AES(256 bit)加密解密的完整流程。

AES加密算法把輸入的128 bit數(shù)據(jù)看成是一個(gè)名為State狀態(tài)矩陣的4×4的字節(jié)矩陣。加密過程就是對(duì)State狀態(tài)矩陣進(jìn)行多輪操作[2]。算法開始前首先構(gòu)造用于加密的兩個(gè)表,一個(gè)是用于字節(jié)替換的S-box表,另一個(gè)是用于產(chǎn)生輪密鑰的密鑰調(diào)度表。算法首先進(jìn)行AddRoundKey(輪密鑰加),即用密鑰調(diào)度表中的前4行對(duì)State矩陣進(jìn)行異或操作。然后是AES加密算法的主循環(huán),循環(huán)的次數(shù)由輸入密鑰的長度決定,如密鑰位數(shù)為256 bit,則循環(huán)總輪數(shù)為14輪。AES算法的加密主循環(huán)每輪對(duì)State狀態(tài)矩陣執(zhí)行4個(gè)不同的操作,分別是SubBytes(字節(jié)替換)、ShiftRows(行移位變換)、MixColums(列混淆變換)和AddRoundKey(輪密鑰加),其中最后一輪不進(jìn)行ShiftRows(行移位變換)。字節(jié)替換是指通過S盒對(duì)狀態(tài)矩陣進(jìn)行替換,行移位變換是指狀態(tài)矩陣的每一行進(jìn)行循環(huán)移位,列混淆變換主要用到了GF28域上的乘法和加法運(yùn)算,而輪密鑰加是簡單的異或運(yùn)算。AES解密主循環(huán)是加密循環(huán)的逆過程,解密主循環(huán)中也有對(duì)應(yīng)的逆變換:Inv_SubBytes(逆字節(jié)替換)、Inv_ShiftRows(逆行移位變換)、Inv_MixColumns(逆列混淆變換),這些變換均可看成加密主循環(huán)中4個(gè)變換的逆變換。

2 AES算法的FPGA實(shí)現(xiàn)

2.1 FPGA技術(shù)簡介

現(xiàn)場(chǎng)可編程門陣列FPGA(Field Programmable Gate Array)是美國Xilinx公司于1984年首次開發(fā)的一種通用型用戶可編程器件。FPGA既具有門陣列器件的高集成度和通用性,又有可編程邏輯器件的靈活性。

FPGA結(jié)構(gòu)靈活,其邏輯單元、可編程內(nèi)部連線和I/O單元都可由用戶編程,可實(shí)現(xiàn)任何邏輯功能,滿足各種設(shè)計(jì)需求。其速度快、功耗低、通用性強(qiáng)的特點(diǎn)適用于復(fù)雜系統(tǒng)的設(shè)計(jì)[3]。FPGA技術(shù)還可以實(shí)現(xiàn)動(dòng)態(tài)配置、在線系統(tǒng)重構(gòu)(可以在系統(tǒng)運(yùn)行的不同時(shí)刻,按需要改變電路的功能,使系統(tǒng)具備多種空間相關(guān)或時(shí)間相關(guān)的任務(wù))及硬件軟化、軟件硬化等功能。

2.2 使用FPGA實(shí)現(xiàn)AES算法

2.2.1 系統(tǒng)的總體結(jié)構(gòu)

根據(jù)AES算法輪操作的特點(diǎn),本文采取基本迭代與串行緩存相結(jié)合的方法,系統(tǒng)總體實(shí)現(xiàn)框圖如圖2所示。通過14個(gè)AES解密模塊并行使用,大大提高了吞吐率,其中每個(gè)AES解密模塊采用基本迭代的方法,即所有輪次復(fù)用一個(gè)輪函數(shù),每個(gè)時(shí)鐘周期完成一次輪操作,14個(gè)時(shí)鐘周期完成一個(gè)分組運(yùn)算。

解密數(shù)據(jù)時(shí),首先讓密文數(shù)據(jù)依次進(jìn)入串行緩存,串行緩存的深度與AES算法的輪數(shù)相同(為14),進(jìn)入串行緩存的數(shù)據(jù)依次進(jìn)入AES解密模塊進(jìn)行解密。第一個(gè)時(shí)鐘周期,讓密文數(shù)據(jù)進(jìn)入Data_buffer1,然后啟動(dòng)第一個(gè)AES解密模塊AES1;第二個(gè)時(shí)鐘周期,讓新的密文數(shù)據(jù)進(jìn)入Data_buffer2,然后啟動(dòng)第二個(gè)AES解密模塊AES2;依此類推,往復(fù)循環(huán)。14個(gè)AES解密模塊的啟動(dòng)順序如圖3所示。

每經(jīng)過14個(gè)時(shí)鐘周期,將每個(gè)AES解密模塊的結(jié)果依次移位輸出。采用這種結(jié)構(gòu)實(shí)現(xiàn)的AES解密算法雖然消耗了不少FPGA的內(nèi)部資源,但數(shù)據(jù)無需等待,可以源源不斷地進(jìn)入解密模塊,整個(gè)解密過程的速度僅僅取決于單個(gè)AES解密模塊的工作頻率與數(shù)據(jù)輸入的速率,使得系統(tǒng)的吞吐率大大提高。考慮到FPGA內(nèi)部資源豐富,可以犧牲部分資源來換取速度。

2.2.2 AES解密模塊的實(shí)現(xiàn)

AES解密前,首先要進(jìn)行密鑰擴(kuò)展。密鑰擴(kuò)展是將初始密鑰作為種子密鑰,經(jīng)過字節(jié)代換、字節(jié)移位、輪常數(shù)計(jì)算、字節(jié)異或等過程,計(jì)算產(chǎn)生14輪迭代所需的輪密鑰。密鑰擴(kuò)展實(shí)現(xiàn)框圖如圖4。有文獻(xiàn)提出計(jì)算密鑰時(shí)密鑰擴(kuò)展和加密過程同步執(zhí)行,這樣做會(huì)節(jié)約FPGA的存儲(chǔ)器資源。但考慮到密鑰不需要經(jīng)常更換,而且FPGA存儲(chǔ)器資源豐富,有足夠的空間存放子密鑰,所以本文決定在解密前先進(jìn)行密鑰擴(kuò)展,然后將產(chǎn)生子密鑰存放在RAM中,根據(jù)使用需要從RAM中讀取密鑰。這種方法易于實(shí)現(xiàn),且靈活性強(qiáng),產(chǎn)生好的密鑰調(diào)度表在種子密鑰不變的情況下都可以供其他模塊使用。

密鑰擴(kuò)展完成后,就可以開始進(jìn)行解密。256 bit的AES解密過程總共需要14輪,除最后一輪外每輪需要進(jìn)行字節(jié)替換、逆行移位、輪密鑰加、逆列混淆等4個(gè)操作,最后一輪不需要進(jìn)行輪密鑰加。其實(shí)現(xiàn)框圖如圖5所示。

逆行移位(Inv_ShiftRow)采用簡單的組合邏輯即可實(shí)現(xiàn);逆字節(jié)替換(Inv_SubBytes)利用FPGA內(nèi)部的分布式RAM實(shí)現(xiàn),將逆S_BOX的值預(yù)先存入到RAM中,在進(jìn)行逆字節(jié)替換時(shí),以字節(jié)的高4位和低4位作為地址即可讀出要替換的值,這樣既避免了復(fù)雜的組合邏輯,又提高了系統(tǒng)的運(yùn)行頻率;輪密鑰加(AddKey)為簡單的異或運(yùn)算;逆列混淆(Inv_MixCol)的實(shí)現(xiàn)采用了將復(fù)雜的GF28域乘法逐次分解為基礎(chǔ)的GF28域乘法的方法,使整個(gè)過程易于在FPGA中實(shí)現(xiàn)。

3 實(shí)驗(yàn)結(jié)果

本設(shè)計(jì)在Xilinx公司的XC7A200T-2芯片上進(jìn)行驗(yàn)證,圖6給出了系統(tǒng)的在Isim仿真環(huán)境下的仿真圖。

輸入密文為16進(jìn)制數(shù)8960494b9049fceabf456751cab-7a28e,密鑰為16進(jìn)制數(shù)1f1e1d1c1b1a1918171615141312-

11100f0e0d0c0b0a09080706050403020100,14個(gè)周期后輸出解密后的明文為16進(jìn)制數(shù)ffeeddccbbaa998877665544-33221100。經(jīng)驗(yàn)證,該解密過程完全正確。

在ISE13.6環(huán)境下代碼在綜合后頻率可達(dá)到236.9 MHz,由于采用串行緩存的方法,數(shù)據(jù)可以持續(xù)加密,無需等待上一個(gè)數(shù)據(jù)加密完。經(jīng)計(jì)算理論吞吐量可以達(dá)到30.3 Gb/s,完全適用于各個(gè)應(yīng)用場(chǎng)合的需要。

4 結(jié)論

采用FPGA實(shí)現(xiàn)AES算法可以大幅度提高加密解密速度,并且具有開發(fā)周期短、易于實(shí)現(xiàn)的特點(diǎn);采用本方法實(shí)現(xiàn)的AES算法雖然占用了較多的FPGA資源,但加密解密速度得到大大的提高,吞吐量可達(dá)到30.3 Gb/s,完全滿足現(xiàn)行生物識(shí)別技術(shù)的要求,能廣泛應(yīng)用于虹膜識(shí)別技術(shù)及指紋識(shí)別技術(shù)等領(lǐng)域,應(yīng)用前景廣闊。

參考文獻(xiàn)

[1] 趙洋.生物識(shí)別系統(tǒng)中的模板安全分析[J].中國安防,2012,3(3):99-104.

[2] DANMEN J,RIIJMEN V.AES proposal:rijndael.AES algo-rithm submission.[EB/OL](1999-09-03)[2014-12-23].http://www.nist.gov/aes.

[3] Clive Max Maxfield.FPGA設(shè)計(jì)指南:器件、工具和流程[M].北京:人民郵電出版社,2007.