文獻標識碼: A

文章編號: 0258-7998(2015)01-0057-03

0 引言

在現(xiàn)代的科學實驗、雷達、通信、測試與控制系統(tǒng)中,往往需要高精度的多路數(shù)字脈沖信號[1]作為測試或者時序控制信號。目前科研領域使用的數(shù)字可編程數(shù)字延遲脈沖發(fā)生器有DG535、BNC Model555以及DEL PDG-2510等進口儀器,其中應用最多的是DG535。DG535作為一種多用途脈沖發(fā)生器,精度高達5 ps,延遲范圍達到0~999.999 999 999 995 s,可輸出TTL、ECL、NIM和VAR 4種電平且幅度與極性可調(diào),但是DG535僅有4路延遲輸出(脈寬固定),如要同時調(diào)節(jié)脈寬,只能輸出兩路脈沖,適合于需要通道數(shù)目不多的實驗領域,且價格高。綜合考慮,本文采取單片機+可編程邏輯器件的方案,設計一套多路可編程數(shù)字延遲脈沖發(fā)生器系統(tǒng)。該系統(tǒng)可同時輸出7路脈沖,通過串口與上位機連接后,可以實現(xiàn)輸出脈沖的延遲和寬度以及頻率的實時調(diào)節(jié),且能夠多臺設備級聯(lián)使用,必要時還可以脫機工作。

1 系統(tǒng)設計方案

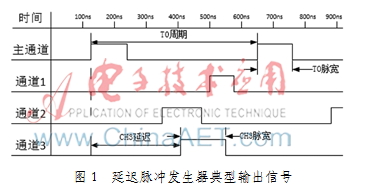

多通道數(shù)字可編程脈沖發(fā)生器典型輸出信號模式如圖1所示。T0是基準門控信號,其他通道CHn(n為1~6)輸出由T0信號的上升沿觸發(fā)。系統(tǒng)主要由單片機、可編程邏輯器件、可編程延遲線和脈沖驅動電路組成。

1.1 可編程邏輯器件

目前主流的可編程邏輯器件主要是復雜可編程邏輯器件(CPLD)和現(xiàn)場可編程門陣列(FPGA)。FPGA的內(nèi)部資源多為觸發(fā)器,適合大規(guī)模的時序電路;而CPLD內(nèi)部寄存器資源豐富,適合組合邏輯多的應用。CPLD內(nèi)部邏輯塊互聯(lián)是集總式的,其特點是等延時,設計完成的電路延時固定,且可預測。FPGA內(nèi)部互聯(lián)為分布式,延時和布局有關。FPGA大部分是基于SRAM編程,編程信息在系統(tǒng)斷電時丟失,每次上電后需從器件外部將編程數(shù)據(jù)重新寫入SRAM,電路也重新布局從而導致延遲不固定,無法預測。

本系統(tǒng)最終采用Altera公司的MAXⅡ系列CPLD-EPM1270T144C3N[2]作為數(shù)字定時器,其包含1 270個邏輯單元(LE),典型等價宏單元數(shù)目為980,速度等級為3級,支持高達300 MHz的內(nèi)部時鐘頻率,其I/O口擺率和驅動能力均可編程,并且可以配置為施密特觸發(fā)器從而提高信號完整性,使用非常方便。時鐘源選用100 MHz的外部有源晶振以減小時鐘抖動從而改善時序品質(zhì)。

可編程邏輯器件的編程語言采用VerilogHDL[3],它是一種基本語法與C語言非常類似的硬件描述語言。設計和仿真平臺分別選擇QuartusⅡ和ModelSim-Altera。前者是Altera公司開發(fā)的PLD設計軟件,后者則是Mentor Graphics公司專為Altera開發(fā)的仿真工具,可以與QuartusⅡ下的工程文件無縫對接,極大提升仿真效率。

1.2 可編程延遲線

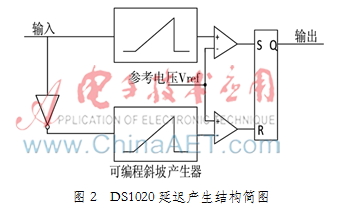

高精度的延遲調(diào)節(jié)通常采用可編程延遲線IC,本系統(tǒng)采用的是Maxim公司的DS1020-15[4]。可編程延遲線是一種數(shù)字模擬混合電路,它對于輸入脈沖的延時作用由其內(nèi)部的數(shù)字寄存器和斜坡產(chǎn)生器決定。DS1020延遲產(chǎn)生結構如圖2所示。

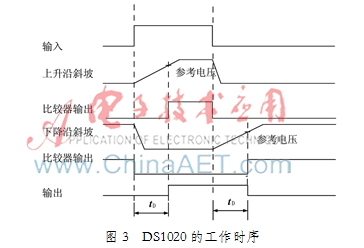

DS1020是一款8位可編程延時電路,共有256級延時,步進調(diào)節(jié)為0.15 ns,它可以通過3線串行或并行模式來編程。DS1020工作時序如圖3所示。圖3中的輸入是待延遲的脈沖信號,參考電壓Vref是其8比特的輸入寄存器(8-bit input register)經(jīng)過DAC后的電壓值。當輸入端出現(xiàn)上升沿時,上方的斜坡發(fā)生器開始工作,輸出由低至高逐漸上升的電壓;當此電壓值跨越參考電壓Vref后,上方的比較器輸出產(chǎn)生由低至高的翻轉,使鎖存器輸出高電平。輸入信號的下降沿到達之后,下方的斜坡產(chǎn)生器開始工作,待其輸出電壓跨越Vref后,下方的比較器輸出低電平翻轉,復位鎖存器輸出低電平。

分析DS1020延遲電路工作原理可知,如果脈沖高電平寬度小于所設的延遲時間值tD,則上升沿斜坡產(chǎn)生器輸出電壓沒有足夠時間充電至Vref,致使延遲失效;另外輸入脈沖高電平寬度必須大于所設延遲時間。

1.3 系統(tǒng)硬件構成

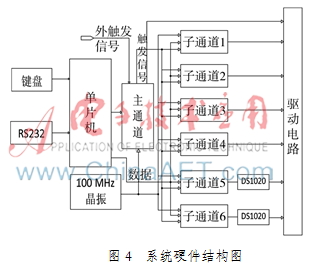

本系統(tǒng)硬件主要由ATmega8A[5]、EPM1270T144C3N、DS1020、ADM3251E和鍵盤等模塊構成,如圖4所示。

單片機負責系統(tǒng)控制,通過EPM1270對輸出脈沖的脈寬和延遲進行配置,通過DS1020對輸出脈沖延遲進行精細調(diào)節(jié),通過RS232與上位機PC通信,也可脫機后改由鍵盤控制操作。除T0外,本系統(tǒng)共有6路子通道輸出,延遲和脈沖寬度的最小分度均為10 ns,能夠勝任大部分應用場合。為了適應對延遲精度有更高要求的場合,增加兩路延遲細調(diào)環(huán)節(jié)。

2 系統(tǒng)軟件

2.1 單片機與CPLD的通信

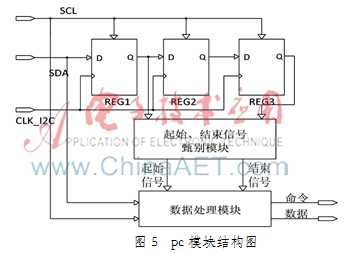

單片機ATmega8A內(nèi)部帶有兩線串行接口TWI模塊,支持高達400 kHz的數(shù)據(jù)傳輸率,只需稍加配置即可與下游器件CPLD通信。CPLD使用QuartusⅡ軟件的宏模塊工具MagaWizrad Plug-In Manager生成虛擬I2C接口,也可手動編寫程序模擬I2C接口完成與單片機的通信[6]。本系統(tǒng)采用手動編程以模擬I2C接口通信,通信速率為40 kHz。控制程序主要任務是起始信號、結束信號的命令和檢測、數(shù)據(jù)的接收等。I2C模塊結構如圖5所示。

CPLD的I2C模塊時鐘源CLK_I2C為100 MHz,采用3個寄存器REG1、REG2和REG3來緩沖從SDA讀入的電平值。當時鐘線SCL為低電平時,3個寄存器全部變?yōu)楦咦钁B(tài),當SCL為高電平時, 數(shù)據(jù)線SDA上的電平值會依次從REG1傳遞至REG3。起始、結束信號甄別模塊內(nèi)部主要是組合邏輯電路,根據(jù)SCL、REG1和REG3的電平鑒別出起始和結束信號。采用3個寄存器以防止干擾信號,即當SCL為高電平時SDA的低電平持續(xù)3個時鐘才認為起始信號到來。數(shù)據(jù)處理模塊在起始信號和結束信號的控制下從數(shù)據(jù)線SDA接收數(shù)據(jù),并從接收到的一連串數(shù)據(jù)中解析出命令和數(shù)據(jù)送至下級處理模塊。

2.2 CPLD脈沖信號的產(chǎn)生

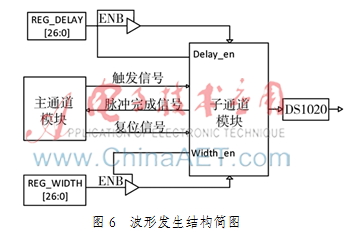

本系統(tǒng)有兩種觸發(fā)方式:內(nèi)部觸發(fā)和外部觸發(fā)。外觸發(fā)信號來自于外部同步設備,內(nèi)觸發(fā)信號則由CPLD內(nèi)部提供。系統(tǒng)脈沖波形發(fā)生結構如圖6所示。

圖6中,主通道模塊負責選擇合適的觸發(fā)模式,并且產(chǎn)生內(nèi)觸發(fā)信號。REG_DELAY是27位的延遲時間寄存器,REG_WIDTH是27位的脈沖寬度時間寄存器,計數(shù)器模塊內(nèi)部是一個27位計數(shù)器,如此高位數(shù)的計數(shù)器占用了CPLD大部分資源,為了節(jié)省資源,采用分時復用的方法完成延遲和脈寬時間的計數(shù)。具體工作過程為:使能計數(shù)器模塊后,觸發(fā)信號的上升沿跳變會使Delay_en信號置位,計數(shù)器模塊裝入REG_LEDAY中的數(shù)據(jù)并開始計數(shù),子通道輸出低電平。計數(shù)達到延遲時間值后子通道輸出翻轉為高電平,Delay_en信號清零,同時Width_en信號置位,計數(shù)器模塊裝入REG_WIDTH中的數(shù)據(jù)并開始計數(shù)。計數(shù)達到脈沖寬度值后輸出翻轉為低電平,同時With_en信號清零,Delay_en置位以等待下一次觸發(fā),并發(fā)送一路脈沖完成信號至主通道模塊。子通道輸出的脈沖信號經(jīng)過DS1020的精細延遲調(diào)節(jié)后再由驅動電路增強驅動能力后成為最終輸出。

2.3 上位機控制軟件

脈沖發(fā)生器通過外觸發(fā)可級聯(lián)工作,控制多達十余臺設備同步工作,連接各設備的電纜可達數(shù)十米,例如一個基體輔助激光解吸/電離飛行時間質(zhì)譜儀(TOF)系統(tǒng)中有激光器、脈沖電源等高壓強電裝置,其浪涌幅度可達上千伏,可能會損壞由RS232與脈沖發(fā)生器連接的PC,其通信接口采用全隔離RS232通信芯片ADM3251E,可用于各種復雜而惡劣的電氣環(huán)境。

上位機控制臺采用C語言編寫的基于API的Windows程序,主通道、各個子通道和延遲細調(diào)的參數(shù)均可調(diào)整,觸發(fā)方式和計算機串口號均可隨時切換,每路子通道的參數(shù)可以單獨裝載也可一鍵裝載,而且各個子通道配備獨立開關。該控制臺還可以把當前下位機的工作狀態(tài)保存起來至本地或者下位機存儲區(qū),并且能夠一鍵讀取本地或者下位機保存的配置文件。“工作狀態(tài)”顯示區(qū)用來實時顯示下位機當前狀態(tài),分別為:未連接、待機和工作中。用戶可以通過“工作”和“停止”按鈕來啟動和關閉下位機。

3 系統(tǒng)測試

考慮到可能的現(xiàn)場強流設備干擾,所有7路數(shù)字脈沖經(jīng)由驅動電路輸出,增加箝位和短路保護。脈沖高度最大5 V,可有效驅動50 ?贅負載,短路電流達50 mA。本設備輸出端從左至右依次為主通道T0、子通道CH1~CH6共7個輸出通道。其中子通道CH5和通道CH6帶有可編程的延遲細調(diào),細調(diào)步長為0.15 ns,最大為255×0.15=38.25 ns。主通道周期T0:2~134 217 728,步長精度100 ns。子通道延遲:0~134 217 728,步長精度10 ns。子通道脈寬:1~134 217 728,步長精度10 ns。

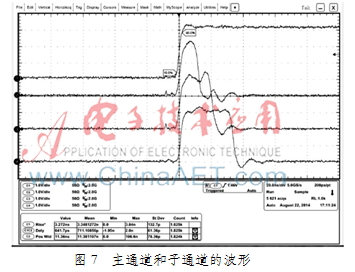

圖7是由數(shù)字熒光示波器DPO5204采集到的主通道TO(圖中C1所示)和子通道(圖中C2所示)的波形圖。圖中顯示系統(tǒng)工作頻率為200 Hz,延遲設置為零,脈寬設置為10 ns,上升沿時間(Rising Time)平均值為3.42 ns。子通道CH1-6相對于主通道T0的固有延遲時間,其平均值為710 ps,抖動標準差為60 ps。

數(shù)字延遲脈沖發(fā)生器的重要參數(shù)是各子通道輸出脈沖相對于TO主通道觸發(fā)脈沖的延遲時間精度,系統(tǒng)誤差主要來自:系統(tǒng)PCB布線、時鐘誤差、器件溫漂、DS1020的誤差等。系統(tǒng)中CPLD輸出的脈沖電平為3.3 V LVTTL電平,通過電平轉換芯片LVC3254后再由驅動器輸出。DS1020的延遲時間由內(nèi)部的斜坡發(fā)生器產(chǎn)生,對電源噪聲和高速開關噪聲十分敏感[4],其電源入口處須用1 ?滋F電容濾波,接地引腳與數(shù)字地平面隔開。輸出波形失真主要是由阻抗不匹配引起的多次反射造成的“振鈴”噪聲,以及相鄰信號線的串擾。CPLD的引腳間距僅10 mil,相鄰傳輸線上的開關動作會產(chǎn)生明顯的串擾攻擊“噪聲”[7]。

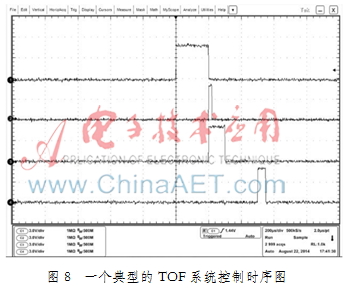

圖8是該系統(tǒng)用于一個典型飛行時間質(zhì)譜儀(TOF)的脈沖時序圖。

圖8中CH1~5分別為驅動樣品噴氣閥、激光器、脈沖電源、偏轉電極和數(shù)據(jù)采集的控制脈沖。首先CH1打開噴氣閥門開始噴入樣品氣體,一定時間(例如200 ?滋s)后氣體到達指定位置,此時CH2啟動激光器電離氣體并由CH3啟動脈沖電源給離子加速,再經(jīng)過一定時間(例如300 ?滋s)后由CH4啟動偏轉電極控制離子軌道,最后離子到達信號采集板CH5啟動數(shù)據(jù)采集。

4 結論

脈沖發(fā)生器是現(xiàn)代測控領域里不可缺少的設備,本系統(tǒng)采用MCU+CPLD的方法設計出一款數(shù)字可編程延遲脈沖發(fā)生器,實用可靠。本系統(tǒng)可同步輸出7個通道脈沖方波(最大5 V), 最小延時分辨為0.15 ns,重復觸發(fā)周期最大可達13 s、脈沖輸出延遲、脈寬調(diào)節(jié)最大可達1.3 s,并提供4種時序觸發(fā)方式。

目前該系統(tǒng)已成功應用于中科院北京化學所、合肥國家同步輻射實驗室、中科院合肥物質(zhì)科學研究院等多家高校和研究單位的飛行時間質(zhì)譜儀(TOF)系統(tǒng),用戶反映良好。

參考文獻

[1] 高輝,陳文通,王金祥,等.可編程器件在納秒級多通道數(shù)字延遲/脈沖發(fā)生器中的應用[J].分析儀器,2002(3):13-17.

[2] Altera Corporation.MAXⅡ device handbook[Z].2008.

[3] Samir Palnitkar.VerilogHDL:A guide to design and syn-thesis[M].北京:電子工業(yè)出版社,2012.

[4] Maxim Corporation.DS1020 programmable 8-bit Silicon delay line[Z].1998.

[5] Atmel Corporation.8-bit Atmel Microcontroller with 8 KB in-system Programmable Flash ATmega8A[Z].2013.

[6] EDA先鋒工作室,王誠,蔡海寧,吳繼華,等.Altera FPGA/CPLD設計基礎篇[M].北京:人民郵電出版社, 2011.

[7] Eric Bogatin.Signal integrity:Simplified[M].北京:電子工業(yè)出版社,2005.