摘 要: 設(shè)計(jì)了一種基于零點(diǎn)優(yōu)化的低功耗ΣΔ調(diào)制器,,該結(jié)構(gòu)不需要傳統(tǒng)ΣΔ調(diào)制器中的數(shù)字抵消邏輯部分,可以采用低增益的運(yùn)算放大器(OTA),,減小了設(shè)計(jì)難度,。此外,設(shè)計(jì)的調(diào)制器中積分器的輸出擺幅大大減小,,積分器的非理想特性得到了抑制,。通過優(yōu)化零點(diǎn)位置,增加了調(diào)制器的穩(wěn)定性和動(dòng)態(tài)范圍,,信噪比和未進(jìn)行零點(diǎn)優(yōu)化相比得到了大大提高,。設(shè)計(jì)的調(diào)制器采用0.35 μm CMOS工藝仿真實(shí)現(xiàn),仿真結(jié)果表明,,在帶寬為500 kHz,、過采樣為16 Mb/s時(shí),信噪比達(dá)到90.9 dB, 功耗僅為3.78 mW,。

關(guān)鍵詞: 低失真,;數(shù)字抵消邏輯;非理想特性,;調(diào)制器;信噪比

模數(shù)轉(zhuǎn)換器(ADC)作為模擬電路和數(shù)字電路的接口,,其精度和速度對(duì)系統(tǒng)的性能起到了決定性作用,。隨著通信產(chǎn)品、電腦產(chǎn)品,、消費(fèi)類電子產(chǎn)品的飛速發(fā)展,,系統(tǒng)對(duì)ADC的要求也與越來越高。

在眾多ADC中,,ΣΔADC能很好地折衷速度和精度,,減少了其中模擬部分的精度,得到了廣泛的應(yīng)用[1],。在一些應(yīng)用中[2],,由于采樣頻率受到了限制,為了達(dá)到高精度,,不得不使用高階調(diào)制器,。但是單環(huán)高階調(diào)制器具有潛在的不穩(wěn)定性,雖然級(jí)聯(lián)結(jié)構(gòu)通過級(jí)聯(lián)多級(jí)低階達(dá)到了高階穩(wěn)定的效果,,得到了廣泛的應(yīng)用,。但是級(jí)聯(lián)結(jié)構(gòu)需要數(shù)字抵消邏輯模塊,,來抵消前級(jí)產(chǎn)生的量化噪聲,以實(shí)現(xiàn)高階整形效果,。因此對(duì)數(shù)字和模擬部分的匹配精度要求很高,,為了達(dá)到高精度,調(diào)制器必須使用高增益,,寬帶寬,,寬擺幅,大擺率的運(yùn)算放大器OTA,,但這樣會(huì)增加系統(tǒng)的功耗和復(fù)雜度,。

本文設(shè)計(jì)了一種基于零點(diǎn)優(yōu)化的低功耗ΣΔ調(diào)制器,該結(jié)構(gòu)對(duì)各級(jí)量化噪聲高階整形,,不再需要傳統(tǒng)ΣΔ調(diào)制器中的數(shù)字邏輯抵消部分,,降低了數(shù)字模擬部分的匹配要求。此外,,本文設(shè)計(jì)的調(diào)制器能減小各級(jí)的輸出擺幅,,提高了穩(wěn)定性和動(dòng)態(tài)范圍。通過優(yōu)化零點(diǎn)位置,,信噪比和未進(jìn)行零點(diǎn)優(yōu)化的情況相比得到了很大地提高,。

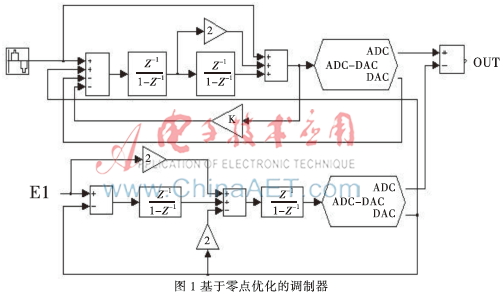

1 基于零點(diǎn)優(yōu)化的調(diào)制器

本文設(shè)計(jì)的基于零點(diǎn)優(yōu)化的ΣΔ調(diào)制器如圖1所示。

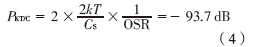

其傳輸函數(shù)為:

從式(1)可以看出,,輸出的第一項(xiàng)和第二項(xiàng)與傳統(tǒng)級(jí)聯(lián)結(jié)構(gòu)一致,,第三項(xiàng)表明E1不止被NTF1整形,還額外乘了(1-STF2),。

理論上,,如果使得STF2=1,可以抵消第一級(jí)的量化噪聲,然而這在實(shí)際中難以實(shí)現(xiàn),。該結(jié)構(gòu)的關(guān)鍵在于選擇第二級(jí)的信號(hào)傳輸函數(shù),,使得1-STF2能對(duì)E1進(jìn)行整形。對(duì)于本文設(shè)計(jì)的調(diào)制器系統(tǒng):

則

因此輸出對(duì)E1也進(jìn)行4階噪聲整形,。從式(3)可以看出,,和傳統(tǒng)的級(jí)聯(lián)結(jié)構(gòu)相比,第二級(jí)的量化噪聲沒有被抵消,,而是進(jìn)行了4階整形,。優(yōu)點(diǎn)在于該結(jié)構(gòu)不需要傳統(tǒng)的數(shù)字抵消邏輯部分。因此不存在數(shù)字模擬部分失配的問題[3],,OTA的設(shè)計(jì)變得更加簡單,。缺點(diǎn)在于增加了總的量化噪聲,信噪比減小了3 dB,。

2 零點(diǎn)優(yōu)化

本文設(shè)計(jì)的調(diào)制器中,,因?yàn)榈谝患?jí)積分器處理的信號(hào)不是傳統(tǒng)級(jí)聯(lián)結(jié)構(gòu)中的E1,使得調(diào)制器的動(dòng)態(tài)范圍有所減小,。通過調(diào)整K的值,可以使得NTF的零點(diǎn)分布在帶寬內(nèi)偏移直流處,,從而進(jìn)行零點(diǎn)優(yōu)化[4],。可以提高系統(tǒng)的動(dòng)態(tài)范圍和信噪比,。

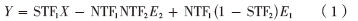

在MATLAB/Simulink下通過行為級(jí)仿真,,發(fā)現(xiàn)在K=0.05時(shí),可以使調(diào)制器達(dá)到最大的動(dòng)態(tài)范圍,,信噪比達(dá)到95.1 dB(如圖2所示),,比未經(jīng)過零點(diǎn)優(yōu)化提高近10 dB。此外,,由于第一級(jí)采用了低失真結(jié)構(gòu),,從圖 3可以發(fā)現(xiàn)除最后一個(gè)積分器外,輸出擺幅都不到0.5 V,。和傳統(tǒng)的級(jí)聯(lián)結(jié)構(gòu)相比,,積分器的擺幅大大減小,降低了功耗,。

3 調(diào)制器參數(shù)選取及電路設(shè)計(jì)

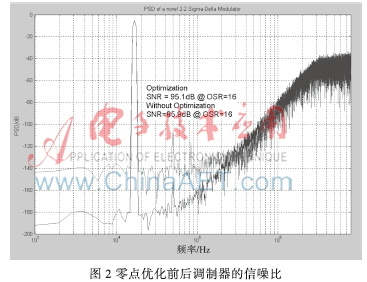

采樣電容會(huì)產(chǎn)生熱噪聲(又稱為KT/C噪聲),,為了減小熱噪聲需要采用較大的采樣電容。運(yùn)算放大器的熱噪聲主要來源于輸入差分對(duì)和電流源管的溝道熱噪聲[1],。當(dāng)Cs=2.4 pF時(shí),,

放大器有限增益以及輸入寄生電容使采樣電容上的差分信號(hào)對(duì)應(yīng)的電荷不能完全轉(zhuǎn)移到積分電容,引起積分泄露,,考慮運(yùn)算放大器的有限增益后,,一階積分器傳輸函數(shù)可表示為:

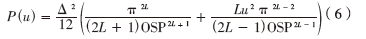

其中,u為OTA增益的倒數(shù),,g為所設(shè)計(jì)積分器的增益。從(5)可以看出,,由于運(yùn)算放大器的增益有限,,傳輸函數(shù)的極點(diǎn)發(fā)生偏移。增加了帶內(nèi)噪聲,,帶內(nèi)噪聲可表示為關(guān)于u的函數(shù),。對(duì)于單環(huán)L階調(diào)制器,加入OTA的有限增益影響后,,其帶內(nèi)噪聲可表示為:

式(6)中第一部分即為量化噪聲,,第二部分所示為運(yùn)算放大器的有限增益引入的噪聲。本文所采用的結(jié)構(gòu)對(duì)第一級(jí)和第二級(jí)的量化誤差均進(jìn)行4階噪聲整形,,所以積分器泄露對(duì)它的影響很小,,這與4階單環(huán)的影響一致,,行為級(jí)仿真發(fā)現(xiàn),對(duì)于本文設(shè)計(jì)的結(jié)構(gòu),,當(dāng)OTA增益大于30 dB時(shí),,積分器泄露對(duì)調(diào)制器的影響很小,;而對(duì)于傳統(tǒng)級(jí)聯(lián)結(jié)構(gòu),,則需要OTA的增益大于70 dB,才能減小積分器泄露的影響(如圖4所示),。設(shè)計(jì)中通常留有一定的裕度,,因此本設(shè)計(jì)中OTA的直流增益定位為40 dB。

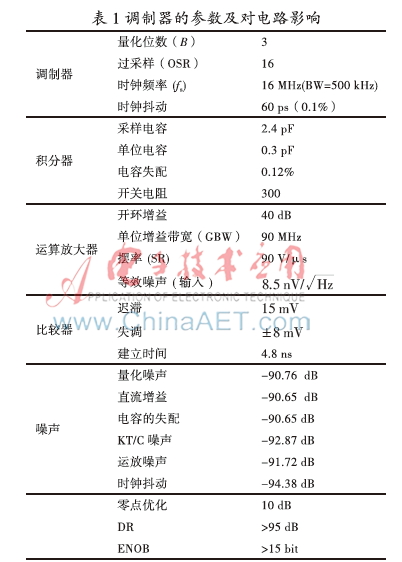

ΣΔ調(diào)制器中積分器的建立時(shí)間和精度由其中OTA的單位增益帶寬和增益決定,,為了保證積分器能在半個(gè)周期內(nèi)完全建立,,必須在小于半個(gè)時(shí)鐘周期內(nèi)建立,且精度達(dá)到99.9%,,據(jù)此,,本文設(shè)計(jì)目標(biāo)定為90 MHz。電路設(shè)計(jì)中的參數(shù)選取和各參數(shù)對(duì)噪聲的影響總結(jié)如表1所示,。

由于對(duì)增益要求不高,,為節(jié)省功耗采用單級(jí)結(jié)構(gòu),此外,,采用增益增強(qiáng)和電流鏡來增加增益和帶寬,,采用AB類輸出增大OTA的擺率。本文設(shè)計(jì)的OTA如圖5所示,。

其增益為:

從式(7)可以看出,,增益提高了1/(1-k)倍,調(diào)整k的大小,,可以改變其增益,。和普通的單級(jí)放大器相比,A點(diǎn)的阻抗和寄生電容都增大,,因而極點(diǎn)位置降低,。為了保證足夠的相位裕度,非主極點(diǎn)必須大于3倍GBW,,即要求

通過式(8)可以得到OTA能達(dá)到的最大增益,。由于調(diào)制器自身也需要非交疊時(shí)鐘,開關(guān)電容電路不需要消耗額外的靜態(tài)功耗,,因此采用開關(guān)電容的共模反饋電路,,值得注意的是,共模反饋環(huán)路的GBW必須大于主放大器的GBW。因此要求gm5必須大于gm1[5],。

本文折衷了增益和帶寬,,選取k=0.8,B=9,。仿真結(jié)果顯示OTA的直流增益為42 dB,,單位增益帶寬為108 MHz(負(fù)載為3.1 pF),相位裕度為62°,,擺率為121 V/μs,,均滿足設(shè)計(jì)要求。在3.3 V電源供電條件下功耗僅為0.75 mW,。

在預(yù)放大器前,,通過一個(gè)開關(guān)電容網(wǎng)絡(luò)實(shí)現(xiàn)輸入信號(hào)和第一級(jí)兩個(gè)積分器輸出之間相加,由于預(yù)放大器一般采用二極管連接的放大結(jié)構(gòu),,輸入管柵漏之間電容(Cgd)的存在,,使得上一個(gè)周期的求和結(jié)果會(huì)影響到下一個(gè)周期,求和結(jié)果會(huì)出現(xiàn)偏差,,需要每個(gè)周期對(duì)其刷新[7],。本文設(shè)計(jì)的求和加法器如圖6所示,Ck1相求和,,Ck2相,,預(yù)放大器的輸入輸出短接,對(duì)Cgd放電,,消除Cgd上存儲(chǔ)電荷對(duì)求和結(jié)果的影響,,實(shí)現(xiàn)高精度求和。

本文采用的比較器中采用的是一種高速高精度低功耗的動(dòng)態(tài)比較器[6],。在16 MHz時(shí)鐘下,,遲滯小于10 mV,建立時(shí)間僅為3 ns,,滿足行為級(jí)仿真要求,。

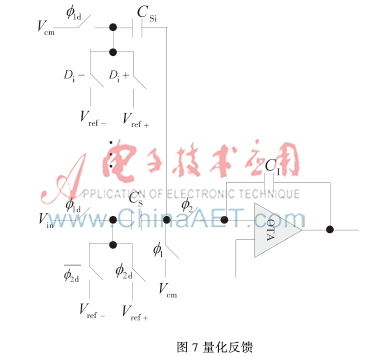

為了避免信號(hào)相關(guān)性,設(shè)計(jì)了一種新的量化反饋方式,,如圖7,,2.4 pF的采樣電容和8個(gè)0.3 pF的單位電容分別處理輸入信號(hào)和兩級(jí)量化器的反饋信號(hào)。

由于采用了多位量化,,為了抑制ADC的非線性,本文采用了DWA技術(shù)[8],。

4 仿真結(jié)果

本文所設(shè)計(jì)的調(diào)制器采用0.35μm CMOS工藝實(shí)現(xiàn),。標(biāo)準(zhǔn)采樣頻率為16 Mb/s,帶寬為500 kHz,。過采樣率為16 Mb/s,。采用Cadence進(jìn)行多工藝角驗(yàn)證,,并且在電源電壓在3 V~3.6 V,溫度在-40 ℃~75 ℃時(shí)調(diào)制器能正常工作,,信噪比和動(dòng)態(tài)范圍均能保持相近水平,。當(dāng)輸入正弦信號(hào)頻率為39 kHz,幅度為-3 dBFS時(shí)的輸出PSD如圖8所示,,結(jié)果表明,,設(shè)計(jì)的調(diào)制器能達(dá)到90.9 dB的SNDR(14.8 bit的有效精度)。

本文設(shè)計(jì)了一種基于零點(diǎn)優(yōu)化的低功耗ΣΔ調(diào)制器,,該結(jié)構(gòu)不需要傳統(tǒng)ΣΔ調(diào)制器中的數(shù)字抵消邏輯部分,,可以采用低增益的運(yùn)算放大器(OTA),減小了設(shè)計(jì)難度,。此外,,本文設(shè)計(jì)的調(diào)制器中積分器的輸出擺幅大大減小,積分器的非理想特性得到了抑制,。通過優(yōu)化零點(diǎn)位置,,增加了調(diào)制器的穩(wěn)定性和動(dòng)態(tài)范圍,信噪比和未進(jìn)行零點(diǎn)優(yōu)化的情況相比得到了很大地提高,。電路通過0.35 μm標(biāo)準(zhǔn)CMOS工藝仿真驗(yàn)證,,結(jié)果表明,調(diào)制器最高能達(dá)到15 bit的分辨率,,功耗為3.78 mW,。 結(jié)果表明,該結(jié)構(gòu)非常適合應(yīng)用于寬帶寬,、高精度,、低壓低功耗環(huán)境。

參考文獻(xiàn)

[1] Norsworthy S,, Schreier R,,Temes G. Delta-Sigma data converters:theory, design, and simulation[M]. NY: IEEE Press, 1996.

[2] Silva J, Moon U,, Steensgaard J. et al. Wideband lowdistortion delta-sigma ADC topology[J]. Electronics Letters, 2001,,37(12):737-738.

[3] Maghari N, Kwon S, Temes G,C. et al. Sturdy-級(jí)聯(lián)delta-sigma modulator[J]. Electron. Lett., 2006(42):1269-1270.

[4] Schreier R. An empirical study of high-order single-bit delta-sigma modulators[J]. IEEE Transactions on Circuits System II, 1993,,40(8):461-466.

[5] Sansen W M C. Aanlog design essentials[M]. Spring Press, 2006.

[6] Yin G M, Eynde F O,,Sansen W. A high-speed COMS comparator with 8-bit resolution[J]. IEEE Journal Solid-State Circuits, 1992(27):208-211.

[7] Sandner C, Clara M. A. A 6-bit 1.2-GS/s low-power flash-ADC in 0.13-μm Digital CMOS[J]. IEEE Journal Solid-State Circuits, 2005,40(7):1499-1505.

[8] Baird R T,,F(xiàn)iez T. Linearity enhancement of multibit A/D and D/A converters using data weigthed averaging[J]. IEEE Transaction on Circuits System. II, 1995,,42(12):753-762.