文獻標識碼: A

文章編號: 0258-7998(2014)12-0023-04

0 引言

ARM微處理器具有高性能、低功耗特點,市場占有率上ARM微處理器超過了75%,其產(chǎn)品從最初的單核ARM7發(fā)展到現(xiàn)在的多核Cortex R系列,相應的指令集從最原始的ARMv1到現(xiàn)在的ARMv8。每一種指令集都是在前一種指令集的基礎(chǔ)上增加若干指令用于提升性能,這樣微處理器保持了良好的向下兼容特性,用于低端芯片的工程可以完美地移植到高端的芯片上,具有良好的繼承性。其中ARMv4是第一次用于商業(yè)芯片的指令集,因而ARMv4是ARM微處理器指令發(fā)展源泉。對于ARM微處理的研究國內(nèi)目前主要集中在應用軟件上,通過ARM微處理器設(shè)計了一段什么樣的代碼,完成了什么樣的功能[1-2],而對于微處理器自身的研究較少。參考文獻[3]利用ARMv4指令集加入wishbone總線設(shè)計了一款新的32位微控制器,其微處理器結(jié)構(gòu)、流水線運行模式都與原來一樣,沒有什么變化。參考文獻[4]針對ARMv4指令集做了一個仿真平臺,主要用于監(jiān)控微處理器程序運行狀態(tài),而對微處理器本身并沒有什么改變。參考文獻[5]完成了一個指令模擬器,即在一臺計算器上模擬一個ARM微處理器,其結(jié)構(gòu)和指令完全都是按照芯片標準設(shè)計沒有一點變化。中國龍芯處理器以類MIPS指令集為基礎(chǔ),采用自己設(shè)計的架構(gòu)形成國產(chǎn)CPU。本文借鑒龍芯的發(fā)展模式,以ARMv4指令集為基礎(chǔ),采用哈佛結(jié)構(gòu),優(yōu)化內(nèi)存訪問指令,充分利用資源共享,減少芯片面積,改進后的嵌入式微處理器性能有所提升。

1 嵌入式微處理器模塊設(shè)計

1.1 結(jié)構(gòu)設(shè)計

當前微處理器有兩種存儲結(jié)構(gòu),馮·諾依曼結(jié)構(gòu)和哈佛結(jié)構(gòu),如圖1所示。馮·諾依曼結(jié)構(gòu)是一種將程序指令存儲器和數(shù)據(jù)存儲器合并在一起的存儲器結(jié)構(gòu)。程序指令存儲空間和數(shù)據(jù)存儲空間指向同一個存儲器的不同物理位置,共用一條數(shù)據(jù)總線,因而當讀取指令時,就必須暫停讀取數(shù)據(jù),兩者只能分別進行操作。這種結(jié)構(gòu)會制約后面流水線的并行操作。當流水線上一條指令訪問存儲器時,下一條指令必須等待上條指令訪問結(jié)束才可以訪問存儲器,期間流水線需要插入NOP指令等待,不能充分發(fā)揮流水線優(yōu)勢。哈佛結(jié)構(gòu)是一種將程序指令存儲和數(shù)據(jù)存儲分開的存儲器結(jié)構(gòu)。微處理器首先從程序指令存儲器中讀取程序指令內(nèi)容,解碼后得到數(shù)據(jù)地址,或直接從寄存器中直接獲得數(shù)據(jù)地址,再到相應的數(shù)據(jù)存儲器中讀取數(shù)據(jù),并進行下一步的操作。由于程序指令存儲和數(shù)據(jù)存儲分開,且擁有獨立的數(shù)據(jù)訪問總線。因而讀取程序和讀取數(shù)據(jù)可以同時進行,這樣可以更好發(fā)揮流水線優(yōu)勢,本文采用哈佛結(jié)構(gòu)。

1.2 單周期32位乘法器設(shè)計

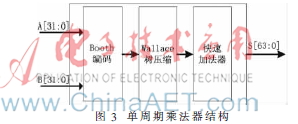

乘法器是重要而復雜的一個運算單元,乘法器電路信號傳播路徑長,電路延時比較大,針對乘法器很多人做了不同優(yōu)化。參考文獻[6]引入流水線乘法器,通過分部計算減少了單次乘法器的運算周期,適用于連續(xù)乘法器運算。但單次乘法器運算,使用時鐘周期反而隨流水線增長而增加,并不適用于微處理器方面。參考文獻[7]針對傳統(tǒng)Booth編碼方式進行了優(yōu)化,提出新的編碼方式。相比傳統(tǒng)Booth該方法減少了10%面積。同時優(yōu)化部分積產(chǎn)生電路如圖2所示,在部分積相加階段采用單獨4-2壓縮器,相比2個3-2壓縮器構(gòu)成的4-2壓縮器減少了門級電路。整個乘法器運算過程如圖3所示。

2 系統(tǒng)優(yōu)化

2.1 第二操作數(shù)獲取

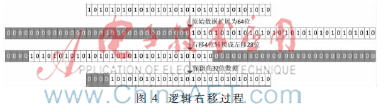

ARMv4指令集中數(shù)據(jù)的運算都是基于寄存器,通常一條指令包括1-3個寄存器,指明源寄存器和目的寄存器。指令中立即數(shù)一般會通過邏輯左移、邏輯右移、算術(shù)右移、循環(huán)右移、帶擴展的循環(huán)右移1位移位得到原立即數(shù)。這樣就需要5個32位的移位寄存器,這將增加芯片面積和功耗。通常控制邏輯單元消耗的邏輯資源少于運算單元消耗的資源。通過對數(shù)據(jù)的前期操作最后使用一個邏輯左移實現(xiàn)上面5種移位功能[8-9],大大減少邏輯資源。邏輯右移轉(zhuǎn)換成邏輯左移的實現(xiàn)過程如下:通過將被移數(shù)據(jù)補足為64位,然后將右移偏移量取負數(shù),通過左移負數(shù)個單位,高位得到的32位結(jié)果就是邏輯右移的結(jié)果,移位示意圖如圖4所示。

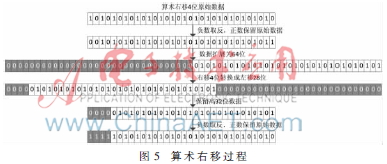

算術(shù)右移通過邏輯左移的實現(xiàn)過程如下:通過將被移數(shù)據(jù)補足為64位,然后判斷被移數(shù)據(jù)的正負性,若為負數(shù)則將數(shù)據(jù)取反,正數(shù)無需處理。然后將右移偏移量取負數(shù),通過左移負數(shù)個單位,保留高位得到的32位數(shù)據(jù)結(jié)果。根據(jù)被移數(shù)據(jù)的正負性,若為負數(shù)則將數(shù)據(jù)取反,正數(shù)保持不變,最后得到的結(jié)果就是算術(shù)右移的最終結(jié)果,移位示意圖如圖5所示。

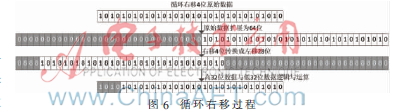

循環(huán)右移通過邏輯左移的實現(xiàn)過程如下:通過將被移數(shù)據(jù)補足為64位,然后將右移偏移量取負數(shù),通過左移負數(shù)個單位,將移位后的高32位數(shù)據(jù)與低32數(shù)據(jù)進行與運算得到結(jié)果即是循環(huán)右移的結(jié)果,移位示意圖如圖6所示。

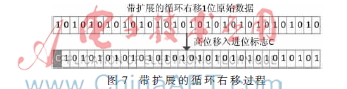

帶擴展的循環(huán)右移1位的實現(xiàn)過程如下:由于每次只能移位一個距離單位,只需要保留被移的數(shù)據(jù)的高31位,然后將進位標志C放在數(shù)據(jù)的最高位,即可實現(xiàn)帶擴展的循環(huán)右移1位功能。移位示意圖如圖7所示。

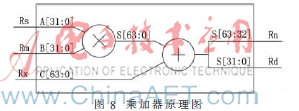

2.2 乘法器和乘加法器指令實現(xiàn)

ARMv4指令集中的乘法運算有32位乘法運算,32位乘加運算,無符號乘法運算,無符號乘加運算、有符號乘法運算、有符號乘加運算6種。通常不同功能乘法器需要不同設(shè)計。這樣6類乘法需要2個乘法器和2個加法器。如果將有符號數(shù)在運算前轉(zhuǎn)換成無符號數(shù),最后將運算結(jié)果根據(jù)之前的符號位轉(zhuǎn)換成有符號結(jié)果,這樣就將有符號乘法轉(zhuǎn)換為無符號乘法。對于簡單的乘法運算轉(zhuǎn)換為被加數(shù)為0的乘加運算,這樣所有的乘法和乘加運算都轉(zhuǎn)換為乘加運算。通過上面轉(zhuǎn)換后,6種乘法指令到最后都通過前置數(shù)據(jù)轉(zhuǎn)換共用一個乘加運算實現(xiàn),如圖8所示。

3 FPGA實現(xiàn)和Modelsim驗證

實驗所用FPGA芯片為Altera EP4CE30F23C7, EP4CE30器件總共有28 848個邏輯單元,器件中分布RAM有107 520 bit。由于芯片具有豐富的RAM,微處理器內(nèi)部RAM和ROM均采用FPGA內(nèi)部RAM實現(xiàn)。整個工程采用Verilog語言編寫,使用synplify pro 2011進行綜合,在Quartus 13.0下進行布局布線。利用Modelsim10.0a進行功能驗證和時序分析。設(shè)計ROM 32 KB,RAM 16 KB,時鐘20 MHz,其中內(nèi)部RAM、ROM通過使用FPGA內(nèi)部M4K存儲單元組成。C語言測試代碼使用?滋Vision V4.22編譯生成,由于FPGA無法直接初始化32位HEX文件,需要將HEX文件轉(zhuǎn)換為MIF格式。代碼轉(zhuǎn)化軟件通過VC ++ 6.0編寫。通過將轉(zhuǎn)換后將生成的MIF文件下載到ROM中進行測試驗證。

3.1 移位寄存器仿真

指令中包含的第二操作常數(shù)一般是通過8位常數(shù)循環(huán)右移得到。因而并不是所有常數(shù)都是合法常數(shù)。例如 mov r0,#0x1000;是合法指令,0x1000可以通過0x01循環(huán)右移20個單位得到。但是mov r0,#0x1001;就是非法指令,因為0x1001無法通過一個8位數(shù)據(jù)循環(huán)右移得到。上文中通過一個邏輯左移實現(xiàn)4種邏輯運算功能,為了驗證其正確性下面將通過4條指令分別測試邏輯左移、邏輯右移、算術(shù)右移、循環(huán)右移4種功能。測試代碼及理論運算結(jié)果如下:

movr0,#0x01//將r0初始化為1,結(jié)果為1

mov r0,r0,LSL#12//將r0邏輯左移12位,結(jié)果為0x1000

mov r0,r0,LSR#4//將r0邏輯右移4位,結(jié)果為0x100

mov r0,r0,ASR#8//將r0算術(shù)右移8位,結(jié)果為0x01

mov r0,r0,ROR#8//將r0循環(huán)右移8位,其結(jié)果位0x1000000

Modelsim仿真如圖9所示。

從Modelsim仿真結(jié)果看出,設(shè)計的單個邏輯左移移位寄存器很好的完成了上述4種功能。

3.2 乘法器和乘加法器仿真

經(jīng)過優(yōu)化后的乘法指令和乘加指令都通過同一個乘加器實現(xiàn)。為了驗證其正確性,分別采用6種乘法指令分析其正確性。測試思路是通過編寫指定的代碼,進行理論計算,然后對比微處理器運行結(jié)果。測試代碼及理論運行結(jié)果如下:

movr0,#0x120000;orr r0,#0x3400;orr r0,#0x56

movr1,#0x80000000;orr r1,#0x7800;orr r1,#0x9a

movr5,#0x01

上面6段代碼主要是初始化r0、r1、r5值,運行后r0為0x123456,r1為0x8000789a, r5為0x01。

mul r4,r0,r1:運算結(jié)果為0x91a33937bcbbc,由于只取32位結(jié)果,r4結(jié)果為0x937bcbbc。

mla r4,r0,r1,r5:運算結(jié)果為0x91a33937bcbbd,由于只取32位結(jié)果,r4結(jié)果為0x937bcbbd。

umull r4,r5,r0,r1:無符號乘法結(jié)果為0x91a33937bcbbc,r5結(jié)果為0x91a33,r4結(jié)果為0x 937bcbbc。

umlal r4,r5,r0,r1:無符號乘發(fā)結(jié)果為0x91a33937bcbbc,乘加r5結(jié)果為0x123467,r4結(jié)果為0x 26f79778。

smull r4,r5,r0,r1:r1最高位為1有符號運算時先轉(zhuǎn)換為無符號數(shù)0x7fff8766,然后計算得到無符號結(jié)果0x91a226c843444,轉(zhuǎn)換成有符號后r5結(jié)果為0xfff6e5dd,r4結(jié)果為0x 937bcbbc。

smlal r4,r5,r0,r1:r1最高位為1有符號運算時先轉(zhuǎn)換為無符號數(shù)0x7fff8766,然后計算得到無符號結(jié)果0x91a226c843444,轉(zhuǎn)換成有符號結(jié)果為0xfff6e5dd937bcbbc,乘加后r5結(jié)果為0xffedcbbb,r4結(jié)果為0x26f79778。

Modelsim仿真如圖10所示。從仿真結(jié)果看出,設(shè)計的單個乘加器正確的完成了上述6類指令的功能。

3.3 Dhrystone性能測試

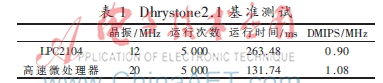

Dhrystone的計量單位為每秒計算多少次Dhrystone,它是一個相對值。程序用C語言編寫,能運行在大多數(shù)微處理器上,是測試處理器運算能力的最常見基準程序之一。基準程序使用?滋Vision V4.22軟件下ARM自帶的Dhrystone2.1基準測試程序,去掉全部優(yōu)化后,將編譯好的文件下載到本文設(shè)計的微處理器。選用NXP公司的ARM LPC2102微處理器芯片作為對比。LPC2102在ARMv4指令集基礎(chǔ)上增加了Thumb指令集,測試時禁用交叉編譯只生成32位的ARM指令。結(jié)果如表1所示。

從表1中可以看出,改進后的微處理器,相比當前市面同種類微處理器性能有近20%提升。

4 結(jié)論

當前高性能、高效率的微處理器基本采用哈佛結(jié)構(gòu)。本文以ARMv4指令集為基礎(chǔ),將傳統(tǒng)馮·諾依曼結(jié)構(gòu)更改為哈佛結(jié)構(gòu),擁有獨立指令總線和數(shù)據(jù)總線,其優(yōu)點是在流水線階段可以同時進行訪問ROM和RAM,避免了單總線引起的資源競爭。采用單周期乘法器,提高微處理器的運算速度。在設(shè)計乘法器時,利用資源共享,最終一個乘加器實現(xiàn)了6條指令功能。采用單一邏輯左移移位寄存器實現(xiàn)多種模式移位功能。實驗結(jié)果表明,本文設(shè)計的微處理器能正確運行ARMv4指令集,同等條件下比當前市面同種類芯片性能有20%提高。大多數(shù)應用程序在不修改就可以提高20%性能。

參考文獻

[1] 董海濤,莊淑君,陳冰,等.基于ARM+DSP+FPGA的可重構(gòu)CNC系統(tǒng)[J].華中科技大學學報(自然科學版),2012,40(8):82-87.

[2] 竺樂慶,張三元,幸銳.基于ARM與WinCE的掌紋鑒別系統(tǒng)[J].儀器儀表學報,2009,30(12):2624-2628.

[3] 孫永琦.基于ARMv4指令集的32位RISC微控制器的設(shè)計與實現(xiàn)[D].浙江:浙江理工大學,2012.

[4] 徐懷亮,劉曉升,王宜懷,等.一種ARM指令集仿真器的實現(xiàn)與優(yōu)化[J].蘇州大學學報(工科版),2009,29(2):28-31.

[5] 賈少波.基于X86平臺的ARM指令集模擬器的設(shè)計[J].電子設(shè)計工程,2013,21(12):164-169.

[6] 周怡,李樹國.一種改進的基4-Booth編碼流水線大數(shù)乘法器設(shè)計[J].微電子學與計算機,2014,1(6):60-63.

[7] 翟召岳,韓志剛.基于Booth算法的32位流水線型乘法器設(shè)計[J].微電子學與計算機,2014,31(3):146-149.

[8] 杜慧敏,王明明,沈子杰.32位桶式移位寄存器FPGA實現(xiàn)[J].西安郵電學院學報,2008,13(1):99-102.

[9] 陳永強,雷雨.可變長移位寄存器在高速數(shù)據(jù)采集中的應用與FPGA實現(xiàn)[J].西華大學學報(自然科學版),2013,32(4):61-63.

基金項目:廣東省工程技術(shù)研究中心項目(2012gczxA003)