摘 要: 結(jié)合PCI-Express的傳輸特性,分析了PEX8311的DMA傳輸模式與時(shí)序邏輯,通過有限狀態(tài)機(jī)的設(shè)計(jì),實(shí)現(xiàn)PEX8311的DMA傳輸。與其他設(shè)計(jì)相比,利用有限狀態(tài)機(jī)理論設(shè)計(jì)控制邏輯具有直觀、簡(jiǎn)單、設(shè)計(jì)流程短等優(yōu)點(diǎn),并對(duì)狀態(tài)機(jī)進(jìn)行了Verilog優(yōu)化設(shè)計(jì),使?fàn)顟B(tài)機(jī)更加穩(wěn)定。

關(guān)鍵詞: 橋接芯片PEX8311;PCI-Express接口;DMA傳輸;有限狀態(tài)機(jī)

0 引言

PCI-Express是最新的總線和接口標(biāo)準(zhǔn),它代表著下一代I/O接口標(biāo)準(zhǔn)。它原名為3GIO,是由英特爾在2001年提出的,交由PCI-SIG(PCI特殊興趣組織)認(rèn)證發(fā)布后才改名為PCI-Express,簡(jiǎn)稱PCI-E。PCI-E屬于高速串行點(diǎn)對(duì)點(diǎn)雙通道高帶寬傳輸,所連接的設(shè)備分配獨(dú)享通道帶寬,不共享總線帶寬,主要支持主動(dòng)電源管理、錯(cuò)誤報(bào)告、端對(duì)端的可靠性傳輸、熱插拔以及服務(wù)質(zhì)量(QoS)等功能。這個(gè)新標(biāo)準(zhǔn)將全面取代現(xiàn)行的PCI和AGP,最終實(shí)現(xiàn)總線標(biāo)準(zhǔn)的統(tǒng)一。

PCI-Express的主要優(yōu)勢(shì)就是數(shù)據(jù)傳輸速率高,目前最高的16X2.0版本可達(dá)到10 Gb/s,而且還有相當(dāng)大的發(fā)展?jié)摿ΑCI-Express也有多種規(guī)格,從PCI-Express 1X到PCI-Express 16X,能滿足將來一定時(shí)間內(nèi)出現(xiàn)的低速設(shè)備和高速設(shè)備的需求。PCI-Express最新的接口是PCIE 3.0接口,其比特率為8 Gb/s,約為上一代產(chǎn)品帶寬的兩倍,并且包含發(fā)射器和接收器均衡、PLL改善以及時(shí)鐘數(shù)據(jù)恢復(fù)等一系列重要的新功能,用以改善數(shù)據(jù)傳輸和數(shù)據(jù)保護(hù)的性能[1]。

1 PEX8311的介紹

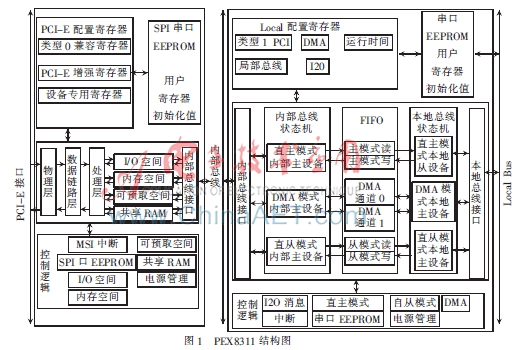

PEX8311是PLX Technology公司推出的一款專用于將DSP、FPGA等處理器總線接口升級(jí)為PCI-E的橋接器件。利用PEX8311靈活的局部總線可以方便地連接多種存儲(chǔ)器、緩存器及FPGA、DSP等邏輯芯片,使復(fù)雜的PCIE接口設(shè)計(jì)簡(jiǎn)單化。PEX8311兼容PCI-Express 1.0標(biāo)準(zhǔn),其本地總線和寄存器與PCI9056兼容,能夠提供完整的本地總線到PCI-E的接口,包括地址轉(zhuǎn)換、包生成與解碼、信號(hào)中斷支持及并/串轉(zhuǎn)換等[2]。圖1為PEX8311結(jié)構(gòu)圖。

PEX8311由兩組橋接模塊組成:PCIE-PCI和PCI-Local Bus,相應(yīng)地配有兩組寄存器PECS和LCS。PEX8311支持外部EEPROM對(duì)寄存器分別進(jìn)行配置,也可以通過PC或本地處理器進(jìn)行配置。

PEX8311芯片特點(diǎn):

(1)集成了單通道、全雙工2.5 Gb/s傳輸?shù)腜CI Express端口;

(2)本地總線配置支持8位、16位和32位的總線結(jié)構(gòu);

(3)支持三種操作模式,使用靈活;

(4)高性能DMA數(shù)據(jù)傳輸支持塊模式、集散模式、循環(huán)隊(duì)列管理和命令模式;

(5)支持端點(diǎn)(EP)和根組件(RC)模式;

(6)芯片低功耗設(shè)計(jì);

(7)芯片小型封裝,適合緊湊的電路板設(shè)計(jì);

(8)3.3 V的I/O并且兼容5 V系統(tǒng);

(9)串行EEPROM用來可選擇的導(dǎo)入配置,支持SPI接口和Microwire接口;

(10)有8 KB的統(tǒng)配共享RAM。

PEX8311可配置為端點(diǎn)模式(Endpoint mode)和根組件模式(Root complex mode)。端點(diǎn)模式多用于設(shè)備端的橋接模式,而根組件端則用于PC端的橋接模式。最常用的模式為端點(diǎn)模式[3]。

在端點(diǎn)模式下有三種操作類型:C模式、J模式和M模式。C模式為非復(fù)用地址/數(shù)據(jù)總線模式,是最為常用的模式,支持多數(shù)的MCU、ASIC和FPGA。J模式為復(fù)用地址/數(shù)據(jù)總線模式,即部分地址/數(shù)據(jù)總線復(fù)用,支持部分MCU和FPGA。M模式為專用模式。

在C模式下又有三種數(shù)據(jù)傳輸模式:直主模式(Direct Master mode)、直從模式(Direct Slave mode)和DMA模式。三種數(shù)據(jù)傳輸模式中,直從模式的優(yōu)先級(jí)最高,直主模式次之,DMA模式最低。

(1)直主模式:本地處理器掌握本地總線控制權(quán)。寄存器配置和PEX8311芯片控制都由本地處理器完成。

(2)直從模式:PEX8311掌握本地總線控制權(quán),寄存器配置和PEX8311芯片控制由PC端完成。

(3)DMA模式:PEX8311掌握本地總線和PCI-E端總線的控制權(quán),此模式下的數(shù)據(jù)傳輸無需本地處理器或PC處理器干預(yù)。

2 DMA傳輸模式

DMA模式中,PEX8311提供兩個(gè)完全獨(dú)立的雙向通道DMA Channel 0和DMA Channel 1,每個(gè)通道都配有256 B深度的獨(dú)立異步FIFO;支持塊模式、集散模式、循環(huán)隊(duì)列管理和命令模式[2]。DMA塊模式無需PC或本地控制器干預(yù),傳輸效率高,所以可以大大降低控制器的工作量并且提高數(shù)據(jù)傳輸效率,為了達(dá)到最大的數(shù)據(jù)傳輸效率,選擇DMA塊模式持續(xù)傳輸方式進(jìn)行數(shù)據(jù)傳輸。

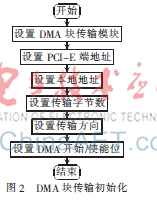

PCI-E設(shè)備或本地處理器設(shè)置DMA的PCI以及本地的開始地址、傳輸字節(jié)數(shù)和傳輸方向后,PCI-E設(shè)備或本地處理器設(shè)置DMA通道開始和使能位(LCS_DMACSR0/1[1:0]=11b)來初始化一個(gè)傳輸。PEX8311訪問內(nèi)部PCI-E地址空間在PCI-E接口和本地總線上產(chǎn)生一個(gè)TLP,然后開始傳輸數(shù)據(jù)。傳輸完成后,PEX8311設(shè)置相應(yīng)的DMA通道的通道完成位(LCS_DMACSR0/1[4]=1),聲明一個(gè)終中斷(LCS_INTCSR[16 and/or 8]和/或LCS_DMAMODE0/1[17 and/or 10]到本地處理器或PCI-E接口(可編程)。相應(yīng)DMA通道的通道完成位可以采用輪詢的方式取代中斷方式來指示DMA傳輸狀態(tài)[4]。圖2為DMA塊傳輸?shù)某跏蓟^程。

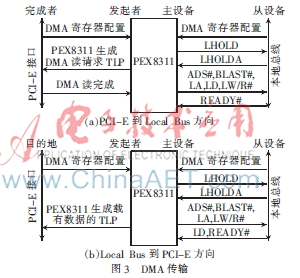

在DMA傳輸中,PEX8311是PCI-E接口的傳輸發(fā)起者(產(chǎn)生TLP)和本地總線的主機(jī),對(duì)于同一時(shí)間的訪問,直從模式或直主模式比DMA模式優(yōu)先級(jí)更高,如圖3所示。

3 狀態(tài)機(jī)設(shè)計(jì)

狀態(tài)機(jī)的基本要素有三個(gè):輸入、輸出和狀態(tài)。根據(jù)狀態(tài)機(jī)的輸出是否與輸入條件有關(guān),可將狀態(tài)機(jī)分為兩大類:摩爾型(Moor)狀態(tài)機(jī)和米勒型(Mealy)狀態(tài)機(jī)[5]。

根據(jù)狀態(tài)機(jī)的設(shè)計(jì)步驟,首先確定狀態(tài)機(jī)的輸入輸出信號(hào),即DMA傳輸?shù)目刂菩盘?hào)。

3.1 狀態(tài)機(jī)輸入輸出信號(hào)

LCLK:輸入,PEX8311本地總線系統(tǒng)時(shí)間。

LHOLD:輸出,PEX8311本地總線請(qǐng)求信號(hào),上電為低電平,當(dāng)PEX8311需要控制本地總線時(shí)拉高,等到LHOLDA信號(hào)響應(yīng)后,PEX8311獲得本地總線控制權(quán)。

LHOLDA:輸入,PEX8311本地總線請(qǐng)求應(yīng)答信號(hào),上電為低電平,在當(dāng)前總線擁有者響應(yīng)LHOLD信號(hào)后,將LHOLDA拉高。PEX8311未發(fā)出LHOLD信號(hào)時(shí),不能把本地總線的使用權(quán)交給PEX8311。

LA[31:0]:雙向,本地地址總線。提供總線物理地址的高30位。

LD[31:0]:雙向,本地?cái)?shù)據(jù)總線,當(dāng)PEX8311配置為L(zhǎng)ocal總線主控時(shí),可以傳輸8 bit、16 bit或32 bit數(shù)據(jù)。

LBE[3:0]#:雙向,本地字節(jié)使能信號(hào),利用此信號(hào)可以實(shí)現(xiàn)8 bit、16 bit、32 bit數(shù)據(jù)傳輸,同時(shí)由該管腳提供輔助增加的地址信號(hào)。如果是32 bit數(shù)據(jù)線,則LBE[3:0]#=0000。

ADS#:三態(tài)雙向,內(nèi)有上拉電阻,地址選通信號(hào),表明地址有效,開始新的總線訪問,ADS#在每次傳輸?shù)牡谝粋€(gè)時(shí)鐘周期插入。

BLAST#:雙向,作為輸入時(shí),本地總線主機(jī)有效該信號(hào)來指示總線的最后一次數(shù)據(jù)傳輸;作為輸出時(shí),PEX8311有效該信號(hào)來指示總線上的最后一次數(shù)據(jù)傳輸。

READY#:雙向,I/O口就緒信號(hào)。在直從或DMA傳輸下為輸入信號(hào),表明可讀的數(shù)據(jù)已經(jīng)在總線上有效或待寫數(shù)據(jù)已經(jīng)在下個(gè)時(shí)鐘上升沿到達(dá)前準(zhǔn)備好;直主模式下為輸出信號(hào)。

LW/R#:雙向,讀寫控制位,對(duì)于DMA塊傳輸,LW/R#=0為讀信號(hào),本地總線到PCI-E方向;LW/R#=1為寫信號(hào),PCI-E到本地總線方向。

3.2 狀態(tài)機(jī)狀態(tài)轉(zhuǎn)換

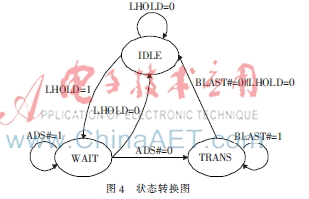

DMA傳輸模式分為單周期模式和突發(fā)模式。本設(shè)計(jì)中采用單周期模式。單周期模式是默認(rèn)的數(shù)據(jù)傳輸模式。在該模式下,PEX8311每個(gè)數(shù)據(jù)周期都聲明一個(gè)ADS#。單周期模式的起始地址可以是任意的。

Local Bus FSM設(shè)計(jì)分為三個(gè)狀態(tài):IDLE、WAIT和TRANS。其狀態(tài)轉(zhuǎn)換如圖4所示。

IDLE:為空閑狀態(tài),當(dāng)FPGA收到lreset復(fù)位信號(hào)后,進(jìn)入IDLE狀態(tài)。

WAIT:為等待狀態(tài),當(dāng)握手信號(hào)LHOLD和LHOLDA完成后進(jìn)入WAIT狀態(tài),進(jìn)行地址空間判斷,等待地址選通信號(hào)有效。

TRANS:為傳輸狀態(tài),當(dāng)?shù)刂愤x通信號(hào)有效后進(jìn)入傳輸狀態(tài),進(jìn)行數(shù)據(jù)傳輸,直到BLAST#信號(hào)有效后,進(jìn)入IDLE狀態(tài)。

FPGA作為L(zhǎng)ocal Bus的控制器,主要負(fù)責(zé)控制Local Processor與PC端的數(shù)據(jù)傳輸。上電初始化完成后,PEX8311向FPGA以及其他后端邏輯電路發(fā)送復(fù)位信號(hào)。當(dāng)PC端做好接收數(shù)據(jù)的準(zhǔn)備后,PEX8311向FPGA發(fā)送Local Bus的總線請(qǐng)求信號(hào)LHOLD,F(xiàn)PGA向PEX8311發(fā)送請(qǐng)求應(yīng)答信號(hào)LHOLDA,PEX8311獲得總線控制權(quán),并進(jìn)行地址空間判斷,向FPGA發(fā)送地址選通信號(hào),表明地址有效,進(jìn)行新的總線訪問。在FPGA端,將經(jīng)過處理的數(shù)據(jù)存入RAM中,當(dāng)?shù)刂愤x通信號(hào)有效后,置位ram_rd信號(hào),從RAM中將數(shù)據(jù)讀出,并且使READY#信號(hào)有效,開始進(jìn)行數(shù)據(jù)傳輸,當(dāng)FPGA收到有效的BLAST#信號(hào)后,在下一周期使READY#信號(hào)無效,進(jìn)入IDLE狀態(tài),完成一次DMA傳輸。

3.3 Local Bus狀態(tài)機(jī)Verilog設(shè)計(jì)

always@(state or ads_n or lhold or blast_n)

begin

case(state)

IDLE:

begin

if(lhold)

next_state<=WAIT;

else

next_state<=IDLE;

end

WAIT:

begin

if(~lhold)

next_state<=IDLE;

else if(!ads_n)

next_state<=TRANS;

else

next_state<=WAIT;

end

TRANS:

begin

if(~lhold|(~ram_rd_delay[2]&ram_rd_delay[1]))

next_state<=IDLE;

else

next_state<=TRANS;

end

default:

begin

next_state<=IDLE;

end

endcase

end

3.4 仿真

圖5為DMA傳輸讀操作仿真圖。

4 結(jié)論

本文設(shè)計(jì)的Local Bus控制器應(yīng)用在PEX8311與FPGA的接口中以實(shí)現(xiàn)DMA傳輸,穩(wěn)定性強(qiáng),使用靈活,可隨時(shí)改變?yōu)槠渌ぷ髂J健?蓱?yīng)用于視頻采集卡、數(shù)據(jù)采集卡。經(jīng)過實(shí)踐證明,基于FPGA設(shè)計(jì)的控制器靈活性強(qiáng)、可編程能力強(qiáng),能迅速縮短產(chǎn)品研發(fā)上市周期,滿足客戶需求。

在Verilog的設(shè)計(jì)中對(duì)代碼的優(yōu)化使用了三段式描述方法[6]。與一段式描述方法相比較,三段式FSM描述方法對(duì)FSM寄存器輸出的描述只需判斷下一狀態(tài),然后直接將下一狀態(tài)的輸出用寄存器輸出即可,根本不用考慮狀態(tài)轉(zhuǎn)移條件(米勒狀態(tài)機(jī))。與兩段式描述相比,三段式雖然代碼結(jié)構(gòu)復(fù)雜了一些,但是換來的優(yōu)勢(shì)是使FSM做到了同步寄存器輸出,消除了組合邏輯輸出的不穩(wěn)定與毛刺的隱患,而且更利于時(shí)序路徑分組,一般來說在FPGA/CPLD等可編程邏輯器件上的綜合與布局布線效果更佳。

參考文獻(xiàn)

[1] 王齊.PCI Express體系結(jié)構(gòu)導(dǎo)讀[M].北京:機(jī)械工業(yè)出版社,2010.

[2] PLX.PEX8311AA Data Book[OL].[2014-04-20].http://www.plxtech.com, 2009.

[3] PLX. Local Bus Primer: introduction to Local Bus signals and protocols[OL]. [2014-04-20].http://www.plxtech.com, 2001.

[4] 王誠,蔡海寧,吳繼華.Altera FPGA/CPLD設(shè)計(jì)[M].北京:人民郵電出版社,2011.

[5] 夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程[M].北京:北京航空航天大學(xué)出版社,2003.

[6] 黃小紅,李峰,倪衛(wèi)芳.PEX8311芯片數(shù)據(jù)傳輸研究[J].電子工程師,2007,33(10):65.