摘 要: 根據(jù)實(shí)際項(xiàng)目需求設(shè)計(jì)了一種實(shí)時(shí)陣列信號(hào)處理系統(tǒng),采用多路高速光纖作為數(shù)據(jù)輸入、輸出接口;4片處理器組成互聯(lián)的拓?fù)浣Y(jié)構(gòu),任何兩片處理器之間都可以互相傳送數(shù)據(jù),多片處理器可同時(shí)對(duì)數(shù)據(jù)進(jìn)行高速處理;系統(tǒng)配備了大容量存儲(chǔ)器,可滿足大量數(shù)據(jù)的存儲(chǔ)要求;采用兩片現(xiàn)場(chǎng)可編程門(mén)陣列器件對(duì)系統(tǒng)接口、時(shí)序進(jìn)行控制;為每片處理器分配了處理任務(wù),并對(duì)信號(hào)處理算法運(yùn)行時(shí)間及數(shù)據(jù)傳輸時(shí)間進(jìn)行評(píng)估。該系統(tǒng)已在實(shí)際項(xiàng)目中運(yùn)行,充分滿足項(xiàng)目要求,運(yùn)行穩(wěn)定,驗(yàn)證了本系統(tǒng)設(shè)計(jì)的可行性。

關(guān)鍵詞: 實(shí)時(shí)系統(tǒng)設(shè)計(jì);陣列信號(hào)處理;算法運(yùn)行時(shí)間評(píng)估;處理器

0引言

在現(xiàn)代雷達(dá)、測(cè)向等系統(tǒng)中需要對(duì)陣列信號(hào)進(jìn)行實(shí)時(shí)處理。陣列信號(hào)通道數(shù)多,數(shù)據(jù)量大,信號(hào)處理實(shí)時(shí)性要求高[1-2]。目前,F(xiàn)PGA和DSP成為這類(lèi)系統(tǒng)中信號(hào)處理的主要器件。參考文獻(xiàn)[3]~[5]均采用FPGA來(lái)實(shí)現(xiàn)數(shù)字信號(hào)處理算法。FPGA對(duì)方法簡(jiǎn)單和規(guī)則的運(yùn)算來(lái)說(shuō)效率很高,所設(shè)計(jì)系統(tǒng)具有集成度高、體積小和快速實(shí)時(shí)處理等優(yōu)點(diǎn),但其靈活性差、開(kāi)發(fā)成本高、系統(tǒng)升級(jí)困難,特別是在浮點(diǎn)運(yùn)算處理時(shí)開(kāi)銷(xiāo)呈幾何級(jí)增長(zhǎng)。DSP技術(shù)具有靈活性強(qiáng)、開(kāi)發(fā)周期短以及系統(tǒng)升級(jí)維護(hù)方便等特點(diǎn)[1,6],比較適合算法復(fù)雜的數(shù)字信號(hào)處理。采用FPGA加DSP的方法進(jìn)行系統(tǒng)設(shè)計(jì),兼顧二者的優(yōu)點(diǎn)[7],更適合雷達(dá)、測(cè)向等大型系統(tǒng),使系統(tǒng)設(shè)計(jì)更加靈活,降低了開(kāi)發(fā)難度和成本,易于系統(tǒng)升級(jí)與維護(hù)。參考文獻(xiàn)[1]、[6]、[8]、[9]均采用了這種方式進(jìn)行系統(tǒng)設(shè)計(jì)。

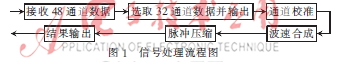

在某實(shí)際項(xiàng)目中,要求設(shè)計(jì)一套實(shí)時(shí)陣列信號(hào)處理系統(tǒng),陣列信號(hào)通道數(shù)為48,每通道數(shù)據(jù)長(zhǎng)度為2 400,根據(jù)高、低頻段選取不同的32通道數(shù)據(jù)進(jìn)行處理,最小處理周期為50 ms,并將選取的32通道數(shù)據(jù)和處理結(jié)果輸出。信號(hào)處理流程如圖1所示。

針對(duì)項(xiàng)目要求設(shè)計(jì)了一套吞吐速率高、處理速度快、存儲(chǔ)容量大的實(shí)時(shí)陣列信號(hào)處理系統(tǒng),并在實(shí)際工程中進(jìn)行了應(yīng)用。系統(tǒng)采用FPGA加DSP的設(shè)計(jì)方式,DSP用于對(duì)數(shù)據(jù)的實(shí)時(shí)處理,F(xiàn)PGA用于對(duì)時(shí)序和接口的控制。

1 系統(tǒng)設(shè)計(jì)

1.1 處理器設(shè)計(jì)

TS201是一款高性能數(shù)字信號(hào)處理器,具有運(yùn)算速度快、接口豐富、擴(kuò)展能力強(qiáng)等特點(diǎn),特別適合雷達(dá)等處理數(shù)據(jù)量大、實(shí)時(shí)性要求高的信號(hào)處理系統(tǒng)[10]。

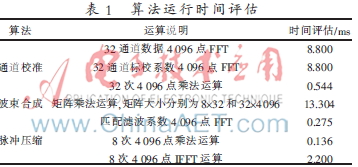

根據(jù)TS201處理器的處理速度,對(duì)系統(tǒng)中所用到的通道校準(zhǔn)、波束合成和脈沖壓縮信號(hào)處理算法運(yùn)行時(shí)間進(jìn)行評(píng)估,如表1所示。

表1中所有時(shí)間合計(jì)為34.059 ms。綜合考慮,本系統(tǒng)需要4片TS201處理器,1片用于接收48通道基帶數(shù)據(jù),1片用于脈壓運(yùn)算及處理結(jié)果輸出,另外兩片處理器主要用于通道校準(zhǔn)、波束合成運(yùn)算及32通道基帶數(shù)據(jù)輸出。

1.2 控制設(shè)計(jì)

選用兩片F(xiàn)PGA(型號(hào)為XC5VLX50T)用于系統(tǒng)接口和時(shí)序控制。

XC5VLX50T是賽靈思公司Virtex-5系列中的一款產(chǎn)品。該型號(hào)FPGA具有480個(gè)用戶I/O,可以被配置成各種電平標(biāo)準(zhǔn);最大可提供2 160 kbit塊式RAM和480 kbit分布式RAM;單片集成12個(gè)Rocket IO模塊,完全滿足本系統(tǒng)的設(shè)計(jì)要求。

1.3 接口設(shè)計(jì)

主要接口包括數(shù)據(jù)的輸入和輸出,根據(jù)項(xiàng)目要求均采用光纖進(jìn)行傳輸。48通道基帶數(shù)據(jù)分別來(lái)自3個(gè)不同的數(shù)字接收機(jī)柜(分別用A、B、C表示),傳送數(shù)據(jù)的通道數(shù)分別為8、24和16,需要3個(gè)接收光口。基帶數(shù)據(jù)轉(zhuǎn)發(fā)光口要求至少為3個(gè),以便提供多臺(tái)設(shè)備使用。處理結(jié)果輸出光口要求大于2個(gè)。這里為每個(gè)處理器配備3個(gè)光纖收、發(fā)接口。

光口收發(fā)器采用Rocket IO模塊。Rocket IO是一種高速串行收發(fā)器,采用兩對(duì)差分信號(hào)進(jìn)行數(shù)據(jù)的發(fā)送和接收,8 B/10 B編碼可以避免數(shù)據(jù)流中出現(xiàn)連0或者連1串,通信速率可達(dá)800 Mb/s~3.125 Gb/s。考慮到穩(wěn)定性問(wèn)題,本系統(tǒng)中光口的速率設(shè)計(jì)為2.5 Gb/s。由于采用了8 B/10 B編碼,因此實(shí)際有效數(shù)據(jù)傳輸速率為2.0 Gb/s。

發(fā)送數(shù)據(jù)時(shí),處理器將數(shù)據(jù)通過(guò)外部接口寫(xiě)入到FPGA的FIFO中,然后數(shù)據(jù)再由FIFO通過(guò)Rocket IO模塊發(fā)送出去。接收數(shù)據(jù)時(shí),數(shù)據(jù)首先進(jìn)入Rocket IO模塊,經(jīng)過(guò)轉(zhuǎn)換之后寫(xiě)入到FPGA的接收FIFO中,處理器通過(guò)外部總線從接收FIFO中讀取數(shù)據(jù)到內(nèi)存進(jìn)行處理。

1.4 系統(tǒng)設(shè)計(jì)

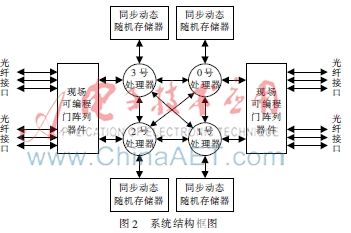

系統(tǒng)結(jié)構(gòu)如圖2所示。

每個(gè)處理器都通過(guò)Link口分別與其他3個(gè)處理器互聯(lián),數(shù)據(jù)可以在任何兩個(gè)處理器之間進(jìn)行傳輸。剩余的一個(gè)Link口被引出,可通過(guò)外接線纜的方式與其他系統(tǒng)TS201處理器的Link口相連,便于系統(tǒng)升級(jí)及其他項(xiàng)目應(yīng)用。

由于陣列信號(hào)數(shù)據(jù)量較大,處理器內(nèi)存很難滿足存儲(chǔ)要求。為此,在本系統(tǒng)中每片處理器都搭載了總?cè)萘繛?12 MB的SDRAM。

系統(tǒng)時(shí)鐘頻率為50 MHz,處理器內(nèi)核時(shí)鐘頻率為600 MHz。處理器通過(guò)外部總線訪問(wèn)SDRAM及光口FIFO的速率為400 MB/s。

2 系統(tǒng)分析

2.1 任務(wù)分配

與0號(hào)處理器連接的3個(gè)光口分別與3臺(tái)數(shù)字接收機(jī)柜相連,用于接收48通道基帶數(shù)據(jù),并按照項(xiàng)目要求分高、低頻段選出不同的32通道數(shù)據(jù),通過(guò)兩個(gè)Link口分別傳送到2號(hào)和3號(hào)處理器。

2號(hào)處理器收到32通道數(shù)據(jù)后,將該數(shù)據(jù)通過(guò)3個(gè)光纖接口輸出;然后開(kāi)始對(duì)前16通道數(shù)據(jù)進(jìn)行信號(hào)處理,包括通道校準(zhǔn)和子陣波束合成;最后將波束合成結(jié)果通過(guò)Link口發(fā)送到1號(hào)處理器。

3號(hào)處理器完成的任務(wù)與2號(hào)處理器相同,只是處理的數(shù)據(jù)為后16通道。

1號(hào)處理器完成對(duì)2號(hào)和3號(hào)處理器波束數(shù)據(jù)的接收,并進(jìn)行全陣波束合成和脈沖壓縮處理,最后將處理結(jié)果通過(guò)該處理器的3個(gè)光纖接口輸出。

2.2 系統(tǒng)評(píng)估

為實(shí)現(xiàn)傳輸?shù)姆€(wěn)定性及處理器接收速率與光纖傳輸速率的最佳匹配,控制每個(gè)接收機(jī)柜發(fā)送數(shù)據(jù)的速率為160 MB/s,并采用圖3所示的時(shí)序進(jìn)行發(fā)送,能充分利用系統(tǒng)傳輸帶寬。

從圖3可以看出,同一時(shí)刻最多只有兩個(gè)光纖在傳輸數(shù)據(jù)。數(shù)字接收機(jī)柜A的8通道數(shù)據(jù)發(fā)送完成后空閑1 ms,然后數(shù)字接收機(jī)柜C開(kāi)始發(fā)送數(shù)據(jù)。0號(hào)處理器接收完3個(gè)機(jī)柜發(fā)送的48通道數(shù)據(jù)所用時(shí)間相當(dāng)于機(jī)柜A的發(fā)送時(shí)間、機(jī)柜C的發(fā)送時(shí)間及空閑時(shí)間的和,約為3.88 ms。32通道數(shù)據(jù)以DMA的方式同時(shí)向2號(hào)和3號(hào)處理器傳送數(shù)據(jù),需要時(shí)間為1.536 ms。因此,0號(hào)處理器完成數(shù)據(jù)的接收和發(fā)送共需要花費(fèi)時(shí)間約5.416 ms。

2號(hào)處理器首先接收32通道基帶數(shù)據(jù),并通過(guò)光纖接口發(fā)送,然后對(duì)前16通道數(shù)據(jù)進(jìn)行通道校準(zhǔn)和波束合成,最后將處理結(jié)果通過(guò)Link口發(fā)送到1號(hào)處理器,其運(yùn)算時(shí)間評(píng)估如表2所示。32通道基帶數(shù)據(jù)要同時(shí)通過(guò)3個(gè)光口發(fā)送,因此處理器訪問(wèn)一個(gè)光口的平均速率變?yōu)?33 MB/s。

2號(hào)處理器總的運(yùn)行時(shí)間為22.535 ms。TS201處理器內(nèi)存由6個(gè)存儲(chǔ)塊組成,4條內(nèi)部總線分別與6個(gè)內(nèi)存塊相連,當(dāng)參與運(yùn)算的數(shù)據(jù)分別位于不同的內(nèi)存塊時(shí)可提高運(yùn)算效率。

3號(hào)處理器算法運(yùn)行時(shí)間評(píng)估與2號(hào)處理器相同。

1號(hào)處理器通過(guò)Link口分別接收來(lái)自2號(hào)和3號(hào)處理器的處理結(jié)果,并將二者再次進(jìn)行波束合成,然后進(jìn)行脈沖壓縮,最終輸出脈沖壓縮結(jié)果。1號(hào)處理器運(yùn)行時(shí)間評(píng)估如表3所示。

1號(hào)處理器總的運(yùn)行時(shí)間為4.168 ms。根據(jù)項(xiàng)目要求輸出數(shù)據(jù)點(diǎn)數(shù)縮短為每波束1 760點(diǎn),同時(shí)由3個(gè)光纖口輸出。

通過(guò)以上分析可知,所設(shè)計(jì)系統(tǒng)在功能和實(shí)時(shí)性上均能滿足項(xiàng)目要求。

3 應(yīng)用

本文所設(shè)計(jì)系統(tǒng)已被成功應(yīng)用于某大型項(xiàng)目中。在該項(xiàng)目中,本系統(tǒng)實(shí)時(shí)接收來(lái)自3個(gè)接收機(jī)柜的48通道基帶數(shù)據(jù),并分高、低頻段選取不同的32通道數(shù)據(jù),先通過(guò)光纖接口輸出,然后完成對(duì)32通道數(shù)據(jù)的校準(zhǔn)、波束合成及脈沖壓縮處理,最后通過(guò)光纖接口將處理結(jié)果輸出。該系統(tǒng)實(shí)現(xiàn)了項(xiàng)目所要求的各種功能和性能指標(biāo),并且系統(tǒng)運(yùn)行穩(wěn)定,達(dá)到了預(yù)期目標(biāo)。

4 結(jié)論

根據(jù)項(xiàng)目要求,本文提出了一種基于DSP和FPGA的實(shí)時(shí)陣列信號(hào)處理系統(tǒng)設(shè)計(jì)方法。系統(tǒng)通過(guò)高速光纖接口實(shí)現(xiàn)外部數(shù)據(jù)的接收和發(fā)送,內(nèi)部處理器之間通過(guò)Link口進(jìn)行數(shù)據(jù)交換;處理器每秒48億次40位浮點(diǎn)乘累加運(yùn)算及多處理器設(shè)計(jì)使系統(tǒng)具備超強(qiáng)的實(shí)時(shí)運(yùn)算能力;單片處理器24 MB內(nèi)存及擴(kuò)展的256 MB外部存儲(chǔ)器,充分滿足大數(shù)據(jù)量的存儲(chǔ)需求。該系統(tǒng)已成功應(yīng)用到某大型項(xiàng)目中,實(shí)現(xiàn)了項(xiàng)目提出的各種功能及指標(biāo)要求,驗(yàn)證了本系統(tǒng)設(shè)計(jì)的可行性。

本系統(tǒng)在接口、存儲(chǔ)資源、處理速度等都方面都有冗余,易于系統(tǒng)升級(jí)改造以及滿足其他項(xiàng)目的應(yīng)用需求;系統(tǒng)結(jié)構(gòu)采用對(duì)稱(chēng)設(shè)計(jì),對(duì)不同結(jié)構(gòu)的算法具有較強(qiáng)的適應(yīng)能力;本系統(tǒng)也是一種通用的實(shí)時(shí)信號(hào)處理運(yùn)算平臺(tái),可直接應(yīng)用于其他項(xiàng)目的實(shí)時(shí)信號(hào)處理系統(tǒng),對(duì)同類(lèi)實(shí)時(shí)信號(hào)處理系統(tǒng)的設(shè)計(jì)具有重要的參考價(jià)值。

參考文獻(xiàn)

[1] 王魁,楊健.基于TS201的外輻射源雷達(dá)信號(hào)處理系統(tǒng)[J].數(shù)據(jù)采集與處理,2013,28(4):444-449.

[2] 王峰,李婧,劉俊,等.寬帶數(shù)字陣?yán)走_(dá)數(shù)字波束形成系統(tǒng)研究[J].雷達(dá)學(xué)報(bào),2013,2(3):314-318.

[3] GUPTA P, GUPTA D. Design and implementation of FPGA based signal processing card[J]. International Journal of VLSI design & Communication Systems(VLSICS), 2011,2(3):131-137.

[4] MURALI H S, MEENAKSHI M. Design and development of FPGA based data acquisition system for process automation[J]. Communications in Control Science and Engineering(CCSE), 2013,1(1):7-11.

[5] Zhang Xiaojing, Yue Yajie, Sha Chenming. Design and implementation of a multichannel pulse compression system based on FPGA[J]. Journal of Computers, 2013,8(1):121-128.

[6] 竺紅偉,梁之勇.一種通用無(wú)人機(jī)載SAR實(shí)時(shí)信號(hào)處理系統(tǒng)設(shè)計(jì)[J].航天電子對(duì)抗,2013,29(3):29-31.

[7] Wu Wei, Wang Jun, Li Wei, et al. Design methods of multi-DSP parallel processing system[C]. World Congress on Computer Science and Information Engineering, 2009,3: 458-464.

[8] 周杰,李小娟,張偉,等.一種通用雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)[J].電子科技,2013,26(5):91-94.

[9] 李鑫,姜明.多核DSP高速實(shí)時(shí)信號(hào)處理系統(tǒng)設(shè)計(jì)[J].光學(xué)技術(shù),2012,38(1):116-120.

[10] 陳新峰,張軍杰,趙非,等.基于TS201芯片的雷達(dá)信號(hào)處理機(jī)設(shè)計(jì)[J].電子設(shè)計(jì)工程,2011,19(13):156-158.