文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2015.09.013

中文引用格式: 劉崇輝,任建偉,李科,等. TO-252封裝電磁仿真分析[J].電子技術(shù)應(yīng)用,2015,41(9):48-50,59.

英文引用格式: Liu Chonghui,Ren Jianwei,Li Ke,et al. Analysis of the performance of PCB and bonding wire in TO-252 package[J].Application of Electronic Technique,2015,41(9):48-50,59.

0 引言

封裝具有支撐、保護(hù)、冷卻的作用,并為芯片提供電氣連接和隔離,以便器件與其他元件構(gòu)成完整的電路。隨著封裝技術(shù)的不斷發(fā)展,工藝尺寸越來越小,工作頻率越來越高,封裝中的鍵合線不能再簡單地視為無電阻、無電感、無電容的傳輸線。因此在頻率較高的情況下,鍵合線會對封裝中信號的完整性產(chǎn)生影響。表面貼裝式是封裝的管腳及散熱法蘭焊接在PCB表面的焊盤上。而PCB傳輸線會產(chǎn)生材料的導(dǎo)體損耗和介質(zhì)損耗,因此,PCB板也有可能對封裝中信號的傳輸特性產(chǎn)生影響。本文主要通過仿真分析鍵合線和PCB對TO-252表面貼裝式封裝技術(shù)中信號傳輸?shù)挠绊憽?/p>

1 TO-252管殼建模

MOSFET芯片都有一定的工作頻率范圍,為了使芯片能正常工作,需要為芯片選取適合的封裝,也就是要求封裝的工作頻率范圍能夠覆蓋芯片的工作頻率范圍。那我們就有必要了解每種封裝的工作頻率范圍。本文是根據(jù)TO-252封裝的尺寸圖,利用HFSS 進(jìn)行建模仿真,通過查看S參數(shù)來判斷TO-252適用的工作頻率范圍。這里主要查看S21,即插入損耗,也就是有多少能量被傳輸?shù)侥康亩耍@個值越大越好,理想值是1,即0 dB,S21越大傳輸?shù)男试礁撸话憬ㄗhS21>-3 dB。

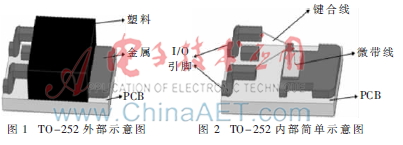

利用HFSS建立TO-252封裝模型如圖1和圖2,底層為PCB板,管殼采用的是塑料封裝。輸入輸出(I/O)引腳是通過鍵合線和微帶線連接在一起。TO-252封裝尺寸圖這里就不做過多的研究,本文主要從PCB板材、厚度和鍵合線的根數(shù)、長度、拱高,鍵合線間的距離等方面來研究對TO-252封裝的影響。

2 PCB板

PCB是電子元器件的支撐體,是電子元器件電氣連接的載體。利用HFSS仿真S參數(shù),需要添加波或集總端口激勵,而波或集總端口激勵需要通過傳輸線傳輸,鑒于TO-252封裝引腳本身只有金屬,不能夠成微帶線,如果只是單獨仿真TO-252信號無法進(jìn)行傳輸,因此,需要采用PCB和TO-252封裝一起仿真。這樣就會使PCB的板材和厚度對TO-252封裝的信號傳輸特性產(chǎn)生影響。

2.1 PCB板材影響

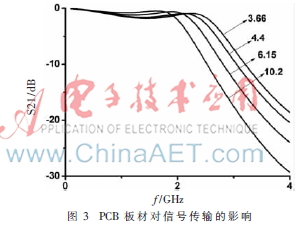

利用HFSS建好模型,設(shè)置PCB板的厚度為1 mm,選取不同的PCB板材,介電常數(shù)分別為3.66、4.4、6.15、10.2,仿真分析不同板材對信號傳輸?shù)挠绊懀瑘D3是給出不同板材下插入損耗(S21)的仿真結(jié)果。

從圖3可以看出:(1)在頻率較低時,隨著板材介電常數(shù)的增大,信號的傳輸特性越好。而高頻時,隨著板材介電常數(shù)的增大,信號的傳輸越來越差。(2)隨著板材介電常數(shù)的增大,信號傳輸較好的帶寬越來越窄。

2.2 PCB厚度仿真

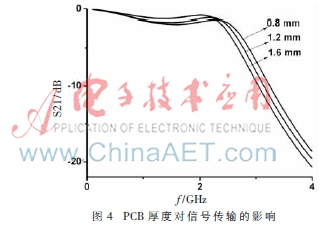

利用HFSS建好模型,設(shè)定PCB的板材為FR_4,將PCB板的厚度設(shè)置為0.8 mm、1.2 mm、1.6 mm,仿真分析不同厚度的PCB對信號傳輸?shù)挠绊懀瑘D4是給出不同厚度下插入損耗(S21)的仿真結(jié)果。

從圖4可以看出:(1)在2 GHz以下時,隨著板材厚度增加,信號的傳輸特性越好。而到2 GHz以上時,隨著板材厚度增大,信號的傳輸衰減的較快。(2)隨著板材厚度的增大,信號傳輸?shù)挠行捲絹碓秸?/p>

綜合圖3和圖4,為了兼顧信號的傳輸和帶寬,需要根據(jù)需求,選取適合的PCB板材和厚度。

3 鍵合線

鍵合線互連是晶體管中管芯和外部環(huán)境進(jìn)行電氣連接的主要手段,具有分配直流偏置電流,為射頻信號提供傳輸途徑的作用[2,3]。隨著器件尺寸的縮小和工作頻率的提高,當(dāng)工作頻率高于1 GHz時,鍵合線的射頻等效串聯(lián)電感、并聯(lián)電容等計生參數(shù)將對信號的傳輸產(chǎn)生很大的影響[4]。因此,關(guān)于鍵合線的設(shè)計和優(yōu)化也十分重要,關(guān)于鍵合線的研究主要有不同材料鍵合線的分析[5,6]、引線鍵合工藝[7]、鍵合線幾何模型參數(shù)研究[8]、電氣特性[9]等。

本文采用鍵合線互聯(lián)的機構(gòu),將芯片的輸入輸出和封裝的引腳連接起來。借助HFSS仿真軟件,對TO-252封裝中鍵合線的長度、拱高、鍵合線間的距離、根數(shù)進(jìn)行仿真,分析改變以上幾種參數(shù)對信號傳輸特性的影響。

3.1 鍵合線長度的影響

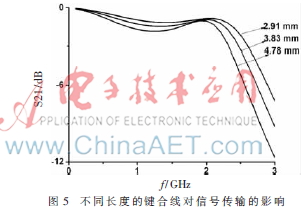

設(shè)定鍵合線間距離為0.5 mm,仿真分析改變鍵合線的長度對信號傳輸?shù)挠绊憽8淖冮L度為2.91 mm、3.83 mm、4.78 mm。圖5是給出不同長度下插入損耗(S21)的仿真結(jié)果。

從圖5可以看出:(1)隨著鍵合線長度的增加,插入損耗越來越大,信號的傳輸特性也越來越差。(2)隨著鍵合線長度的增加,傳輸信號的有效帶寬也越來越窄。因此,為了信號更好的傳輸,要盡可能地縮短鍵合線的長度。

3.2 鍵合線拱高的影響

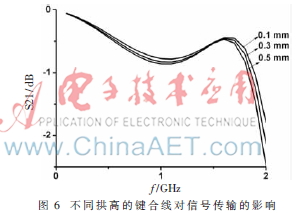

設(shè)定鍵合線的長度為3.71 mm,根數(shù)為2根(連接輸入輸出引腳各一根),鍵合線間的距離為0.5 mm,改變拱高為0.1 mm、0.3 mm、0.5 mm。仿真分析改變鍵合線的拱高對信號傳輸?shù)挠绊憽D6是給出不同拱高下插入損耗(S21)的仿真結(jié)果。

從圖6可以看出:(1)隨著鍵合線拱高的增大,插入損耗越來越大,信號的傳輸特性也越來越差。(2)隨著鍵合線拱高的增大,傳輸信號的有效帶寬也越來越窄。由此平直的的鍵合線是最好的,但平直鍵合線受力集中,易斷裂。因此,考慮到信號的傳輸和鍵合線的受力問題,要選取合適鍵合線的拱高。

3.3 鍵合線間距的影響

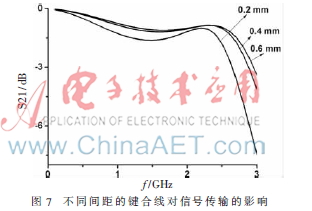

設(shè)定鍵合線的拱高為0.2 mm,根數(shù)為2根(連接輸入輸出的各一根),鍵合線的長度為3.71 mm。改變鍵合線間的距離為0.2 mm、0.4 mm、0.6 mm。仿真分析改變鍵合線間的距離對信號傳輸?shù)挠绊憽D7是給出不同鍵合線間距下插入損耗(S21)的仿真結(jié)果。

從圖7可以看出,隨著鍵合線間距的增大,插入損耗越來越小,信號的傳輸特性越來越好。傳輸?shù)挠行捯苍絹碓綄挕R虼耍瑸榱诵盘柛玫膫鬏敚M可能增加鍵合線間的距離。

3.4 鍵合線根數(shù)的影響

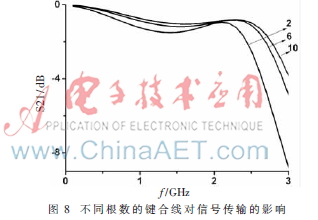

設(shè)定鍵合線的拱高為0.2 mm,鍵合線的長度為3.71 mm。鍵合線間的距離為0.1 mm。仿改變鍵合線的根數(shù)為2、6、10(連接輸入,輸出的各占總數(shù)的一半),仿真分析改變鍵合線的根數(shù)對信號傳輸?shù)挠绊憽D8是給出不同根數(shù)鍵合線下插入損耗(S21)的仿真結(jié)果。

從圖8可以看出:(1)隨著鍵合線根數(shù)的增加,插入損耗越來越好,信號的傳輸特性也越來越好。(2)隨著鍵合線根數(shù)的增加,信號傳輸?shù)挠行捲鰧挕R话闱闆r下,增加鍵合線的根數(shù),可能會減小鍵合線間的距離,這樣也有可能使插損變大,因此,要選取適合鍵合線的根數(shù)和鍵合線間的距離,才能實現(xiàn)信號更好的傳輸。

4 結(jié)束語

綜合上述研究發(fā)現(xiàn):(1)PCB板材介電常數(shù)越大、厚度越高,插損越小,信號傳輸特性越好。但其有效工作帶寬隨著介電常數(shù)的增大而變小。因此,在工程中,需要根據(jù)自己的需求,選擇合適的PCB板材和厚度。(2)鍵合線的長度越短、拱高越小、根數(shù)越多、鍵合線間的距離越大,此時插入損耗最小,信號的傳輸特性最好。通過借助HFSS仿真軟件,模擬分析PCB和鍵合線對封裝系統(tǒng)中信號傳輸?shù)牡挠绊懀瑸閷嶋H封裝提供了可靠的依據(jù)。

參考文獻(xiàn)

[1] 劉俊永,孫文超,崔嵩,等.AlN多層共燒陶瓷微波外殼的設(shè)計與制作[J].電子元件與材料,2012,31(7):1-4.

[2] PETER H A,JAIME A P,JOHN W.Modeling and charac-terization of RF and microwave power FETS[M].New York:Cambridge University Press,2007:126-127.

[3] LIM J H,KWON D H,RIEH J S,et al.RF characterizationand modeling of various wire bond transitions[J].IEEE Transactions on Advanced Package,2005,28(4):772-778.

[4] 周永強,王立新,張萬榮,等.射頻功率晶體管內(nèi)匹配技術(shù)中鍵合線的建模仿真與參數(shù)提取[J].電子器件,2011,34(4):363-366.

[5] KUMAR B S,ALBERT A,LIM L H G.Effect of die attachmaterial on heavy Cu wire bonding with Au coated Pd bond pad in automotive application[C].IEEE Electronics Packaging Technology Conference,2013:618-624.

[6] LIAO J K,LIANG Y H,LI W W,et al.Silver alloy wire bonding[C].2012ECTC:1163-1168.

[7] 宗飛,王志杰,徐艷博,等.電子制造中的引線鍵合[J].電子與封裝,2013,13(1):1-8.

[8] SUTONO A,CAFARO G,LASKAR J,et al.Experimental modeling repeatability investigation and optimization of microwave bond wire interconnects[J].IEEE Trans Adv.2001,24(4):595-603.

[9] 周燕,孫玲,景衛(wèi)平.IC封裝中引線鍵合互聯(lián)特性分析[J].中國集成電路,2006(11):55-57.

[10] 楊玲玲,孫玲,孫海燕.IC封裝中鍵合線傳輸結(jié)構(gòu)的仿真分析[J].電子與封裝,2014(9):1-4.