文獻(xiàn)標(biāo)識嗎: A

DOI:10.16157/j.issn.0258-7998.2015.11.020

中文引用格式: 李良光,余芳芳,曹玲玲,等. 基于FPGA的微震信息采集系統(tǒng)研究[J].電子技術(shù)應(yīng)用,2015,41(11):70-73.

英文引用格式: Li Liangguang,Yu Fangfang,Cao Lingling,et al. Research of microseism information acquisition system based on FPGA[J].Application of Electronic Technique,2015,41(11):70-73.

0 引言

隨著社會經(jīng)濟(jì)和科學(xué)技術(shù)的發(fā)展,礦山開采技術(shù)越來越成熟,但地質(zhì)的微震活動會引發(fā)很多災(zāi)難[1]。目前,人們通過對微震數(shù)據(jù)的分析能夠預(yù)測微震發(fā)生的時間和位置,對礦山井下很多由于沖擊壓力危害帶來的災(zāi)難問題得到一定程度的預(yù)防和治理,但在利用微震監(jiān)測技術(shù)以及相關(guān)設(shè)備的性能方面還存在很多的缺陷[2]。針對這一情況,設(shè)計(jì)了一種基于FPGA的煤礦井下微震信息采集和傳輸系統(tǒng)。

1 微震信息采集系統(tǒng)總體設(shè)計(jì)

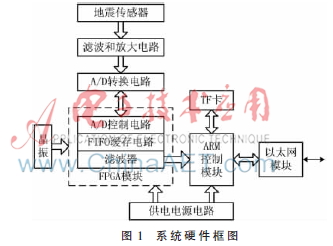

微震信號采集系統(tǒng)硬件框圖如圖1所示,主要由電源電路、前端調(diào)理電路、A/D轉(zhuǎn)換電路、FPGA及ARM系統(tǒng)及其接口電路、TF卡存儲電路、以太網(wǎng)控制器這幾大部分組成。考慮到微震波特點(diǎn),其采集的信號頻率范圍在20 Hz~500 Hz之間[3],系統(tǒng)采用12路信息采集,選擇特殊的地震傳感器采集微震信號;采集的微震信號經(jīng)過調(diào)理電路進(jìn)行初步放大和模擬濾波處理,送往A/D轉(zhuǎn)換器;轉(zhuǎn)換后的數(shù)字信號送往FPGA,在FPGA中設(shè)計(jì)有高速緩存電路和數(shù)字濾波器,對信號進(jìn)行緩存和數(shù)字濾波處理,處理后的數(shù)據(jù)經(jīng)ARM通過以太網(wǎng)送往上位機(jī)。當(dāng)與上位機(jī)連接中斷時,信息可臨時存儲在TF卡中[4]。

2 硬件設(shè)計(jì)

2.1 前端調(diào)理電路

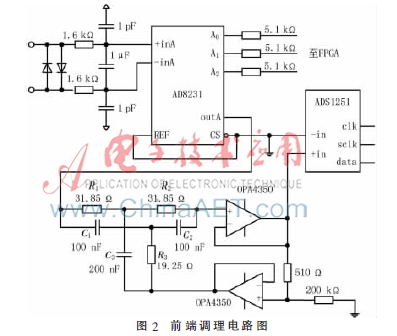

由于采集的微震信號中包含大量的干擾信號,因此信號經(jīng)過放大后還需要進(jìn)行初步濾波[4-5]。圖2為前端調(diào)理電路,設(shè)計(jì)了一個正反饋雙T形50 Hz窄帶陷波器[6],濾波后的信號送入OPA4350運(yùn)算放大器,最后進(jìn)入A/D轉(zhuǎn)換電路。

2.2 A/D轉(zhuǎn)換電路

當(dāng)差分信號輸入到ADS1251中,首先進(jìn)入4階∑-▽調(diào)制器進(jìn)行調(diào)制,該調(diào)制器的調(diào)制時鐘來自系統(tǒng)時鐘分頻。調(diào)制好的信號進(jìn)入ADS1251的內(nèi)部數(shù)字濾波器,濾波器對信號進(jìn)行加權(quán)、計(jì)算得出平均值。最后數(shù)據(jù)通過ADS1251的串行接口輸出,方便與后端處理器連接[7]。ADS1251的電路接口如圖3所示,由于ADS1251引腳電平為+5 V,與其連接的FPGA的引腳電平為+3.3 V,在兩個芯片之間需要增加電平轉(zhuǎn)移芯片,完成兩個芯片不同電平的匹配。ADS1251的CLK引腳和SCLK引腳使用74HCT244作為緩沖器,信號輸出引腳則使用74LCX244作為緩沖器。

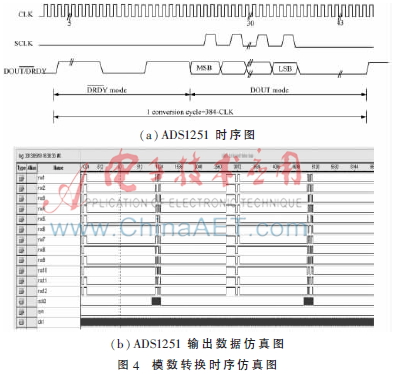

ADS1251是24位的低功耗模數(shù)轉(zhuǎn)換器,輸出的最高位是符號位,其余23位為有效位。當(dāng)外部采樣時鐘頻率為8 MHz時,采樣率fs=fclk/384=20.833 kHz,其中384個時鐘為一個周期。ADS1251工作模式有兩種,當(dāng)DOUT/DRDY引腳輸出高電平時為同步模式,反之為掉電模式。為了保證12路采集信號實(shí)時同步到達(dá)服務(wù)器,本系統(tǒng)的ADS1251采用同步模式,并且每60 s向12路ADS1251發(fā)送一次同步信號。

ADS1251的數(shù)據(jù)轉(zhuǎn)換和同步由DOUT/DRDY引腳控制。當(dāng)DOUT/DRDY輸出高電平時,表示ADS1251處于轉(zhuǎn)換狀態(tài),當(dāng)電平由高轉(zhuǎn)低時,轉(zhuǎn)換結(jié)束,數(shù)據(jù)被存入輸出寄存器中。然后DOUT/DRDY會連續(xù)輸出6個低電平和6個高電平,表示數(shù)據(jù)準(zhǔn)備就緒,進(jìn)入輸出狀態(tài)。數(shù)據(jù)從高位到低位經(jīng)過24個SCLK周期后全部從寄存器中移出,DOUT/DRDY恢復(fù)低電平,等待下次轉(zhuǎn)換到來。因此,在新的轉(zhuǎn)換過程開始前,必須將所有數(shù)據(jù)位讀完,圖4(a)為ADS1251時序圖。

數(shù)據(jù)轉(zhuǎn)換的384個時鐘周期中,前36個為DRDY狀態(tài),后348個時鐘為DATA狀態(tài),這樣就可以保證24位數(shù)據(jù)讀取完畢后才進(jìn)入下次轉(zhuǎn)換。如果SCLK不到24個時鐘周期,DOUT/DRDY引腳將保持未讀出的當(dāng)前數(shù)據(jù)直到下一個轉(zhuǎn)換周期。如果超過24個周期,則DOUT/DRDY引腳為低電平。

綜上分析可知,F(xiàn)PGA對ADS的轉(zhuǎn)換控制中,保持與DOUT/DRDY信號同步非常重要,如果在最低數(shù)據(jù)位LSB還沒讀出前,DOUT/DRDY引腳就進(jìn)入DRDY狀態(tài),會導(dǎo)致LSB讀取失敗。

根據(jù)上述流程,通過Verilog編程,在QUARTUSII的嵌入式邏輯分析儀SIGNALTAPII上進(jìn)行了仿真,仿真結(jié)果如圖4(b)所示。由仿真結(jié)果可以看出,在數(shù)據(jù)讀取狀態(tài),12路通道能夠同時讀取信息。

2.3 FPGA中數(shù)據(jù)緩存及傳輸實(shí)現(xiàn)與仿真

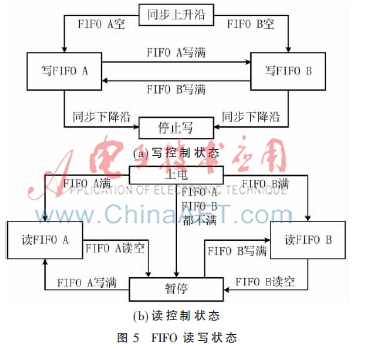

乒乓操作是一種數(shù)據(jù)流的處理技巧,在處理大數(shù)據(jù)量的緩存和傳輸時,避免使用單個FIFO,讀寫操作不能同時進(jìn)行,效率低下,因此常采用兩個FIFO的乒乓緩存機(jī)制來實(shí)現(xiàn)數(shù)據(jù)的無縫傳輸[8]。乒乓緩存的原理為:當(dāng)系統(tǒng)對兩個緩存模塊的其中一個進(jìn)行寫數(shù)據(jù)時,另一個緩存模塊則讀數(shù)據(jù),當(dāng)兩個模塊分別讀空和寫滿時,兩者通過節(jié)拍配合,互換讀寫操作。使用這種方法,寫入和讀出數(shù)據(jù)操作可以沒有任何停頓,因此可以完成數(shù)據(jù)的無縫緩存和傳輸[9]。

乒乓操作流程為:將采集到的數(shù)據(jù)首先寫入FIFO A,這時是沒有輸出的;當(dāng)FIFO A寫滿后,輸入控制模塊會自動切換到FIFO B,將數(shù)據(jù)寫入FIFO B中,同時輸出控制模塊對FIFO A進(jìn)行讀操作;當(dāng)FIFO B寫滿時,輸入控制模塊會再次切換到FIFO A,進(jìn)行寫操作,同時輸出切換到FIFO B。

基于乒乓緩存機(jī)制的優(yōu)點(diǎn),考慮采集的數(shù)據(jù)量很大,本文在FPGA中設(shè)計(jì)了兩個異步FIFO單元,對數(shù)據(jù)進(jìn)行緩存和無縫傳輸。由于緩存單元前端是ADS轉(zhuǎn)換控制單元,對A/D采樣需要每分鐘進(jìn)行一次同步,在同步期間,是沒有數(shù)據(jù)寫入緩存單元的,但是這并不影響數(shù)據(jù)的讀操作。乒乓緩存單元的整體思想是:不滿不讀,滿了讀完,讀空暫停。

為了保證兩個FIFO正常切換,需要設(shè)計(jì)專門的讀、寫控制模塊,簡化復(fù)雜的時序命令,并且避免出錯。其數(shù)據(jù)讀寫狀態(tài)控制過程如圖5所示。

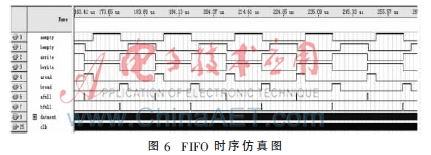

由于采用乒乓操作讀寫數(shù)據(jù),對單個緩存的空間要求降低,因此兩個緩存模塊的存儲寬度和深度都選擇為32 B。在QUARTUSII上對乒乓操作進(jìn)行時序仿真,結(jié)果如圖6所示,F(xiàn)IFO A和FIFO B有“full”和“empty”兩種狀態(tài),且讀寫操作總是交替進(jìn)行的。由于讀操作的頻率為20 MHz,寫操作的頻率只有fw=(3.84 M/384)/24=0.417 kHz,可見,數(shù)據(jù)讀出快于寫入,在一個FIFO數(shù)據(jù)被讀空后,有較長的暫停時間,方便后面的濾波器對數(shù)據(jù)進(jìn)行處理。

2.4 數(shù)字濾波器的設(shè)計(jì)與仿真

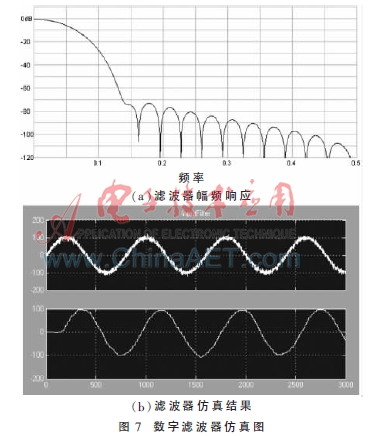

本文在FPGA中設(shè)計(jì)了一個32階的抽樣頻率為200 kHz、截止頻率為1 kHz的FIR低通濾波器[10]。在MATLAB中對濾波器進(jìn)行仿真,得到的幅頻響應(yīng)如圖7(a)所示,濾波器的輸入中含有大量噪聲,輸出信號噪聲明顯減小,如圖7(b)所示。從濾波前后的波形對比可以看出,F(xiàn)PGA中實(shí)現(xiàn)的濾波器,能消除大量的高頻噪聲,但是有一定的時間延遲,需要修正。

3 實(shí)驗(yàn)測試與結(jié)果分析

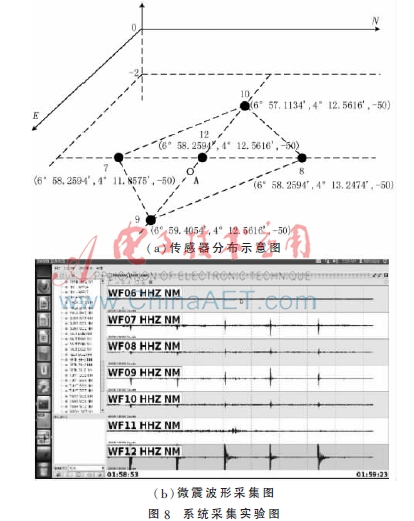

為了測試系統(tǒng)采集微震信息是否準(zhǔn)確有效,通過對傳感器不同的布放,進(jìn)行了模擬現(xiàn)場實(shí)驗(yàn)。在12路通道中選擇7、8、9、10、12這5個傳感器作為實(shí)驗(yàn)通道,各通道對應(yīng)的傳感器分布位置如圖8(a)所示。除12路傳感器外,其余4個傳感器分布點(diǎn)組成了一個正方形,12路傳感器位置在該正方形的中心點(diǎn),傳感器的放置深度均為地下2 m。同時,設(shè)置前端調(diào)理電路的增益值為64。

圖8(a)中A點(diǎn)坐標(biāo)處為人工震源點(diǎn),實(shí)驗(yàn)前,記錄各路傳感器及震源坐標(biāo),在確定系統(tǒng)正常后,在A點(diǎn)進(jìn)行敲擊,各傳感器將檢測到的數(shù)據(jù)傳至上位機(jī)。

在上位機(jī)觀察到的采集信息如圖8(b)所示,其中距離震源非常近的12路傳感器最先采集到微震信息,且強(qiáng)度最高;另外幾路傳感器也監(jiān)測到了微震信息,其中7路和9路相對于8路和10路,距震源較近,所以先檢測到微震波形,且幅度也較高。

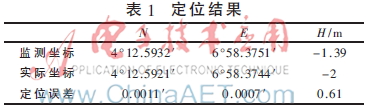

震源定位的算法有很多種,在本次實(shí)驗(yàn)中,上位機(jī)采用的是Geiger定位方法,其主要思想是將第一監(jiān)測到微震信號的傳感器位置坐標(biāo)作為迭代初值,將多路監(jiān)測數(shù)據(jù)依次代入運(yùn)算,最后得到較準(zhǔn)確的震源位置。實(shí)驗(yàn)得到震源定位結(jié)果如表1所示。

由于實(shí)驗(yàn)條件和場地限制,傳感器都布置在同一平面內(nèi),對震源深度定位帶來較大誤差。要想得到更加精確的定位監(jiān)測結(jié)果,還需要完善上述實(shí)驗(yàn),如擴(kuò)大監(jiān)測范圍,增加傳感器數(shù)量及采用立體布點(diǎn)等措施。

4 結(jié)語

微震波在預(yù)測地質(zhì)運(yùn)動趨勢中有非常重要的作用,通過對微震信號的實(shí)時監(jiān)測和分析,可以判斷潛在威脅,有效規(guī)避煤礦采集作業(yè)過程中由于地質(zhì)微運(yùn)動引起的礦難。本文針對微震信號的特點(diǎn),設(shè)計(jì)了一套基于FPGA的微震信號采集系統(tǒng),該系統(tǒng)采用非常靈敏的微震檢波器采集微震信號,通過調(diào)理電路,對微震信號進(jìn)行初步濾波和放大處理,然后通過24位∑-▽型模數(shù)轉(zhuǎn)換器ADS1251對其進(jìn)行轉(zhuǎn)換,送入FPGA中進(jìn)行緩存、濾波處理,最后通過以太網(wǎng)送入上位機(jī)。系統(tǒng)不僅速度快、運(yùn)行穩(wěn)定,且功耗低、體積小,系統(tǒng)結(jié)構(gòu)簡單,可推廣到我國的煤炭行業(yè),具有良好的應(yīng)用前景。

參考文獻(xiàn)

[1] 劉建坡.深井礦山地壓活動與微震時空演化關(guān)系研究[D].沈陽:東北大學(xué),2011(3).

[2] 李庶林.試論微震監(jiān)測技術(shù)在地下工程中的應(yīng)用[J].地下空間與工程學(xué)報(bào),2009,5(1):121-128.

[3] 郭來功,歐陽名三.一種高精度微震信息采集系統(tǒng)[J].儀表技術(shù)與傳感器,2013(11):65-73.

[4] 余芳芳,郭來功,李良光.基于STM32F407的微震信息采集系統(tǒng)設(shè)計(jì)[J].工礦自動化,2014,40(7):9-12.

[5] 襲江濤.基于FPGA的高精度地震勘探數(shù)據(jù)采集系統(tǒng)[D].成都:成都理工大學(xué),2007(5).

[6] 蔣亞超,楊勇,李興東,等.三種雙T網(wǎng)絡(luò)陷波電路分析與比較[J].電子技術(shù),2011(1):70-72.

[7] 曹利波.ADS1251在微震檢測裝置中的應(yīng)用[J].電子制作,2014(6):10-11.

[8] 陳標(biāo)龍,王保成,周江華.基于FPGA和FIFO技術(shù)的多串口系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)測量與控制,2013,21(10):2835-2837.

[9] 謝廷婷,彭鼎祥,鄭積仕.一種多通道動態(tài)均衡先進(jìn)先出緩存機(jī)制[J].太赫茲科學(xué)與電子信息學(xué)報(bào),2013,11(6):897-901.

[10] 韓建,何學(xué)蘭,魏運(yùn)峰.基于FPGA的FIR數(shù)字濾波器算法的改進(jìn)及仿真[J].光學(xué)儀器,2013,35(5):56-70.