文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.022

中文引用格式: 祁志恒,姜喆,張為. 基于ADV212的雷達圖像壓縮傳輸系統(tǒng)[J].電子技術應用,2015,41(11):78-80,84.

英文引用格式: Qi Zhiheng,Jiang Zhe,Zhang Wei. Radar image compress and transfer system based on ADV212[J].Application of Electronic Technique,2015,41(11):78-80,84.

0 引言

雷達在現代海上交通運輸中發(fā)揮著不可替代的作用。雷達圖像具有分辨率高、數據量大、實時性要求高等特點,現代雷達獲取的有效數據可達100 Mb/s~200 Mb/s,巨大的數據量為雷達圖像的傳輸與存儲帶來了一定的困難[1]。目前雷達數據采用PCI總線或光纖等傳輸方式,雖然可以實現高帶寬,但是在傳輸距離和成本上受到限制,而以太網傳輸距離遠、成本低,配合數據壓縮可以用來傳輸海量雷達數據,并方便雷達數據共享及遠程岸上站點或移動設備接收。JPEG2000作為新一代靜態(tài)圖像壓縮標準非常適合雷達圖像的壓縮[2-3],相比于JPEG等靜態(tài)圖像壓縮算法,JPEG2000有以下優(yōu)點[4]:(1)可以支持有損和無損壓縮;(2)支持更大的圖像分辨率;(3)感興趣區(qū)域編碼(ROI);(4)抗誤碼性;(5)圖像加密等。ADV212[5-7]是一款單芯片JPEG2000編解碼器,針對視頻和高帶寬圖像壓縮應用,使之能受益于JPEG2000 ISO/IEC15444-1圖像壓縮標準所提供的增強畫質與功能。該器件可實現JPEG2000圖像壓縮標準的計算密集型操作[8-9],并且提供完全兼容、適合多數應用的碼流產生方法[10]。

本文在深入分析雷達圖像特點的基礎上,設計了一種低延時的適合雷達圖像實時壓縮并傳輸的處理方式,并以此為基礎設計了以FPGA和ADV212為核心的雷達圖像壓縮與傳輸系統(tǒng)。根據系統(tǒng)對空間的要求,所設計系統(tǒng)體積小、重量輕,可作為一個模塊添加到整體系統(tǒng)中,只占用很小的空間。

1 系統(tǒng)總體設計

某型號雷達掃描周期為1.5 s,每個掃描周期共有4 096級方位量化,在探測距離最大時有4 096級距離量化,采樣精度為12 bit。本設計要求壓縮系統(tǒng)的采樣率達到16 MS/s,外形尺寸小于10 cm×10 cm,重量不超過200 g。

基于以上需求,本系統(tǒng)采用支持JPEG2000的ADV212作為壓縮芯片,ADV212支持有損和無損壓縮,支持5/3和9/7小波變換。無損壓縮模式下,支持45 MS/s的數據輸入速率,有損模式下,支持65 MS/s的數據輸入速率。對于單分量靜態(tài)圖像,支持的最大分辨率為4 096×4 096,一片ADV212每幅圖像的采樣點最多為1.048 MB,單片ADV212即可滿足系統(tǒng)的指標要求。另外,系統(tǒng)采用W5500作為以太網傳輸芯片,采用Altera ep3c55 FPGA實現各功能模塊和系統(tǒng)控制。

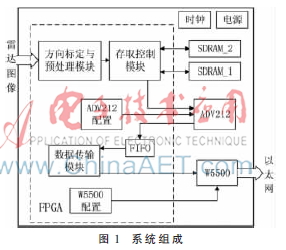

圖像壓縮系統(tǒng)主要由方向標定與預處理模塊、存取控制模塊、圖像壓縮模塊、數據傳輸模塊構成。整個壓縮過程如下:由信號采集前端接收雷達回波信號,捕獲正北方位標志和每個掃描脈沖的開始采樣點,丟棄超出范圍的采樣信號,將得到的數據經預處理后交給存取控制模塊,存取控制模塊分塊將圖像乒乓緩存到兩片SDRAM中,在將數據存到1片SDRAM中的同時從另一片SDRAM中讀取圖像數據,然后把數據和同步信號傳給圖像壓縮模塊;圖像壓縮的核心是ADV212,它由所配置的參數和同步信號處理圖像數據,生成壓縮碼流,然后把生成的壓縮碼流送給傳輸模塊,經網口把壓縮數據傳給上位機進行解碼并顯示。系統(tǒng)組成如圖1所示。

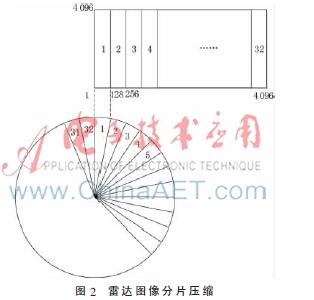

如果將分辨率為4 096×4 096的圖像作為一整幅圖像進行壓縮,可利用幀間相關性,但代價是壓縮必須要等到雷達完成一周期后才能開始,從接收雷達信號到壓縮完傳輸的延遲是雷達旋轉周期的倍數,對于實時性要求極高的雷達信號來說并不適合,因此本文設計了一種延遲更小的分片壓縮方式。將每個雷達旋轉周期內的各個掃描線以128個為一組作為一幅圖像,4 096個掃描線共分成32份,每張圖像的分辨率為128×4 096,如圖2。雷達旋轉360°/(4 096/128)=11.25°就可以開始對圖像進行壓縮,因此減小了接收到傳輸的延時。

2 系統(tǒng)硬件設計

系統(tǒng)采用FPGA實現各模塊的功能,利用FPGA強大的高速并行處理能力和方便的可配置能力,完成以下模塊的設計。

2.1 方向標定與預處理模塊

雷達信號首先經前端模數轉換并加上方位信息后送到壓縮系統(tǒng),壓縮系統(tǒng)接收到的信號中帶有標定正北方向的信息和每個掃描脈沖的首像素位置信息,如圖3所示。如果數據第14位為1就代表此脈沖為正北方向,如果第13位為1就代表此脈沖的第一個像素。方向標定模塊實時監(jiān)測接收到的掃描脈沖信號,在檢測到包含正北方向信息的掃描脈沖時將此脈沖標定為正北方向,在檢測到脈沖首像素信息后表示后面的數據為下一脈沖的數據。對于12位雷達圖像數據,取高8位作為有效數據,一個雷達周期得到4 096×4 096×8 bit的圖像數據。通常輸入的原始信息會存在大量的隨機噪聲,噪聲會降低圖像相鄰像素之間的相關性,影響編碼效率。所以在此對圖像信息進行去噪處理。

2.2 存取控制模塊

系統(tǒng)的數據存儲由兩片SDRAM負責,分別為SDRAM1和SDRAM2,兩片SDRAM構成乒乓緩存。接收到的圖像先存到SDRAM1中,共存128×4 096個像素值,存取控制模塊判斷ADV212是否壓縮完成上一幅圖像,如果完成則在SDRAM1取數傳給ADV212,在SDRAM1取數時把接收到的下一幅圖像存入SDRAM2。如此循環(huán)構成乒乓操作。在取數送給ADV212的過程中,需要為原始圖像數據添加同步信號,同步信號采用獨立于碼流的HVF格式。

2.3 數據壓縮模塊

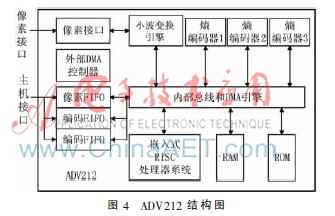

ADV212的結構框圖如圖4所示。ADV212芯片由兩個圖像傳輸接口(像素接口和主機接口)和一些模塊組成,包括小波變換引擎、嵌入式RISC處理器、存儲器系統(tǒng)、3個熵編碼器、可配置FIFO和內外部DMA引擎等。其工作原理為每幀圖像經過預處理、小波變換、量化、算數編碼、率失真優(yōu)化截斷后生成標準的JPEG2000壓縮碼流。ADV212可配置多種接口模式,用戶可通過VDATA總線和HDATA總線輸入原始數據,也可以單獨使用HDATA總線。本系統(tǒng)工作在custome-specific模式,接口為JDATA模式,原始數據由VDATA接口輸入,JDATA接口輸出。VDATA接口支持8、10、12、16位的單分量或多分量YCbCr4:2:2格式視頻,同步信號可以為EAV/SAV模式或HVF模式。ADV212與FPGA的連接方式如圖5所示。

ADV212的MCLK連接頻率為27 MHz的晶振,經內部PLL倍頻后生成JCLK和HCLK作為內部工作時鐘,VCLK是視頻接口工作時鐘,與圖像數據同步。FPGA通過HDATA接口低15位配置ADV212,正確的配置是系統(tǒng)正常工作的關鍵,芯片的配置主要包括PLL配置、固件加載、直接寄存器和簡介寄存器配置等。本文設計ADV212工作在JDATA模式,上電復位后,設置內部PLL,為ADV212工作提供正確的時鐘,等PLL鎖定后設置為No-boot host mode,并設置BUSMODE和MMODE,加載32 kb編碼固件;然后設置soft-reboot,重新設置BUSMODE和MMODE,并設置編碼參數,編碼參數要與輸入的圖像參數一致;使能SWIRQ0,配置正確ADV212將產生軟件中斷;查詢應用程序ID,若讀出0xff82則表明ADV212可以正常工作;清除中斷標志寄存器,ADV212開始工作。

2.4 數據傳輸模塊

數據傳輸模塊使用了Wiznet的W5500芯片,W5500是一款全硬件TCP/IP嵌入式以太網控制器,集成了TCP/IP協議棧,10/100 M以太網數據鏈路層(MAC)及物理層(PHY),使得用戶使用單芯片就能夠在其應用中拓展網絡連接。而且,W5500使用了新的高效SPI協議支持80 MHz速率,從而能夠更好地實現高速網絡通信。本文使用FPGA對W5500進行控制,以Verilog HDL實現SPI接口協議。首先通過SPI接口對W5500進行配置,設置本地IP、子網掩碼、網管、硬件Mac地址、發(fā)送與接收緩存大小、目標IP地址等,并使其工作在UDP模式;數據接收模塊收到ADV212的JDATA接口發(fā)出的壓縮碼流后轉成串行數據交給W5500,W5500自動對數據封裝成UDP包,通過網口發(fā)送給上位機。相比于TCP,UDP是一個非連接的協議,它在傳輸數據時不需要握手,只是將數據盡可能快地發(fā)送到網絡上,所以UDP可以實現更快的傳輸速度。缺點是會帶來丟包的可能性,在網絡穩(wěn)定的情況下,丟包率極低,而且即使發(fā)生丟包,影響解碼圖像的質量,這種影響也不會保留到下一幅圖像,而是控制在當前圖像以內。

3 系統(tǒng)實現

系統(tǒng)的實物尺寸為10 cm×6 cm,重量小于100克,可以方便地加入到原有雷達系統(tǒng)中,只占用很小的空間。在有損模式下,壓縮輸入采樣率可達65 MS/s,在無損模式下,輸入采樣率可達45 MS/s,滿足系統(tǒng)16 MS/s的采樣要求。采用本文的分片壓縮方式,系統(tǒng)不必等雷達掃描一個周期,而是1/32周期即11.25°,便可開始壓縮,從而減小了系統(tǒng)延時。

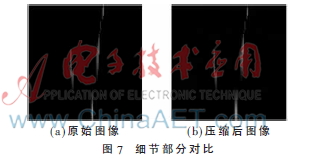

為了測試圖像壓縮系統(tǒng)的性能,在XUPV5-LX110T平臺上搭建了測試系統(tǒng),產生符合要求的原始數據信號,輸入到圖像壓縮系統(tǒng),通過網線連接上位機,圖像經過網線傳輸給上位機,并在上位機對圖像解壓,實驗表明系統(tǒng)完全符合設計要求。試驗中系統(tǒng)采用5/3可逆小波變換,壓縮比為20:1,原始圖像分辨率為4 096×4 096,大小為24 MB,經系統(tǒng)處理壓縮以后結果為1 053 KB,極大地減小了網絡寬帶占用及存儲占用空間,便于遠程數據傳輸。圖6為一幀雷達圖像壓縮后的效果圖,為了對比更清楚,在整體圖中取某一塊進行比較,如圖7所示,壓縮的PSNR為47.17,完全滿足對雷達圖像后期處理的要求。

4 結論

本文在分析了雷達圖像特點的基礎上設計了一款雷達圖像壓縮系統(tǒng),采用FPGA和ADV212專用圖像壓縮芯片為核心,提出了一種將雷達圖像分塊壓縮的壓縮方式,解決了雷達圖像壓縮與實時性要求之間的矛盾,使壓縮結果不僅可以用來做航行記錄儀的雷達圖像記錄,而且還可以用于實時顯示,遠程傳輸等。系統(tǒng)體積小、重量輕、占用空間小,而且由于系統(tǒng)基于FPGA實現,通過重新配置可以用于小型無人機、遠程監(jiān)控等其他場合。

參考文獻

[1] 董鵬曙,張朝偉,金加根,等.高分辨率雷達圖像壓縮編碼算法及實現[J].系統(tǒng)工程與電子技術,2009,31(1):54-56.

[2] 魏江力,柏正堯.JPEG2000圖像壓縮基礎、標準和實踐[M].北京:電子工業(yè)出版社,2004.

[3] 小野定康,鈴木純司.JPEG2000技術[M].北京:科學出版社,2004.

[4] ISO/IEC 15444-1.Information technology-JPEG2000 image coding system-Part 1:Core coding system[S].2000.

[5] Analog Devices.JPEG2000 Video Codec ADV212 Rev.A[S].2008.

[6] Analog Devices.ADV212 JPEG2000 Video Processor User’sGuide[S].2006.

[7] Analog Devices.ADV212 JPEG2000 Programming Guide[S].2007.

[8] 李進,金龍旭,李國寧,等.ADV212在大視場多光譜TDI-CCD空間相機中的應用[J].光譜學與光譜分析,2012,32(6):1700-1707.

[9] 陳柘,段宗濤,陳玲,等.高分辨率航空圖像壓縮系統(tǒng)設計[J].計算機工程與設計,2011,32(8).

[10] 鄧宸偉,趙保軍.基于ADV212的實時圖像壓縮系統(tǒng)[J].電視技術,2008,32(12):35-37.