摘 要: 航天應用中,單粒子翻轉引發(fā)SRAM型FPGA的錯誤最多,而EDAC設計在糾錯模塊中有著廣泛的應用。將依據擴展海明碼設計的[40,32]EDAC模塊嵌入到ARINC 659的雙口數(shù)據DPRAM和指令SRAM中,提高了總線控制器的容錯處理能力。

關鍵詞: ARINC 659;單粒子翻轉;錯誤檢測與糾正;海明碼

0 引言

集成電路的應用領域在不斷深入擴大,航空航天方面要求系統(tǒng)能長期可靠地運行,其運行的環(huán)境輻射比地面輻射嚴重,集成電路很容易受到干擾,導致設備不能正常工作。單粒子翻轉是指高能粒子射入集成電路的PN結,會發(fā)生PN結電離、電荷積累、能量轉移等。存儲器件某一位數(shù)據會從一個穩(wěn)態(tài)轉變?yōu)榱硗庖粋€穩(wěn)態(tài),是引發(fā)航天器故障的主要因數(shù)。

為了最大限度地減少單粒子效應對FPGA的影響,通常采用三模冗余的加固結構,盡管三模冗余結構可以將錯誤暫時隔離,但是在長期工作的情況下冗余單元也可能繼續(xù)發(fā)生錯誤。近年來國內外采用EDAC電路來減少或避免錯誤的發(fā)生。常見的EDAC電路都是采用專用芯片配上時序來工作的,這不利于系統(tǒng)的集成小型化和低功耗。本文基于ARINC 659控制器的設計,利用Verilog HDL實現(xiàn)EDAC的功能,使設計朝著高集成、低功耗的方向發(fā)展[1]。

1 ARINC 659總線技術簡介

ARINC 659[2]是一種航空電子模塊化設計的背板總線標準,有魯棒分區(qū),具有確定的時間和空間性。霍尼韋爾公司根據ARINC 659標準設計的SAFEbus用于波音777的飛機信息管理系統(tǒng)中,從1993年被采納成為行業(yè)標準至今已經穩(wěn)定運行30多年。它能夠應用于大型客機的電子系統(tǒng),表明ARINC 659是一種較為可靠的內總線,適用于航天系統(tǒng)的綜合電子平臺。

在ARINC 659標準中,每一個可插拔的子板被稱作在線可更換模塊(Line Replaceable Module,LRM)。每個LRM有兩個總線接口(Bus Interface Unit,BIU)。在該標準中,一條659總線上最多允許連接32個LRM。ARINC 659使用時間觸發(fā)的調度方式稱為表驅動比例訪問協(xié)議(Table Driven Proportional Access,TDPA),并將決定總線時分復用特性的調度表保存在每個BIU中,維護協(xié)議的數(shù)據開銷非常小。ARINC 659的4線交叉校驗機制可以對每一位進行校驗。

ARINC 659假設每個BIU使用獨立的時鐘,儲存相同的TDPA表,因此在總線工作時是沒有中心控制的分布式系統(tǒng)的。同時,ARINC 659也支持LRM的冗余,協(xié)議中最多允許某項功能有4個LRM做備份。

目前見到的航空總線標準中,ARINC 659總線的實時性、可靠性和冗余度是最高的,但霍尼韋爾公司只提供整機解決方案,不提供芯片,因此研究該總線能為我國航空電子系統(tǒng)開發(fā)與應用提供幫助。

2 EDAC的原理與實現(xiàn)

2.1 海明碼的基本原理

海明碼是一種廣泛使用的可以糾正單個錯誤和檢測任意兩位錯誤的線性分組碼。常見的海明碼應滿足不等式2m≥n+m+1,其中n為數(shù)據碼的位數(shù),m為校驗碼的位數(shù),如果要求既要能糾正一位錯位又能檢測出兩位錯位,則至少需要m+1位校驗碼。該控制器中傳輸32 bit數(shù)據,依據海明碼的原理,使用8 bit校驗位,構成[40,32]擴展海明碼。依據規(guī)則,在數(shù)據位的第2k(k=0,1,2,3,4,5) bit上放置校驗碼。

2.2 EDAC模塊的設計與實現(xiàn)

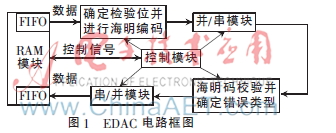

EDAC模塊在CPU與RAM之間[3],保護控制器RAM的數(shù)據,CPU對RAM操作時,EDAC模塊已經對RAM中的數(shù)據進行了預處理,同時EDAC模塊中也加入了使能信號。EDAC主要工作在寫周期和讀周期,如圖1所示,EDAC主要包括發(fā)送和接收兩個部分。

上面發(fā)送模塊負責海明碼編碼,用控制電路寄存器中的數(shù)據位確定校驗位,然后依據海明碼的長度和編碼方案編碼。將并行轉成串行數(shù)據發(fā)出去。接收模塊主要負責海明碼糾錯與解碼,解碼過程就是依據已知校驗位數(shù)確定碼字長度;而糾正就是用已經生成的校驗碼和形成該校驗碼的編碼方程再進行一次異或操作,如果該等式為0,則代表沒有發(fā)生錯誤,若等式為1,說明有錯,可以從等式的值判斷具體的出錯位,糾正后再從碼字中選出數(shù)據位。

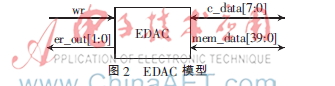

EDAC模塊通過Verilog HDL在FPGA中實現(xiàn),其總體框架如圖2所示,其各變量的含義如下:

wr:CPU讀寫信號,0和1分別表示為寫和讀。

c_data[7:0]:CPU的傳送和接收數(shù)據。

mem_data[39:0]:存儲器數(shù)據包括32 bit數(shù)據位和8 bit校驗位。

er_out[1:0]:錯誤類型,分別為無錯誤、1 bit錯、2 bit及2 bit以上錯、校驗位錯誤。

3 EDAC模塊在ARINC 659總線控制器中的實現(xiàn)

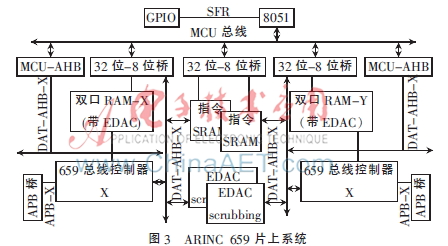

圖3是ARINC 659總線的系統(tǒng)框圖,雙口數(shù)據DPRAM使用[40,32]EDAC編碼保存數(shù)據。8051讀取數(shù)據時,EDAC狀態(tài)寄存器記錄1 bit錯或2 bit錯。EDAC狀態(tài)寄存器有可屏蔽的EDAC中斷。依據海明編碼原理,ARINC 659總線控制器讀取數(shù)據時,1 bit錯直接糾正,2 bit以上的錯不做處理,ARINC 659總線控制器自身能保存正常數(shù)據,2 bit以上的錯誤導致ARINC 659總線校驗全部失效,將數(shù)據錯誤通知其他LRM。

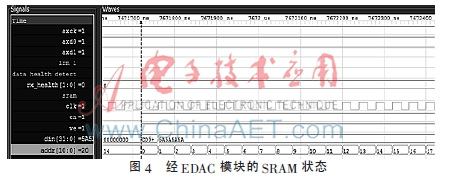

指令SRAM也使用[40,32]EDAC編碼保存數(shù)據,寫入方法與雙端口數(shù)據DPRAM相同。正常狀態(tài)下,ARINC 659總線控制器只讀指令SRAM,指令SRAM自身也有EDAC,但隨著時間累積,單粒子翻轉可能在指令SRAM中累積,最后發(fā)生多位錯。針對這種情況,在ARINC 659指令總線上新增EDAC刷新模塊,它每次讀取指令SRAM的一個字,再將其寫入指令SRAM,可以避免1 bit錯累加形成多位錯。659總線控制器讀取指令SRAM的EDAC狀態(tài)時,對1 bit錯不做處理,對2 bit錯659總線控制器會斷開,另一個659總線控制器依靠交叉使能不一致也會斷開。659總線控制器遇到多位錯將會變?yōu)槲粗獱顟B(tài),最終因為交叉使能不一致也會斷開。圖4是32 bit數(shù)據5A5A5A5A經過EDAC模塊之后的狀態(tài)。

4 注入故障與結果分析

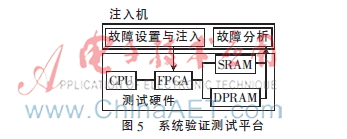

通常SEU發(fā)生頻率與器件所處的軌道位置和工作時間有關,每天SRAM中SEU的發(fā)生約為3×10-5位。為了加快實驗進度,采用與實際情況相似的硬件故障注入方式,故障注入基本頻率為10次/s。其結構如圖5所示,包括注入機和目標機,注入機通過向FPGA發(fā)送命令的方式注入故障,實現(xiàn)故障邏輯[4]。

運行時指令SRAM和數(shù)據DPRAM會同時發(fā)生故障,導致主機失效。本文選用4種程序進行試驗,分別為遞歸(Fibonacci,F(xiàn)I)、快速排序(Quick Sort,QS)、矩陣乘(Matrix Multiplication,MM)和快速傅里葉變換(Fast Fourier Transform,F(xiàn)FT)。同時向指令SRAM和數(shù)據DPRAM中注入1 480 000次故障,主機平均會有475次失效,在這些失效中平均會有452次被檢測到并處理,其可靠性相對不加EDAC時顯著提高。

5 結論

本文研究了EDAC的主要原理和實現(xiàn),針對ARINC 659總線控制器的體系結構與特點,將[40,32]EDAC模塊嵌入數(shù)據DPRAM和指令SRAM中,用來糾正1 bit錯位和檢驗2 bit錯誤。該設計嵌入在FPGA中,與傳統(tǒng)的利用糾錯芯片硬件電路相比,簡化了電路,能快速地實現(xiàn)ARINC 659總線控制器的糾錯檢錯,有效降低了單粒子翻轉效應對存儲器的影響,提升系統(tǒng)的整體性能。

參考文獻

[1] 付劍.星載計算機的硬件容錯設計與可靠性分析[D].長沙:國防科技大學,2009.

[2] 張喜民,魏婷.ARINC659容錯數(shù)據總線測試驗證系統(tǒng)研制[J].西安電子科技大學學報(自然科學版),2011,38(6):140-145.

[3] 劉淑芬.崔星.計算機RAM檢錯糾錯電路的設計與實現(xiàn)[J].航天控制,2003(4):59-67.

[4] 賈文濤,張春元,付劍,等.一種高可靠雙機備份星載計算機的設計與實現(xiàn)[C].第六屆中國測試會議,2010.7.