摘 要: 借助頻域傅里葉分析的方法,對傳統(tǒng)PMOS結(jié)構(gòu)LDO系統(tǒng)的穩(wěn)定性進行了仿真建模方法研究,闡述了引起環(huán)路不穩(wěn)定的因素及其影響機制。結(jié)合一例LDO自激振蕩故障的分析,指出故障發(fā)生的原因和相應(yīng)的處理措施。

關(guān)鍵詞: LDO;穩(wěn)定性分析;失效模式;故障診斷

0 引言

低壓差線性穩(wěn)壓器(Low-Dropout Linear Regulator,LDO)因其具有穩(wěn)定性高、噪聲低、功耗低、抗干擾能力強、響應(yīng)快速等優(yōu)點被廣泛應(yīng)用于計算機、網(wǎng)絡(luò)設(shè)備、無線通信設(shè)備及芯片內(nèi)部供電。因此LDO在一定程度上帶動了很多產(chǎn)業(yè)的發(fā)展,具有相當(dāng)廣闊的發(fā)展前景。

環(huán)路穩(wěn)定性作為重要指標(biāo),直接影響LDO在實際使用中能否正常工作。本文以PMOS結(jié)構(gòu)LDO為例,進行小信號建模及瞬態(tài)響應(yīng)分析,并以此為基礎(chǔ)研究一例LDO輸出電壓自激振蕩的故障,得出環(huán)路不穩(wěn)定因素及其影響機制,給出解決的方法。

1 問題背景

某超高頻RFID閱讀器射頻板,工作在UHF頻段(840 MHz~845 MHz,920 MHz~925 MHz),基帶信號接收頻段為40 kHz~640 kHz,系統(tǒng)的低頻噪聲直接影響接收靈敏度指標(biāo)。單板選用的低壓差線性電壓調(diào)整器是一款商用LDO,該LDO具有超低噪聲(48 μVRMS)和高PSRR值(在10 kHz為49 dB),因此被用于大負(fù)載電流的電壓調(diào)整,為前接收鏈路供電。

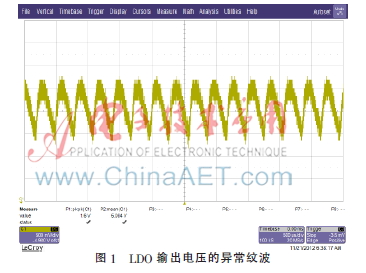

單板調(diào)試過程中,發(fā)現(xiàn)LDO輸出電壓紋波異常(5.4 V~5 V的電平轉(zhuǎn)換),Vpp達到1.6 V,判斷LDO處于正反饋自激振蕩狀態(tài),測試結(jié)果如圖1所示。

LDO電路原理圖如圖2。其中C118和C16是輸入端的去耦電容,C14和C117是輸出端的去耦電容,R61和R34是反饋取樣電阻,C106是反饋補償電容,C15是NR|FB管腳的去耦電容。

2 小信號建模及瞬態(tài)響應(yīng)分析

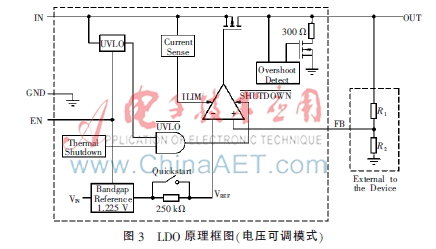

通過查看器件手冊[1],LDO工作在輸出電壓可調(diào)模式。 LDO原理框圖如圖3所示。當(dāng)輸出電壓可調(diào)時,C15是反饋端的旁路電容。新引入的旁路電容與電阻R61形成一個RC濾波,造成反饋取樣信號的延時,反饋端無法及時反映輸出電平的情況,容易造成環(huán)路不穩(wěn)定。從環(huán)路穩(wěn)定性原理也可以得出,當(dāng)LDO穩(wěn)定工作時,旁路電容C15的引入會使C106產(chǎn)生的補償極點頻率減小,環(huán)路帶寬減小,當(dāng)新補償極點的頻率小于單位增益點時,其產(chǎn)生的負(fù)相移會大大增加,系統(tǒng)開環(huán)函數(shù)的相位裕度減小,容易造成環(huán)路不穩(wěn)定,形成正反饋振蕩。

下面將建立LDO的AC小信號模型[2],通過環(huán)路穩(wěn)定性理論來分析故障的原因。

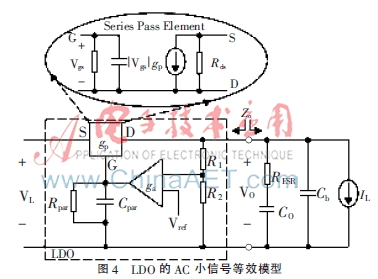

所用LDO是PMOS結(jié)構(gòu)的LDO,如果不考慮過流、過溫保護的情況,芯片正常工作時的等效模型如圖4所示。LDO線性調(diào)整器可以分為4個基本的功能模塊:調(diào)整管(Pass Element)、電壓基準(zhǔn)(Voltage Reference)、誤差放大器(Error Amplifier)和電阻反饋網(wǎng)絡(luò)(Feedback Network,包含電阻R1和R2)。誤差放大器的小信號模型是跨導(dǎo)ga,電容Cpar和電阻Rpar是它的寄生輸出阻抗,同時也是調(diào)整管的柵極輸入阻抗。串聯(lián)調(diào)整管(PMOS晶體三極管)的小信號模型是跨導(dǎo)gp。LDO的輸出電容Co,它的等效串聯(lián)電阻是RESR,Cb是后級各電壓輸入器件的高頻去耦電容,Cb<<Co。

MOSFET共有G、D、S 3個腳,通過G、S間加控制信號可以改變D、S間的導(dǎo)通和截止。PMOS源漏區(qū)的摻雜類型是P型,所以PMOS的工作條件是在柵上相對于源極施加負(fù)電壓,形成從源到漏的源漏電流,|Vgs|=Vsg的值越大,溝道的導(dǎo)通電阻越小,電流的數(shù)值越大。在LDO降壓轉(zhuǎn)換器中,PMOS調(diào)整管作為電壓控制電流源(VCCS),電流I=|Vgs|*gp,其中g(shù)p是跨導(dǎo),它提供穩(wěn)定輸出電壓VO所需的負(fù)載電流IL。輸出電壓VO由R1和R2分壓得到的反饋信號作為誤差放大器(EA)的輸入,與基準(zhǔn)源Vref進行比較放大Verr=ga*(Vfb-Vref),EA輸出調(diào)整PMOS管的柵極電壓,驅(qū)動PMOS管輸出穩(wěn)定電流,從而得到穩(wěn)定輸出電壓VO。由此可見,LDO的穩(wěn)定性即是輸出電壓的穩(wěn)定性,它是由負(fù)反饋網(wǎng)絡(luò)決定的。環(huán)路的負(fù)反饋特性要求EA的兩個輸入電壓相等,即把反饋信號固定在一個參考電平上,因此得到VO=Vref(1+R1/R2)。

模型中幾個變量的常用取值[3]為:

(1)典型的誤差放大器的直流增益為25 dB~45 dB。

(2)寄生電容Cpar一般取值為100 pF~300 pF。

(3)寄生電阻Rpar大約為300 kΩ。

由LDO的小信號等效模型,得到輸出阻抗為:

其中,Rds‖(R1+R2)≈Rds,Co>>Cb,Rds>>RESR。

其中,Rds‖(R1+R2)≈Rds,Co>>Cb,Rds>>RESR。

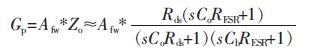

前向通道傳遞函數(shù)為:

其中,Afw指前向通道增益,即PMOS管的增益,設(shè)置Afw=Gpmos=8=18.1 dB(20log)。

反饋通道傳遞函數(shù)為:

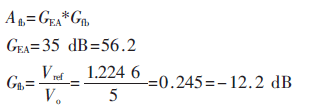

其中,Afb指反饋通道增益,包括反饋分壓網(wǎng)絡(luò)的增益和誤差放大器的增益:

開環(huán)傳遞函數(shù)為:

G(s)=GfGp

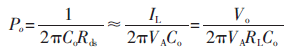

化簡G(s)可找出環(huán)路中的零點(Zero)和極點(Pole),主極點為:

其中, λ為PMOS管的溝道調(diào)制因子。主極點Po由輸出電容Co和負(fù)載電阻RL構(gòu)成,因此又被稱為負(fù)載極點。可以看出,Po與負(fù)載電流有關(guān),當(dāng)負(fù)載電流減小時,Po極點出現(xiàn)在低頻,會減小相位裕度。

λ為PMOS管的溝道調(diào)制因子。主極點Po由輸出電容Co和負(fù)載電阻RL構(gòu)成,因此又被稱為負(fù)載極點。可以看出,Po與負(fù)載電流有關(guān),當(dāng)負(fù)載電流減小時,Po極點出現(xiàn)在低頻,會減小相位裕度。

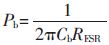

次極點 ,由旁路電容Cb和Co的等效串聯(lián)電阻RESR構(gòu)成。

,由旁路電容Cb和Co的等效串聯(lián)電阻RESR構(gòu)成。

Pb與等效串聯(lián)電阻RESR有關(guān),當(dāng)RESR很大時,Pb極點出現(xiàn)在低頻,同樣會減小相位裕度。

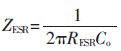

還有一個極點 ,由Cpar和Rpar構(gòu)成,它處于LDO的內(nèi)部。

,由Cpar和Rpar構(gòu)成,它處于LDO的內(nèi)部。

零點 ,由Co和其等效串聯(lián)電阻RESR構(gòu)成。選擇具有合適ESR值的輸出電容可以產(chǎn)生零點,增加相位裕度,以穩(wěn)定LDO系統(tǒng)。

,由Co和其等效串聯(lián)電阻RESR構(gòu)成。選擇具有合適ESR值的輸出電容可以產(chǎn)生零點,增加相位裕度,以穩(wěn)定LDO系統(tǒng)。

通常系統(tǒng)中存在3個極點(Po,Pa,Pb)和一個零點(ZESR),可以近似比較出4個零極點的大小:po<pa<ZESR<pb。

LDO所有輸出電容相并聯(lián),總的ESR要滿足的范圍主要取決于大電容的小ESR值。通常認(rèn)為,電容所含的寄生單元會降低其電性能,ESR是最重要的寄生單元之一。如果在設(shè)計時電容選擇不恰當(dāng),將導(dǎo)致穩(wěn)定性故障,并影響輸出的時域瞬態(tài)響應(yīng)[4]。圖5為典型LDO的頻率響應(yīng)曲線。大多數(shù)LDO都要求其輸出電容的ESR滿足特定范圍,以保證環(huán)路的穩(wěn)定性,并根據(jù)ESR的穩(wěn)定區(qū)間選取合適的電容類型:固體坦電解/鋁電解/多層陶瓷電容。

圖6為LDO當(dāng)輸出電容為10 F時,不同負(fù)載電流所對應(yīng)的ESR穩(wěn)定范圍曲線,作為電容選擇時的參考,即規(guī)定了特定負(fù)載電流和特定輸出容值條件下,其等效串聯(lián)電阻RESR在工作溫度范圍內(nèi)的阻值上限,超過上限會引起環(huán)路不穩(wěn)定。

從圖6可以看出,隨著負(fù)載電流的增大,ESR的取值上限在降低,這是因為隨著Iout增大,主極點Po頻率升高,主極點產(chǎn)生的負(fù)相移減小,因此零點(反比ESR)可以減少正相移的補償,ZESR頻率升高則ESR的取值上限可以相應(yīng)減小。

環(huán)路的穩(wěn)定性補償除了使用輸出電容的等效串聯(lián)電阻RESR來獲取有效的正相移之外,在大多數(shù)輸出可調(diào)LDO穩(wěn)壓器中,都通過在取樣電阻R1上并聯(lián)補償電容CFF來獲得正相移[5]。

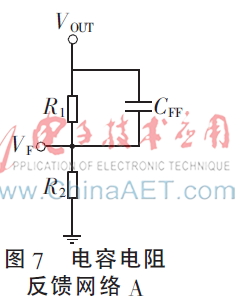

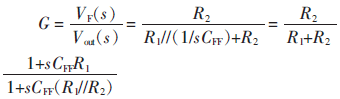

如圖7所示,反饋網(wǎng)絡(luò)由R1、R2和CFF組成,反饋網(wǎng)絡(luò)的傳輸函數(shù)為:

R1、R2和CFF形成一個極點/零點對,這里零點的頻率總比極點的頻率低,零極點頻率由如下公式給出:

FZERO=1/(2×π×CFF×R1)

FPOLE=1/(2×π×CFF×(R1//R2))

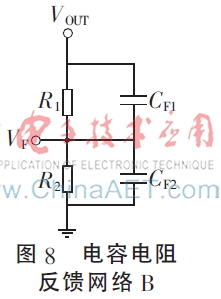

如圖8所示,與原理圖對應(yīng),反饋網(wǎng)絡(luò)由R1、R2和CF1、CF2組成,電容電阻反饋網(wǎng)絡(luò)的傳輸函數(shù)為:

R1、R2和CF1、CF2形成一個新的零/極點對,零極點頻率由以下公式給出:

FZERO=1/(2×π×CF1×R1)

FPOLE=1/(2×π×(CF1+CF2)×(R1//R2))

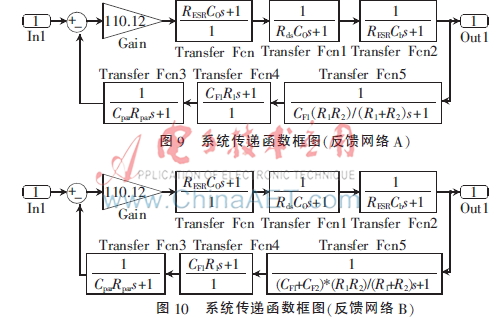

相比于反饋網(wǎng)絡(luò)A產(chǎn)生的零極點對,反饋網(wǎng)絡(luò)B產(chǎn)生的零點頻率不變,極點頻率減小,這就增加了系統(tǒng)的負(fù)相移,使單位增益點(0 dB)頻率對應(yīng)的相位裕度減小,環(huán)路的不穩(wěn)定性增大。

下面根據(jù)實際LDO系統(tǒng)設(shè)置具體參數(shù),通過繪制bode圖得到系統(tǒng)的相位裕度,從而證明,正是CF2取值不當(dāng)使系統(tǒng)的相位裕度減小到不穩(wěn)定區(qū)域,最終導(dǎo)致正反饋振蕩。

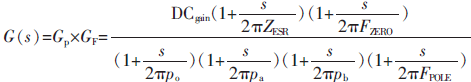

系統(tǒng)開環(huán)傳遞函數(shù)為:

其中,直流增益DCgain=Gpmos×GEA×Gfb=8×56.2×(1.224 6/5)=110.12。

其中,直流增益DCgain=Gpmos×GEA×Gfb=8×56.2×(1.224 6/5)=110.12。

由原理圖知,Co≈47 F,RESR=1 Ω,R1=62 kΩ,R2=20 kΩ,CF1=20 pF,CF2=0.1 ?滋F,Cb=56 pF(SRF=900 MHz),Cpar=200 pF,Rpar=300 kΩ,Rds=65 Ω。

計算得到零極點的分布為:

Po=52 Hz,Pa=2.65 kHz,Pb=2.84 GHz,ZESR=3.39 kHz,F(xiàn)ZERO=128 kHz,F(xiàn)POLE=526 kHz(反饋網(wǎng)絡(luò)A),F(xiàn)POLE′=105 Hz(反饋網(wǎng)絡(luò)B)

由Simulink繪制出系統(tǒng)傳遞函數(shù)框圖分別如圖9和圖10所示。

分別仿真得到它們的bode(波特)圖如圖11所示。

從圖11可以看到,隨著CF2的引入,補償極點的頻率明顯減小(FPOLE→FPOLE′),回路帶寬減小(4.81 kHz→767 Hz),補償極點產(chǎn)生的負(fù)相移明顯增大(-arctan(4.81k/526k)=-0.5°→-arctan(767/105)=-82°),相位裕度由86°減小到8.68°,負(fù)反饋環(huán)路處于不穩(wěn)定狀態(tài),反饋信號與源信號相位相差很小,兩信號相互疊加可能導(dǎo)致正反饋振蕩。根據(jù)仿真結(jié)果,C15容值逐漸減小直到去掉的過程中,相位裕度逐漸增大(8.68°→86°),實測發(fā)現(xiàn)電壓紋波逐漸減小,輸出恢復(fù)穩(wěn)定,與仿真結(jié)論一致。

3 結(jié)論

本文從理論上分析得到PMOS結(jié)構(gòu)LDO的零極點分布,并仿真得到bode圖,通過開環(huán)函數(shù)的相位裕度判斷閉環(huán)系統(tǒng)的穩(wěn)定性,結(jié)果表明補償電容使用不當(dāng)可能引起環(huán)路不穩(wěn)定,導(dǎo)致自激振蕩。根據(jù)仿真結(jié)果給出改進方案,實驗與理論相符合。

參考文獻

[1] Texas Instruments Incorporated. Ultralow-noise, high-PSRR, fast, RF, 1.5-A low-dropout linear regulators[EB/OL].[2014-06-08].http://www.ti.com.cn/cn/lit/ds/symlink/tps 78601.pdf

[2] LEE B S. Understanding the stable range of equivalent series resistance of an LDO regulator[EB/OL]. [2014-06-08].http://www.ti.com.cn/cn/lit/an/slyt187/slyt187.pdf.

[3] Everett Rogers. Stability analysis of low-dropout linear regulators with a PMOS pass element[EB/OL]. [2014-06-08].http://www.ti.com.cn/cn/lit/an/slyt194/slyt194.pdf.

[4] ALLEN G R, ADELL P C, Chen Dakai,et al. Single-event transient testing of low dropout PNP series linear voltage regulators[J]. IEEE Transactions on Nuclear Science, 2012,59(6):2764-2771.

[5] SIMPSON C. LDO regulator stability using ceramic output capacitors[EB/OL]. [2014-06-08].http://www.ti.com/lit/an/snva167a/snva167a.pdf.