摘 要: 采用DSP與FPGA相結(jié)合的方案,設(shè)計了一款雷達回波信號采集卡。此設(shè)備主要用于小型VTS系統(tǒng)、中小型船舶以及航海操縱模擬器中。DSP與FPGA相結(jié)合構(gòu)成快速傳輸通道,為雷達回波采集處理提供有力保障。現(xiàn)場可編程門陣列(FPGA)靈活性強,內(nèi)部邏輯功能可以根據(jù)需要在系統(tǒng)中配置,其作為DSP的輔助芯片為AD提供時鐘,協(xié)同AD完成模擬信號的采集與傳輸,同時完成外部接口的邏輯轉(zhuǎn)換,充分發(fā)揮它的靈活性優(yōu)點。主控芯片DSP主要用于信息處理和整個硬件模塊的控制。

關(guān)鍵詞: FPGA;DSP;雷達回波;采集系統(tǒng)

0 引言

數(shù)據(jù)采集系統(tǒng)是一種應(yīng)用非常廣泛的模擬量測量系統(tǒng),其基本任務(wù)是將模擬信號經(jīng)采樣量化編碼后送入計算機或相應(yīng)的信號處理系統(tǒng)中,然后根據(jù)不同的需要進行相應(yīng)的計算處理。隨著科技的發(fā)展,其應(yīng)用領(lǐng)域涵蓋雷達、電力、空間遙測、汽車制造、軍事等行業(yè)。雷達性能的日益強大離不開數(shù)據(jù)采集系統(tǒng)的發(fā)展,特別是數(shù)據(jù)處理芯片和AD采樣頻率的快速發(fā)展。現(xiàn)在雷達探測距離涵蓋愈來愈廣泛,探測精度越來越高,使得航海安全更具保障。

近年來,隨著加工工藝的突破,處理器的運算速度大幅提高,同時芯片功能更加強大。模擬信號采樣芯片AD的采樣頻率已達到10 GHz。采樣頻率和數(shù)據(jù)處理芯片運算速度的提高推動著數(shù)據(jù)采集系統(tǒng)的發(fā)展。因此,專用的數(shù)據(jù)采集卡日漸成熟,并大量涌現(xiàn)。雷達回波信息數(shù)據(jù)采集可以運用專用的高速數(shù)據(jù)采集卡來采集,實現(xiàn)雷達回波信息的高速實時采集[1]。解放初期我國雷達研制技術(shù)相對比較薄落,航海上雷達的研制幾乎是空白,國內(nèi)的航海雷達幾乎是靠國外進口[1]。隨著這幾年的發(fā)展,尤其改革開放以后,我國經(jīng)濟騰飛,在科技領(lǐng)域與國際先進水平的差距有了明顯的改觀。我國海岸線綿長,隨著漁業(yè)的發(fā)展壯大,船用雷達市場需求打開,雷達專用的數(shù)據(jù)采集卡的普及應(yīng)用將是未來的發(fā)展趨勢。借此本論文提出一種雷達回波信息采集卡的技術(shù)方案。

1 硬件架構(gòu)

1.1 硬件架構(gòu)

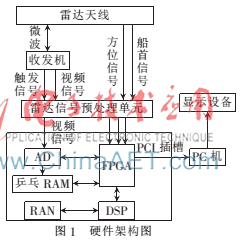

航海雷達由天線、收發(fā)機、雷達信號采集單元和顯示器四部分組成,如圖1所示。本文主要設(shè)計雷達信號采集單元,由天線和收發(fā)機產(chǎn)生的雷達信號包括視頻信號、觸發(fā)信號、方位信號和船首信號,它們不能直接被采集卡采集。為此,以上信號需要預(yù)處理之后才能被采集。信號經(jīng)過轉(zhuǎn)換電路后接入采集卡進行采集處理。采集卡主要芯片采用DSP和FPGA芯片,并使用PCI接口的方式與PC機主板集成,以達到雷達圖像實時精確地顯示采集到的信息。

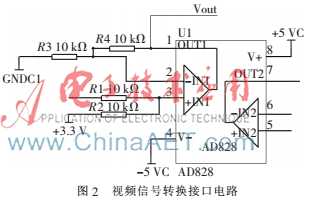

1.2 雷達視頻信號分析

本文以智森雷達RS1712作為實驗雷達,視頻信號幅度為-3.3~0 V,帶寬20 MHz。信號參數(shù)不能直接接入AD采集,需要信號轉(zhuǎn)換,轉(zhuǎn)換接口電路如圖2所示。航海雷達回波信息稱之為視頻信號,是由天線將接收到的高頻信號經(jīng)變頻、檢波后包絡(luò)完成的信號。雷達視頻信號屬于一維信號,回波強弱代表有無目標(biāo)障礙物。雷達回波的采集是實現(xiàn)雷達功能的重中之重,也是雷達系統(tǒng)信息處理最前端的工作部分。

雷達視頻信號不同于傳統(tǒng)意義上的視頻信號,它是利用微波成像原理形成的,回波信號的強弱程度決定了圖像上相對應(yīng)處灰度值的大小[2]。不同障礙物其材質(zhì)、形狀和大小的不同導(dǎo)致反射電磁波的能力不同,雷達根據(jù)障礙物反射電磁波的強弱來呈現(xiàn)出目標(biāo)。雷達視頻信號是通過掃描線刷新來局部變化的圖像。整個雷達圖像是以灰度值的大小和強弱來顯示海面上目標(biāo)物的大小和有無。灰度值越高的點,采集的視頻信號越強。由于視頻信號夾雜大量的雜波,在采集完成后需要以適當(dāng)?shù)拈T限值來限制雜波的影響。雷達天線每旋轉(zhuǎn)一圈形成一幅雷達圖像,圖像以極坐標(biāo)形式顯示。

1.3 雷達脈沖信號分析

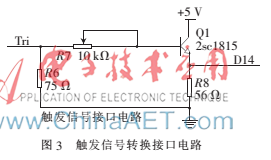

(1)觸發(fā)信號:觸發(fā)信號是整個雷達信號中的重要信號之一,是雷達的總指揮,它控制發(fā)射機、接收機、顯示器同步工作。觸發(fā)信號與接收機收到的雷達視頻回波同步,由此確定一次回波的起點和顯示器上掃描線對應(yīng)的時間。本文實驗雷達觸發(fā)信號幅度約為6 V、脈沖寬度約為33.2 ms,信號參數(shù)不能直接接入采集卡,需要進行信號轉(zhuǎn)換,轉(zhuǎn)換電路如圖3。

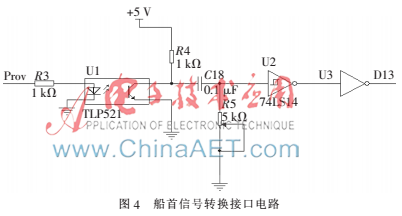

(2)船首信號:天線在旋轉(zhuǎn)過程中,當(dāng)轉(zhuǎn)到正北或者船舶航行方向時雷達產(chǎn)生的信號。由此,該信號可以作為天線旋轉(zhuǎn)一周的標(biāo)志信號,同時可以作為視頻信號處理中分隔兩幅相鄰圖像的標(biāo)志。本實驗雷達的幅度為 +12.5 V。轉(zhuǎn)換電路如圖4。

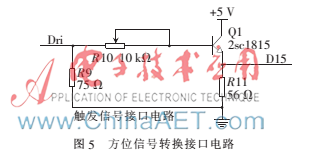

(3)方位信號:方位信號是由天線產(chǎn)生,與天線旋轉(zhuǎn)同步的信號。為了電路簡單雷達在天線底部安裝碼盤,天線每旋轉(zhuǎn)一圈通過碼盤可以產(chǎn)生幾百個增量脈沖,但在顯示器顯示前,利用鎖相倍頻電路將每周的脈沖調(diào)整到4 096或者更高[3]。本實驗雷達天線旋轉(zhuǎn)一周輸出360個方位脈沖,幅度約為+12 V。轉(zhuǎn)換接口電路如圖5。

2 數(shù)據(jù)傳輸

2.1 AD的選擇

本文實驗雷達脈沖重復(fù)頻率為f=1 500 Hz,脈寬τ=0.32  ,則雷達的發(fā)射波形伸展在S=Cτ≈100 m(C為光速)的空間距離上。對于同一方位向上的兩個等同目標(biāo),當(dāng)間隔距離S′=S/2=50 m時,它們在距離上可以被區(qū)分出來,即雷達的距離分辨率為50 m[4]。

,則雷達的發(fā)射波形伸展在S=Cτ≈100 m(C為光速)的空間距離上。對于同一方位向上的兩個等同目標(biāo),當(dāng)間隔距離S′=S/2=50 m時,它們在距離上可以被區(qū)分出來,即雷達的距離分辨率為50 m[4]。

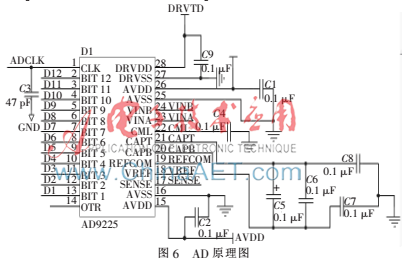

在采樣中如何考慮采樣速率和采樣數(shù)據(jù)精度是一個重要的問題。當(dāng)采樣頻率為f時,可根據(jù)公式△=C/2f(C為光速)得采樣點的距離分辨率,所以為了使采樣結(jié)果能夠無失真地還原出雷達回波,需保證△大于或者等于S,即必須保證采樣速率f>=1/τ。根據(jù)RS1712雷達的性能指標(biāo)參數(shù),雷達視頻信號的帶寬為20 MHz,因此數(shù)據(jù)采樣帶寬要求大于20 MHz,并且數(shù)字化的采樣數(shù)據(jù)精度要求不低于10位。一般要求采樣頻率20 MHz以上,數(shù)據(jù)量大要求傳輸速度與處理速度要相匹配。本文選用AD9225芯片,采集速度25 MS/s,數(shù)據(jù)精度達到12位。圖6為AD部分原理圖。

2.2 快速數(shù)據(jù)流的傳輸

此方案利用FPGA來控制AD的工作。為了提高效率,采用乒乓緩存原理。乒乓緩存結(jié)構(gòu)是在FPGA內(nèi)部開辟出兩個數(shù)據(jù)緩存區(qū)域,將數(shù)據(jù)等時地輸入進去,區(qū)域的選擇由選擇標(biāo)志位決定。在第一個周期內(nèi),將輸入的數(shù)據(jù)緩存到數(shù)據(jù)緩存模塊1中[5];在第二個周期內(nèi),將輸入的數(shù)據(jù)緩存到數(shù)據(jù)緩存模塊2中。以此類推,隨著時間推移,緩存模塊由輸入選擇標(biāo)志位來控制。兩個數(shù)據(jù)緩存區(qū)域緩解DSP處理數(shù)據(jù)的壓力,同時避免數(shù)據(jù)處理錯位。兩個數(shù)據(jù)緩存區(qū)域循環(huán)往復(fù)依次切換數(shù)據(jù)輸入輸出,可以更加有效的進行數(shù)據(jù)采集傳送。以下為FPGA中部分程序。

reg[8:0]data_addr;

always@(posedge ADCLK or posedge RST)

if(RST)

data_addr<=0;

else

data_addr<=data_addr+1;

reg pingpang;

always@(posedge ADCLK or posedge RST)

if(RST)

pingpang<=0;

else if(data_addr==511)

pingpang<=!pingpang;

reg[8:0]dpra;

wire[11:0]dpo1;

wire[11:0]dpo2;

always@(posedge ARE or posedge RST)

if(RST)

dpra<=0;

else if(~CE[2]&&(TEA==4′b0000))

dpra<=dpra+1;

3 技術(shù)方案

數(shù)據(jù)采集是雷達信號數(shù)字處理必不可少的前提,特別對雷達微弱信號的檢測,良好且不失真的數(shù)據(jù)采集是處理的關(guān)鍵[6]。雷達視頻信號數(shù)據(jù)量極大,實時性要求高,為此需要專門的信息采集處理板卡。DSP與FPGA結(jié)合構(gòu)成采集板卡主控芯片。DSP可勝任數(shù)據(jù)處理功能,F(xiàn)PGA能夠提供AD采集接口和數(shù)據(jù)傳輸通道。此外,利用高性能DSP芯片和PCI接口芯片,可有效提高雷達信號采集卡的通用性和擴展能力。采集卡使用德州儀器6000系列6713,這是一款浮點型芯片,運算速度可達1 350 MIPS,搭配一款賽靈思公司的FPGA型號XC2S200。

該板卡采用了一款高速12位的模數(shù)轉(zhuǎn)換芯片AD9225,轉(zhuǎn)換頻率達到25 MHz,可以滿足雷達視頻采集的要求。數(shù)字信號處理模塊以DSP作為核心處理器。DSP外接PROM和SRAM,其中,EEPROM存放程序代碼用于DSP的boot loader,SRAM作為數(shù)據(jù)空間的擴展用于存儲多次回波數(shù)據(jù)。首先,雷達上單元發(fā)出的視頻信號經(jīng)過高速AD采樣后由FPGA控制寫入乒乓RAN中,DSP收到相應(yīng)中斷信號時,讀取數(shù)據(jù)進行處理,處理完成的信號寫入PROM和SRAN等待上位機的讀取。方位信號、船首信號和觸發(fā)信號經(jīng)過預(yù)處理接入FPGA中。方位信號經(jīng)過FPGA電平邏輯轉(zhuǎn)換,由倍頻電路倍頻至4 096 Hz,作為雷達信號的方位基準(zhǔn)傳輸給顯示模塊。觸發(fā)信號作為控制信號接入DSP中斷,由DSP中斷觸發(fā)對視頻信號的采集處理,以達到與上單元同步,同時區(qū)分每條掃描線的視頻信號。船首信號經(jīng)FPGA接入DSP中斷,來觸發(fā)對方位信號和觸發(fā)信號計數(shù)清零處理,同時區(qū)分一幅完整的雷達圖像。FPGA作為DSP的輔助器,協(xié)助DSP控制其外設(shè)器件。另外,為了便于調(diào)試,在板卡中增添串口模塊、JTAG模塊和USB模塊。

3.1 FPGA的功能實現(xiàn)

FPGA負(fù)責(zé)控制AD采樣、讀取采樣數(shù)據(jù)和與DSP通信的任務(wù),以及對脈沖信號進行預(yù)處理[7]。FPGA將對AD的配置參數(shù)寫入其相應(yīng)的寄存器中。將輸入時鐘分頻,產(chǎn)生采樣時鐘提供給AD。同時,F(xiàn)PGA直接對AD下達啟動采樣開始。FPGA監(jiān)測AD的采樣完成信號,若采樣完成則通過AD并行數(shù)據(jù)接口接收一個采樣數(shù)據(jù),送入FPGA內(nèi)部的開辟的乒乓RAN中,同時等待下一個采樣數(shù)據(jù)的到來。當(dāng)FPGA內(nèi)部乒乓RAN存儲滿后溢出標(biāo)志位觸發(fā)DSP中斷,DSP開始從數(shù)據(jù)總線中讀取數(shù)據(jù)處理。

3.2 DSP功能

DSP負(fù)責(zé)數(shù)據(jù)處理和控制整個系統(tǒng)的協(xié)調(diào)運作。觸發(fā)信號、方位信號、船首信號經(jīng)過FPGA時序處理接入DSP中斷,DSP通過對此信號的處理完成對雷達視頻信號的解析,例如控制上下位機協(xié)同工作、確定雷達的分辨率、分割天線掃描一周形成的一幀圖等。DSP有幾個重要的控制中斷:觸發(fā)信號中斷是AD采集開始及一條掃描線數(shù)據(jù)開始標(biāo)志中斷;船首信號中斷是觸發(fā)脈沖和方位脈沖計數(shù)清零標(biāo)志,同時也是一幅完整雷達圖像產(chǎn)生的標(biāo)志,而且由此獲得船首位置;FPGA數(shù)據(jù)溢出標(biāo)志位中斷通知DSP從數(shù)據(jù)總線中讀取采集的雷達數(shù)據(jù)。

3.3 PCI接口

PCI接口是應(yīng)用最為普遍、較為成熟的接口總線。PC機主板中常見的接口總線都能夠方便地與PC連接,并且具有獨立于CPU的結(jié)構(gòu),兼容性好。同時,它具有傳輸速度快、存儲延誤性小、成本低、可編程等優(yōu)點。PCI接口有現(xiàn)成的模塊,故此不再贅述。

4 結(jié)束語

本文設(shè)計的雷達信號采集卡,結(jié)合目前較為先進的硬件芯片,整合各個芯片的優(yōu)點,實現(xiàn)對雷達的回波信號的高速采集。本設(shè)計中相關(guān)FPGA的程序用Xilinx ISE軟件編寫,DSP程序使用CCS軟件完成程序設(shè)計。采用FPGA能夠有效地控制AD的采集,同時,能夠?qū)崟r、高速地把數(shù)據(jù)傳輸出去,為雷達信號的實時采集處理、雷達圖像的實時顯示提供了保障。DSP是傳統(tǒng)的信號處理芯片,運算速度快,能夠在高速數(shù)據(jù)流中發(fā)揮它的優(yōu)勢。

參考文獻

[1] 邱海琴.航海雷達回波數(shù)據(jù)采集與特性研究[D].廈門:集美大學(xué),2011.

[2] 白雅卿.船舶導(dǎo)航雷達視頻信號分析[D].大連:大連海事大學(xué),2013.

[3] 郭鵬.雷達信號數(shù)字化單元研究[D].大連:大連海事大學(xué),2006.

[4] 王立寧.導(dǎo)航雷達回波信號數(shù)據(jù)采集與壓縮技術(shù)研究[D].哈爾濱:哈爾濱工程大學(xué),2009.

[5] 邰林,黃芝平,唐貴林,等.并行緩存結(jié)構(gòu)在高速海量數(shù)據(jù)記錄系統(tǒng)中的應(yīng)用[J].計算機測量與控制,2008,16(4):527-529.

[6] 張亞標(biāo),程家明,閻世強,等.一種雷達弱信號處理的視頻回波數(shù)據(jù)采集系統(tǒng)[J].空軍雷達學(xué)院學(xué)報,2003,17(1):31-33.

[7] 劉歡,田建生,梅安華,等.FPGA+雙DSP結(jié)構(gòu)的雷達信號采集處理系統(tǒng)設(shè)計[J].計算機測量與控制,2005,13(2):157-159.