摘 要: 在X87執(zhí)行環(huán)境下,采用基于Two-Path算法的并行深度流水線優(yōu)化算法,,設(shè)計(jì)了一種能夠?qū)崿F(xiàn)符合IEEE-754標(biāo)準(zhǔn)的單精度,、雙精度和擴(kuò)展雙精度及整型數(shù)據(jù)且舍入模式可控的高速浮點(diǎn)加法器。采用并行深度流水設(shè)計(jì),,經(jīng)驗(yàn)證,,功能滿足設(shè)計(jì)要求,使用TSMC 65 nm工藝庫進(jìn)行綜合,,其工作頻率可達(dá)900 MHz,。

關(guān)鍵詞: 浮點(diǎn)加法器;IEEE-754,;Two-Path算法,;并行流水線

0 引言

浮點(diǎn)運(yùn)算單元(FPU)是微處理器(CPU)的重要組成部分,是進(jìn)行大規(guī)模數(shù)據(jù)運(yùn)算處理的關(guān)鍵技術(shù)[1],。在通用處理器中,,浮點(diǎn)加法指令、浮點(diǎn)減法指令及浮點(diǎn)反轉(zhuǎn)減法指令最終都是使用浮點(diǎn)加法單元來實(shí)現(xiàn)的[2],。浮點(diǎn)加法運(yùn)算過程是由指數(shù)差計(jì)算,、尾數(shù)對階移位、有效數(shù)相加,、前導(dǎo)零計(jì)算,、規(guī)格化操作、例外處理等單獨(dú)操作組成,。通過提高各個操作步驟的并行化,,減少運(yùn)算過程的關(guān)鍵路徑,,可以提高浮點(diǎn)加法運(yùn)算單元的性能[3]。根據(jù)設(shè)計(jì)要求,,對浮點(diǎn)加法單元的結(jié)構(gòu)進(jìn)行并行優(yōu)化,,采用基于Two-Path算法的深度流水設(shè)計(jì),在X87執(zhí)行環(huán)境下進(jìn)行仿真驗(yàn)證,,兼容X87指令集中的浮點(diǎn)加法指令,,包括對控制狀態(tài)寄存器、狀態(tài)寄存器和標(biāo)記寄存器的處理過程,。

1 數(shù)據(jù)格式

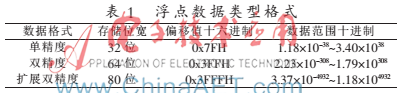

本設(shè)計(jì)兼容IEEE-754浮點(diǎn)標(biāo)準(zhǔn),,IEEE-754標(biāo)準(zhǔn)浮點(diǎn)數(shù)據(jù)具體格式[4]如表1所示。

實(shí)數(shù)Y=(-1)S×F×2E-Bias,,其中:S(sign)為符號位,,F(xiàn)(significand)是有效數(shù)字位,E(exponent)為指數(shù)位,,Bias為偏移值[5],。目前主流計(jì)算機(jī)系統(tǒng)中運(yùn)算數(shù)據(jù)的表現(xiàn)形式均是通過上述表達(dá)式轉(zhuǎn)換而來的。

2 浮點(diǎn)加法單元的算法

2.1 浮點(diǎn)加法單元Two-Path算法

由于傳統(tǒng)浮點(diǎn)加法算法每個步驟之間都是串行執(zhí)行的,,限制了FPU的執(zhí)行效率,,F(xiàn)ARMWARL M P提出的Two-Path算法[6]主要在以下方面進(jìn)行了改進(jìn):

(1)通過判斷指數(shù)差的符號,,對操作數(shù)進(jìn)行交換,,使其總是較大的操作數(shù)在前。除指數(shù)相等的情況外,,數(shù)據(jù)轉(zhuǎn)換這一步驟可以省略,。在指數(shù)相等的情況下,則不需要進(jìn)行對階移位,,有效減法的運(yùn)算結(jié)果是一個精確值,,不必進(jìn)行舍入操作。數(shù)據(jù)轉(zhuǎn)換步驟中的加法與舍入步驟中的加法互斥,,可以將傳統(tǒng)算法中三個全長加法延時(shí)減少一個,。

(2)在有效數(shù)加法的運(yùn)算過程中,,指數(shù)差絕對值△E≦1的情況下,,運(yùn)算結(jié)果一般不會出現(xiàn)多位數(shù)據(jù)有多個零的情況,故不需要對結(jié)果進(jìn)行全長的規(guī)格化移位操作,。當(dāng)指數(shù)差絕對值△E>1時(shí),,有效數(shù)的加法過程只需一個全長的對階移位器。對于有效數(shù)減法,,可以分兩種情況:①如果指數(shù)差絕對值△E≦1,,只需要一個全長的規(guī)格化移位,。這種情況下,,一位的對階移位和尾數(shù)交換條件能夠通過指數(shù)差絕對值的最低位和指數(shù)比較與尾數(shù)比較的結(jié)果來進(jìn)行預(yù)測,。②指數(shù)差絕對值△E>1,則需要一個全長的對階移位器,,但卻不需要超過一位的規(guī)格化移位,。因此,全長的規(guī)格化移位與全長的對階移位是互斥的,,并且在關(guān)鍵路徑上兩種移位器只會出現(xiàn)一個,。上述情況可以表示為:當(dāng)△E≦1且是有效減法運(yùn)算時(shí)為近端(CLOSE)路徑;當(dāng)△E>1時(shí)為遠(yuǎn)端(FAR)路徑,。

?。?)在近端CLOSE路徑中,將有效數(shù)相加和前導(dǎo)零計(jì)算并行處理,,采用前導(dǎo)零預(yù)測直接從兩個源操作數(shù)中預(yù)測出有效加法運(yùn)算后結(jié)果中前導(dǎo)一的位置,,得到規(guī)格化移位量[7]。

2.2 Two-Path并行深度流水優(yōu)化算法

為進(jìn)一步提高浮點(diǎn)加法運(yùn)算單元的性能,,引入了合并舍入的Two-Path算法,。由于舍入計(jì)算的實(shí)現(xiàn)一般要等到運(yùn)算結(jié)果產(chǎn)生后根據(jù)舍入模式才可以執(zhí)行,并且只是對結(jié)果進(jìn)行小數(shù)量的修改,。合并舍入的Two-Path算法需要通路上每一個有效數(shù)的加法器同時(shí)計(jì)算出有效數(shù)相加結(jié)果(sum)和有效數(shù)相加結(jié)果加一(sum+1)兩個運(yùn)算結(jié)果,。為此,浮點(diǎn)運(yùn)算單元的主加法器采用混合加法器來同時(shí)計(jì)算sum和sum+1兩個結(jié)果,,混合加法器是一個專用加法器,,通過共用內(nèi)部硬件單元的方法以減少運(yùn)算規(guī)模。在得到了可能的運(yùn)算結(jié)果之后,,通過分析浮點(diǎn)運(yùn)算結(jié)果的末尾的多位有效數(shù)據(jù)包括最低位(LSB),、警戒位(guard bit)、舍入位(round bit)和粘貼位(sticky bit),,最終選擇需要的結(jié)果,。由于舍入方式的不同,還需要產(chǎn)生一個有效數(shù)相加結(jié)果加2(sum+2)的運(yùn)算結(jié)果,,并且需要一個舍入矯正操作,。在旁路通道上,需要在執(zhí)行主通路時(shí)同時(shí)處理符號位的結(jié)果以及特殊數(shù)據(jù)的運(yùn)算過程,,保證整個設(shè)計(jì)的并行化,。

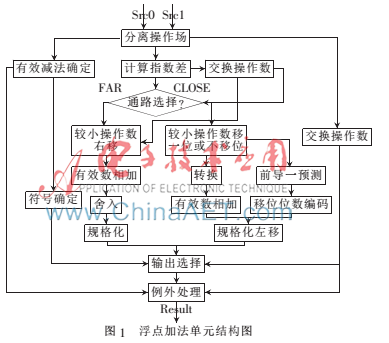

本文基于合并舍入的Two-Path算法提出了一種高速深流水線浮點(diǎn)加法單元設(shè)計(jì),共6級流水線,。第1級完成分離操作場(符號場,、指數(shù)場,、尾數(shù)場),指數(shù)差的計(jì)算以及尾數(shù)大小的比較,;第2級實(shí)現(xiàn)尾數(shù)交換,、有效加減法的判斷、結(jié)果符號預(yù)判,、通路選擇等操作,;第3級完成尾數(shù)對階移位,其中FAR通路是全長對階移位,,CLOSE通路是最多一位的移位,;第4級進(jìn)行有效數(shù)相加和前導(dǎo)零預(yù)測;第5級完成舍入選擇和指數(shù)尾數(shù)規(guī)格化,;第6級完成最終結(jié)果的選擇,、特殊數(shù)據(jù)處理、對例外的標(biāo)記,。其算法結(jié)構(gòu)如圖1所示,,通過Verilog HDL硬件描述語言對算法進(jìn)行實(shí)現(xiàn)。

3 浮點(diǎn)加法單元的實(shí)現(xiàn)與驗(yàn)證

3.1 指數(shù)差計(jì)算

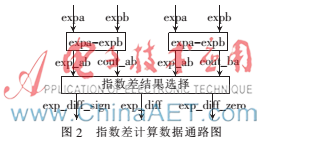

該模塊通過分別計(jì)算|expa-expb|和|expb-expa|,,其中expa為操作數(shù)0的指數(shù),,expb為操作數(shù)1指數(shù)。通過16 bit超前進(jìn)位加法器,,分別得出操作數(shù)0指數(shù)減操作數(shù)1的結(jié)果(exp_ab)及進(jìn)位(cout_ab)和操作數(shù)1指數(shù)減操作數(shù)0的結(jié)果(exp_ba)及進(jìn)位(cout_ba),,從而得到兩個源操作數(shù)的指數(shù)大小關(guān)系:不等于(exp_diff_sign)和等于(exp_diff_zero),以及指數(shù)差的絕對值(exp_diff),,如圖2所示,。

3.2 移位器

設(shè)計(jì)中共有兩個全長移位器,其中一個移位器為 67 bit數(shù)據(jù)尾數(shù)對階移位器,,用來對較小的尾數(shù)進(jìn)行邏輯右移,。通過指數(shù)差判斷移位量,從而得到較小尾數(shù)對階移位后的結(jié)果,。另一個移位器為65 bit數(shù)據(jù)規(guī)格化移位器,,用來對CLOSE通路有效數(shù)相加計(jì)算后的結(jié)果進(jìn)行規(guī)格化左移位。通過前導(dǎo)零預(yù)測得出移位量,,然后對運(yùn)算結(jié)果進(jìn)行移位,,完成規(guī)格化操作。

3.3 加法器設(shè)計(jì)

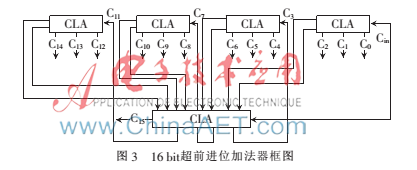

加法器是浮點(diǎn)加法單元最主要的模塊電路,。本設(shè)計(jì)在不同階段的操作過程中運(yùn)用了多種加法器,。實(shí)現(xiàn)16 bit超前進(jìn)位加法器,需要使用4個超前進(jìn)位加法器模塊(CLA)進(jìn)行級聯(lián)[8],。CLOSE通路指數(shù)規(guī)格化同樣采用的是16 bit超前進(jìn)位加法器,,如圖3所示,。

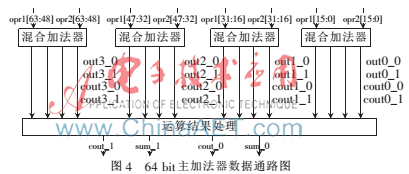

有效數(shù)相加模塊采用64 bit的混合加法器,即采取4個16 bit混合加法器并行計(jì)算,,每個16 bit的混合加法器計(jì)算出16 bit的計(jì)算結(jié)果(out0_0,、out1_0、out2_0,、out3_0)及其進(jìn)位(cout0_0,、cout1_0,、cout2_0,、cout3_0)和計(jì)算結(jié)果加一(out0_1、out1_1,、out2_1,、out3_1)及其進(jìn)位(cout0_1、cout1_1,、cout2_1,、cout3_1),再通過每一級的進(jìn)位來選擇最終結(jié)果(sum_0)及其進(jìn)位(cout_0)和最終結(jié)果加一(sum_1)及其進(jìn)位(cout_1),,如圖4所示,。

3.4 前導(dǎo)零計(jì)算

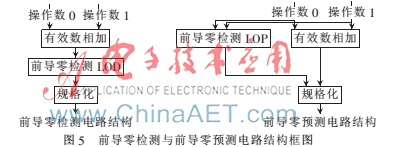

前導(dǎo)零預(yù)測邏輯電路是提高浮點(diǎn)加法器性能的關(guān)鍵。前導(dǎo)零計(jì)算一般有兩種方式:前導(dǎo)零檢測和前導(dǎo)零預(yù)測[9],。前導(dǎo)零檢測處理的是浮點(diǎn)加法運(yùn)算中有效數(shù)相加的結(jié)果,,而預(yù)測處理的是需要進(jìn)行浮點(diǎn)加法運(yùn)算中有效數(shù)相加的兩個有效數(shù),即前導(dǎo)零預(yù)測不需要等待浮點(diǎn)數(shù)加法運(yùn)算有效數(shù)相加的計(jì)算結(jié)果就可以得到前導(dǎo)零的個數(shù),。兩者均可以完成有效數(shù)相加后結(jié)果的前導(dǎo)零的計(jì)算,,但前導(dǎo)零預(yù)測可以與有效數(shù)相加運(yùn)算并行進(jìn)行,很大程度地提高浮點(diǎn)加法運(yùn)算的性能,,圖5為前導(dǎo)零檢測電路結(jié)構(gòu)與前導(dǎo)預(yù)測電路結(jié)構(gòu)框圖,。

3.5 浮點(diǎn)加法運(yùn)算單元的驗(yàn)證

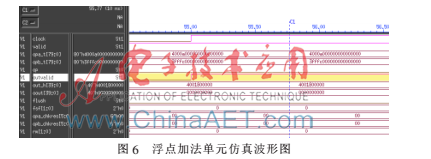

本設(shè)計(jì)功能驗(yàn)證采用VMM測試方法學(xué),通過System verilog系統(tǒng)硬件描述語言搭建對比測試平臺,,產(chǎn)生定向測試激勵和受約束隨機(jī)測試激勵[10],,對本設(shè)計(jì)的運(yùn)算結(jié)果與C模型運(yùn)算結(jié)果進(jìn)行比對,比對結(jié)果一致,,覆蓋率達(dá)到100%,,功能上滿足設(shè)計(jì)要求。圖6為完成一次FADD指令的結(jié)果波形圖,。

4 結(jié)論

本文從浮點(diǎn)加法單元的算法結(jié)構(gòu)入手,,提出了高速深流水線浮點(diǎn)加法單元設(shè)計(jì)。使用TSMC 65 nm工藝庫進(jìn)行綜合,,其工作頻率可達(dá)900 MHz,,兼容X87指令集,,可用于高通量CISC微處理器中。

參考文獻(xiàn)

[1] 張予器.超高精度浮點(diǎn)運(yùn)算的關(guān)鍵技術(shù)研究[D].長沙:國防科學(xué)技術(shù)大學(xué),,2005.

[2] 陳弦,,張偉功,于倫正.并行浮點(diǎn)加法器架構(gòu)與核心算法的研究[J].計(jì)算機(jī)工程與應(yīng)用,,2006,,17(3):53-55.

[3] 夏杰,宣志斌,,薛忠杰.基于流水線結(jié)構(gòu)的浮點(diǎn)加法器IP核設(shè)計(jì)[J].微計(jì)算機(jī)信息,,2008,24(9):192-193.

[4] 朱亞超.基于IEEE 754的浮點(diǎn)數(shù)存儲格式分析研究[J].計(jì)算機(jī)與信息技術(shù),,2006(9):50-52.

[5] Intel Corporation. Intel 64 and IA-32 Architectures Software Developer′s Manual[Z]. U.S: Intel Corporation,,2011.

[6] 王穎,林正浩.快速浮點(diǎn)加法器的優(yōu)化設(shè)計(jì)[J].電子工程師,,2004,,30(11):24-26.

[7] 靳戰(zhàn)鵬.高速浮點(diǎn)加法運(yùn)算單元的研究與實(shí)現(xiàn)[D].西安:西北工業(yè)大學(xué),2006.

[8] 夏有為,,林正浩,,楊曉峰.一款32位嵌入式CPU的定點(diǎn)加法器設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2005,,31(10):76-78.

[9] 李星,,胡春媚,李勇,,等.前導(dǎo)1預(yù)測算法的設(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)科學(xué).2013,,40(4):31-35.

[10] [美]克里斯·斯皮爾.SystemVerilog驗(yàn)證測試平臺編寫指南[M].張春,趙益新,,麥宋平,,譯.北京:科學(xué)出版社,2009.