摘 要: 1553B總線以其可靠性高、實(shí)時(shí)性好、使用靈活等優(yōu)點(diǎn),廣泛應(yīng)用于現(xiàn)代飛機(jī)、導(dǎo)彈、衛(wèi)星、艦艇、坦克等航空、航天、兵器領(lǐng)域,并且逐漸擴(kuò)展到地鐵交通控制等民用領(lǐng)域。而在實(shí)際使用過(guò)程中,1553B總線由于接口配置復(fù)雜,無(wú)法直接與PC進(jìn)行通信,使得系統(tǒng)的安裝調(diào)試存在困難。利用NIOS II軟核處理器面向用戶、靈活定制的特性和USB接口方便、支持熱插拔的優(yōu)點(diǎn),給出了一種在FPGA上已經(jīng)實(shí)現(xiàn)的1553B總線測(cè)試系統(tǒng)設(shè)計(jì)方法。整個(gè)系統(tǒng)硬件設(shè)計(jì)簡(jiǎn)單,軟件設(shè)計(jì)穩(wěn)定可靠,可應(yīng)用于1553B系統(tǒng)調(diào)試和測(cè)試以及各種仿真實(shí)驗(yàn)中。

關(guān)鍵詞: NIOS II軟核處理器;1553B;USB;測(cè)試系統(tǒng)

0 引言

MIL-STD-1553B由美國(guó)在20世紀(jì)70年代提出,具有可靠性高、實(shí)時(shí)性好、靈活性強(qiáng)的特點(diǎn),已經(jīng)發(fā)展成國(guó)際公認(rèn)的數(shù)據(jù)總線標(biāo)準(zhǔn),廣泛應(yīng)用于現(xiàn)代飛機(jī)、導(dǎo)彈、衛(wèi)星、艦艇、坦克等航空、航天、兵器領(lǐng)域,并且逐漸擴(kuò)展到地鐵交通控制等民用領(lǐng)域。我國(guó)從20世紀(jì)90年代初開(kāi)始引進(jìn)1553B數(shù)據(jù)總線,經(jīng)過(guò)十多年的發(fā)展,1553B已經(jīng)成為國(guó)內(nèi)航空航天的主要航電總線之一。國(guó)內(nèi)一些研究機(jī)構(gòu)也通過(guò)不斷努力,已經(jīng)有能力研制生產(chǎn)出符合1553B標(biāo)準(zhǔn)的接口芯片,本文在設(shè)計(jì)中即采用了中國(guó)電子科技集團(tuán)公司第58研究所自主研發(fā)的JBU61580作為1553B總線通信控制器,其與DDC公司的同型號(hào)芯片BU61580完全兼容,支持插拔替換,具有總線控制(BC)、遠(yuǎn)程終端(RT)和監(jiān)測(cè)終端(MT)三大功能[1]。

1 系統(tǒng)硬件設(shè)計(jì)

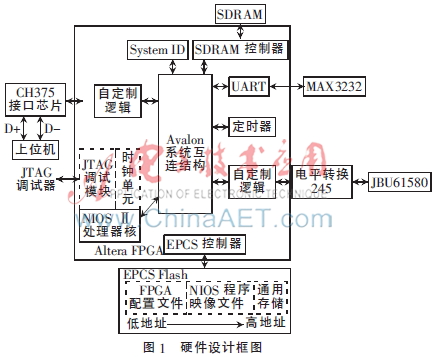

系統(tǒng)采用Altera公司Cyclone Ⅱ系列的FPGA(EP2C8Q208C8)作為主控芯片,內(nèi)嵌NIOS Ⅱ軟核處理器,輸入時(shí)鐘為20 MHz,由PLL倍頻出兩個(gè)100 MHz時(shí)鐘分別提供給NIOS Ⅱ軟核處理器和外接的SDRAM使用。USB接口部分采用CH375芯片,1553B接口部分采用JBU61580芯片,均利用SoPC Builder支持的用戶自定義元件定制時(shí)序轉(zhuǎn)換邏輯,以提高接口芯片的讀寫速度,而NIOS Ⅱ則負(fù)責(zé)兩者之間的數(shù)據(jù)解析和交換。

1.1 總體設(shè)計(jì)思想

硬件原理框圖如圖1所示,整個(gè)系統(tǒng)可以分為5個(gè)部分:(1)系統(tǒng)核心模塊:NIOS Ⅱ處理器;(2)處理器外圍支持電路:時(shí)鐘單元及SDRAM控制器;(3)程序下載調(diào)試模塊:JTAG接口控制器和異步通信接口(UART用于打印調(diào)試信息);(4)系統(tǒng)內(nèi)部外設(shè)模塊:諸如系統(tǒng)ID、定時(shí)器、用戶自定制邏輯等;(5)系統(tǒng)外圍設(shè)備:EPCS存儲(chǔ)器、CH375、JBU61580。

1.2 系統(tǒng)外圍接口設(shè)計(jì)

1.2.1 EPCS接口

系統(tǒng)采用Altera專用的配置芯片EPCS4存儲(chǔ)FPGA的配置數(shù)據(jù)和NIOS Ⅱ的程序,EPCS4總共有4 Mbit的存儲(chǔ)空間,分成8個(gè)64 KB的塊,并通過(guò)專用電路接口與FPGA連接[2]。FPGA的配置數(shù)據(jù)從EPCS4中偏移地址為0的地方開(kāi)始存放,緊接著FPGA的配置數(shù)據(jù)就是NIOS Ⅱ的程序,也就是說(shuō)FPGA的配置數(shù)據(jù)和NIOS Ⅱ的程序從EPCS4的低端地址開(kāi)始存放,而在本設(shè)計(jì)中只占用了不到4個(gè)塊的存儲(chǔ)空間,所以高端塊的存儲(chǔ)空間可以用來(lái)存放JBU61580的配置數(shù)據(jù)。

1.2.2 CH375接口

CH375是一個(gè)USB總線的通用設(shè)備接口芯片,工作在全速模式,兼容USB2.0,其內(nèi)置了USB通信中的底層協(xié)議,具有省事的內(nèi)置固件模式和靈活的外置固件模式[3]。在內(nèi)置固件模式下,屏蔽了相關(guān)的USB協(xié)議,自動(dòng)完成標(biāo)準(zhǔn)的USB枚舉配置過(guò)程,完全不需要本地端控制器作任何處理,簡(jiǎn)化了NIOS Ⅱ的固件編程。本設(shè)計(jì)中CH375芯片只負(fù)責(zé)數(shù)據(jù)的交換,接收上位機(jī)下傳的數(shù)據(jù)和NIOS Ⅱ上傳的數(shù)據(jù)。CH375的8位數(shù)據(jù)總線、4線控制信號(hào)讀選通、寫選通、片選輸入、中斷輸出通過(guò)SoPC自定制邏輯連接到Avalon系統(tǒng)互連結(jié)構(gòu)。

1.2.3 JBU61580接口

JBU61580工作在16位緩沖非零等待模式下,工作電壓為5 V,在3.3 V電壓下工作的FPGA不能與其直接相連,中間需要接總線驅(qū)動(dòng)器245芯片進(jìn)行電平轉(zhuǎn)換。JBU61580的寄存器和存儲(chǔ)器的讀寫控制有兩種方法:一是用PIO口來(lái)模擬JBU61580的讀寫時(shí)序,此方法的優(yōu)點(diǎn)是實(shí)現(xiàn)簡(jiǎn)單,擴(kuò)展性強(qiáng),但讀寫速度比較慢,不利于系統(tǒng)的模塊化與集成;二是根據(jù)HDL語(yǔ)言定制符合JBU61580的時(shí)序控制邏輯,以訪問(wèn)內(nèi)存的方式來(lái)讀寫JBU61580的寄存器和存儲(chǔ)器,此方法實(shí)現(xiàn)稍微復(fù)雜,但是可以極大地提高JBU61580的數(shù)據(jù)讀寫速度。本設(shè)計(jì)中即采用了第二種方法。

2 軟件系統(tǒng)設(shè)計(jì)

由于JBU61580工作在16位緩沖模式,而CH375只有8位數(shù)據(jù)總線,因此上位機(jī)程序要與NIOS Ⅱ約定相同的數(shù)據(jù)封裝格式。上位機(jī)將JBU61580的16位地址和數(shù)據(jù)信息以及一些傳輸控制指令拆分成8位數(shù)據(jù),經(jīng)過(guò)USB總線傳輸,NIOS Ⅱ收到之后再重新解析成16位的地址和數(shù)據(jù)。在配置數(shù)據(jù)全部傳送完成之后,NIOS Ⅱ再根據(jù)控制指令來(lái)配置JBU61580,使其工作在指令要求的模式(BC、RT或MT)下。另外NIOS Ⅱ還將根據(jù)上位機(jī)的指令決定是否將配置數(shù)據(jù)寫入EPCS中,使得單板在上電復(fù)位之后不需要再?gòu)纳衔粰C(jī)獲得配置數(shù)據(jù),從而可以離線工作。處于離線工作狀態(tài),NIOS Ⅱ還應(yīng)實(shí)時(shí)監(jiān)測(cè)CH375的中斷信號(hào),以便接收上位機(jī)的控制指令進(jìn)入聯(lián)機(jī)工作模式。同樣,若NIOS Ⅱ需要上傳JBU61580的通信數(shù)據(jù),也要將讀取的16位數(shù)據(jù)拆分成兩個(gè)8位數(shù)據(jù),再寫入CH375的上傳端點(diǎn)中,上位機(jī)取走數(shù)據(jù)之后同樣按照約定的封裝格式將解析成16位的數(shù)據(jù)顯示出來(lái)。

軟件系統(tǒng)設(shè)計(jì)分為NIOS Ⅱ固件程序和上位機(jī)程序。NIOS Ⅱ固件程序又分為固件主程序、中斷處理程序、數(shù)據(jù)包解析程序。上位機(jī)程序則包括BC模式接口及傳輸控制、RT模式接口及傳輸控制、MT接口及傳輸控制3個(gè)部分。

2.1 NIOS Ⅱ固件程序

2.1.1 固件主程序

固件主程序主要負(fù)責(zé)系統(tǒng)初始化及流程控制。初始化主要包括CH375的工作狀態(tài)測(cè)試、工作模式選擇,JBU61580的初始復(fù)位,讀取并判斷EPCS4配置存儲(chǔ)器的高位地址特征字符以確認(rèn)是否需要單板離線工作等。在初始化之后進(jìn)入主循環(huán),實(shí)時(shí)監(jiān)視USB接口和1553B接口的中斷信號(hào)。

2.1.2 中斷處理程序

中斷處理程序包括CH375中斷處理程序和JBU61580中斷處理程序。由于1553B接口的實(shí)時(shí)要求性高,因此在SoPC系統(tǒng)搭建過(guò)程中,JBU61580的中斷優(yōu)先級(jí)要高于CH375的中斷優(yōu)先級(jí)。

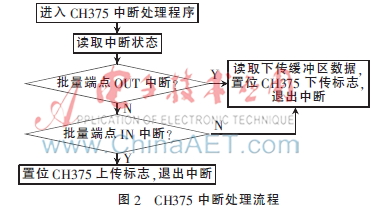

在CH375中斷處理程序中首先讀取中斷狀態(tài),判斷中斷類型,再進(jìn)入相對(duì)應(yīng)的中斷類型處理程序。如果是批量端點(diǎn)接收到數(shù)據(jù),則讀取緩沖區(qū)的數(shù)據(jù),并置位中斷下傳標(biāo)志,退出中斷[4]。如果是批量端點(diǎn)發(fā)送完數(shù)據(jù),則應(yīng)置位中斷上傳標(biāo)志,退出中斷。其流程如圖2所示。

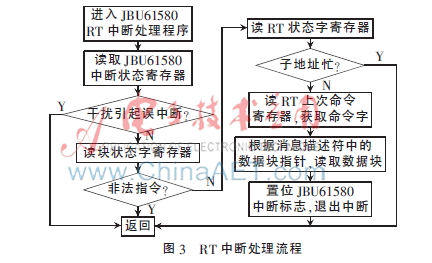

在JBU61580的中斷處理程序中,由于存在BC、RT、MT 3種不同的工作模式[5],則分別對(duì)應(yīng)了不同的中斷處理程序。以RT模式為例,當(dāng)JBU61580接收到來(lái)自1553B總線的與本地址相關(guān)的消息時(shí),若符合中斷條件,將產(chǎn)生中斷。由NIOS Ⅱ進(jìn)行處理,中斷處理程序中首先讀取JBU61580的中斷狀態(tài)寄存器,判斷是否是干擾引起的誤中斷,讀消息描述符中的消息塊狀態(tài)字,判斷是否是非法指令;讀RT狀態(tài)字寄存器,判斷是否是子地址忙;讀取RT上次命令寄存器,獲取命令字;根據(jù)消息描述符中的數(shù)據(jù)塊指針,找到數(shù)據(jù)塊并保存數(shù)據(jù)至消息塊的結(jié)構(gòu)體中[6]。其流程如圖3所示。

2.1.3 數(shù)據(jù)包解析程序

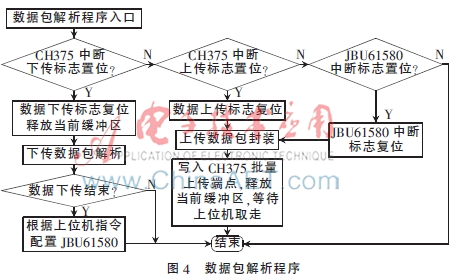

數(shù)據(jù)包解析程序負(fù)責(zé)解析上位機(jī)下傳的8位數(shù)據(jù)及傳輸控制指令,遵從上位機(jī)封裝數(shù)據(jù)的協(xié)定,解析出配置JUB61580的16位地址和對(duì)應(yīng)的數(shù)據(jù),以及一些如啟動(dòng)、復(fù)位等必要的控制指令。另外數(shù)據(jù)包解析程序還要將從JBU61580讀取的16位通信數(shù)據(jù)分拆封裝成8位數(shù)據(jù)寫到CH375的批量上傳端口,等待上位機(jī)取走。數(shù)據(jù)包解析程序如圖4所示。

2.2 上位機(jī)設(shè)計(jì)

CH375在計(jì)算機(jī)端提供了應(yīng)用層接口,應(yīng)用層接口是由CH375動(dòng)態(tài)鏈接庫(kù)DLL提供的面向功能應(yīng)用的API。用戶可以在上位機(jī)軟件中直接調(diào)用這些API,極大地減少了編寫USB設(shè)備驅(qū)動(dòng)的工作量。CH375動(dòng)態(tài)鏈接庫(kù)提供的API包括:設(shè)備管理API、數(shù)據(jù)傳輸API、中斷處理API。上位機(jī)的程序可以分成下傳數(shù)據(jù)和上傳數(shù)據(jù)兩部分,下傳數(shù)據(jù)調(diào)用CH375WriteData()函數(shù)來(lái)實(shí)現(xiàn),上傳數(shù)據(jù)調(diào)用CH375ReadData()函數(shù)來(lái)實(shí)現(xiàn)。由于CH375芯片的上傳緩沖區(qū)和下傳緩沖區(qū)只有64 B,故一次的數(shù)據(jù)傳輸不能超過(guò)64 B。整個(gè)上位機(jī)軟件采用VB2008編寫,圖5是RT控制接口界面。

3 結(jié)論

按照本文的方法已經(jīng)成功實(shí)現(xiàn)了通過(guò)USB實(shí)時(shí)控制JBU61580的1553B總線接口測(cè)試系統(tǒng),整個(gè)系統(tǒng)硬件設(shè)計(jì)簡(jiǎn)單,軟件設(shè)計(jì)穩(wěn)定可靠,可應(yīng)用于1553B系統(tǒng)調(diào)試和測(cè)試以及各種仿真實(shí)驗(yàn)中。

參考文獻(xiàn)

[1] 周遠(yuǎn)林,吳忠,丑武勝.基于BU-61580的1553B總線接口設(shè)計(jì)[J].計(jì)算機(jī)工程與應(yīng)用,2010,46(35):65-68.

[2] 任承志,宋克非,王淑榮.基于BU65170與單片機(jī)系統(tǒng)的RT設(shè)計(jì)與實(shí)現(xiàn)[J].微計(jì)算機(jī)信息,2006,22(6-2):18-20.

[3] 雷勇,吳勇,潘莉.基于USB的1553總線通用接口研究[J].計(jì)算機(jī)測(cè)量與控制,2010,18(4):861-864.

[4] DDC. MIL-STD-1553B Designer′s Guide[S]. 1998.

[5] Condor Engineering Inc. MIL-STD-1553 Protocol Tutorial[S]. 2004

[6] 黃長(zhǎng)春,徐抒巖.基于DSP的1553B總線系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[J].電子設(shè)計(jì)工程,2010(8):4-7.