劉雪亭,,許斌

?。ㄋ拇ㄐ畔⒙殬I(yè)技術(shù)學(xué)院,四川 廣元 6280401)

摘要:設(shè)計(jì)了一種基于FPGA的多路信號智能集成測控系統(tǒng)電路,,其系統(tǒng)電路采用模塊化設(shè)計(jì),,包括電源模塊、多通道模塊,、信號隔離模塊,、ADC模塊、FPGA主控模塊,、通信模塊和電平轉(zhuǎn)換模塊等,。所設(shè)計(jì)的電路將多路信號檢測系統(tǒng)和多路信號控制系統(tǒng)集成在一起,解決了一些需要檢測和控制聯(lián)合應(yīng)用的案例,,且設(shè)備操作簡單,,系統(tǒng)應(yīng)用廣泛,尤其適合于汽車信號控制及檢測等情形,。通過對該電路進(jìn)行仿真和實(shí)際電路的測試,,達(dá)到了對多路信號智能檢測和控制的目的。

關(guān)鍵詞:FPGA,;多路檢測系統(tǒng),;多路控制系統(tǒng);通道切換

0引言

現(xiàn)在市面上常見多路信號檢測設(shè)備能夠檢測的通道數(shù)目最多可達(dá)8路,,信號檢測采樣率一般低于2 MHz,,且僅限于檢測功能,不具備控制功能,。對于一些需要多路低頻信號檢測的系統(tǒng)(如通道數(shù)超過10路時(shí)),,如汽車線路信號通斷檢測等案例,使用通用的示波器無法準(zhǔn)確判斷出各信號間的邏輯關(guān)系,。且儀器儀表的集成化是儀表測量與儀器控制行業(yè)必然的發(fā)展趨勢,,智能化的儀器已逐漸走進(jìn)千家萬戶,,與人們的健康、日常生活,、工作和娛樂活動息息相關(guān)[1],。所以有必要設(shè)計(jì)一款多通道、多用途,、安裝測試方便且具有對多路信號輸出檢測和控制功能的智能集成測控設(shè)備,。

本文設(shè)計(jì)的基于FPGA的多路信號智能集成測控系統(tǒng)裝置,不僅集成了16路信號的檢測,、示波和人機(jī)交互功能,,且能控制各路信號在高電平、數(shù)字地,、浮空輸入,、高電壓輸出4種工作狀態(tài)間轉(zhuǎn)換,并支持對外可調(diào)電源輸出功能,。所研發(fā)的設(shè)備操作簡單,,系統(tǒng)應(yīng)用廣泛,尤其適合于汽車信號控制及檢測等情形,,解決了一些需要檢測和控制聯(lián)合應(yīng)用的案例,。經(jīng)理論仿真和實(shí)物制作測試,驗(yàn)證了本電路達(dá)到了對多路信號檢測和控制智能集成的目的,。

1多路信號智能集成測控系統(tǒng)電路設(shè)計(jì)

1.1系統(tǒng)總體設(shè)計(jì)框圖

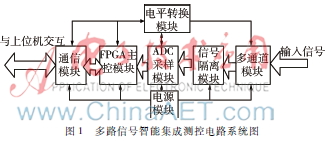

圖1多路信號智能集成測控電路系統(tǒng)圖該系統(tǒng)電路采用模塊化設(shè)計(jì),,包括電源模塊、多通道模塊,、信號隔離模塊,、ADC模塊、FPGA主控模塊,、通信模塊和電平轉(zhuǎn)換模塊,。系統(tǒng)框圖如圖1所示。輸入信號連接多通道模塊,,完成16路信號的通道切換,。再通過信號隔離模塊實(shí)現(xiàn)對信號的緩沖、隔離,,經(jīng)過ADC采樣模塊完成模數(shù)轉(zhuǎn)換,,ADC模塊還與FPGA主控模塊連接,實(shí)現(xiàn)對ADC輸出信號的采集,。FPGA主控模塊與通信模塊連接,,其通信模塊完成一個USB到串口的轉(zhuǎn)換,F(xiàn)PGA通過指令實(shí)現(xiàn)對16路通道的控制,,從而實(shí)現(xiàn)通信模塊與上位機(jī)的通信,,使系統(tǒng)具有人機(jī)界面的簡易測控交互功能,。電源模塊為各單元電路提供工作電壓,包括對外輸出可調(diào)穩(wěn)壓源和內(nèi)部電源管理兩部分,。其電平轉(zhuǎn)換模塊完成不同電平之間的轉(zhuǎn)換,,滿足不同電路的輸入、輸出供電電壓,。

1.2多通道切換模塊和信號隔離模塊

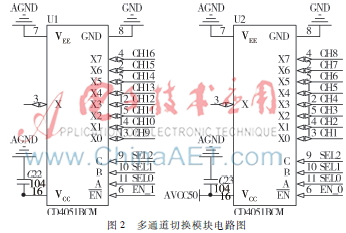

CD4051是單8通道數(shù)字控制模擬電子開關(guān),,有A、B和C三個二進(jìn)制控制輸入端以及INH共4個輸入,,具有低導(dǎo)通阻抗和很低的截止漏電流,。在采集板上通過2顆CD4051的級聯(lián)構(gòu)成16路的通道切換,其電路如圖2所示,?!?/p>

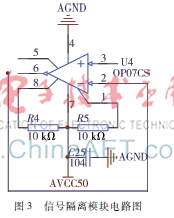

圖3信號隔離模塊電路圖在采集板中,,信號從模擬電子開關(guān)輸出后,,為了減少開關(guān)的切換噪聲對采樣的影響,采用運(yùn)放OP07構(gòu)成一個射隨電路,,實(shí)現(xiàn)信號的隔離,,其電路如圖3所示。OP07芯片是一種低噪聲,、非斬波穩(wěn)零的雙極性(雙電源供電)運(yùn)算放大器集成電路,,同時(shí)具有輸入偏置電流低和開環(huán)增益高的特點(diǎn),這種低失調(diào),、高開環(huán)增益的特性使得OP07特別適用于高增益的測量設(shè)備和傳感器微弱信號放大等方面,。

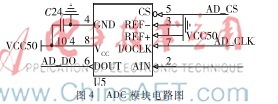

1.3ADC模塊

采集板采用TLC549芯片完成信號的采樣,其電路如圖4所示,。TLC549是TI公司生產(chǎn)的一種高性能的8位A/D轉(zhuǎn)換器[2],,采用了CMOS工藝,它以8位開關(guān)電容逐次逼近的方法實(shí)現(xiàn)A/D轉(zhuǎn)換,,其轉(zhuǎn)換時(shí)間小于17 μs,,最大轉(zhuǎn)換速率為 40 000 Hz,4 MHz典型內(nèi)部系統(tǒng)時(shí)鐘,。TLC549可以通過三線SPI總線方式完成與FPGA的交互,。其供電為5 V,所以其信號輸入范圍為0~5 V,,可以滿足外部輸入信號的動態(tài)電壓范圍,。

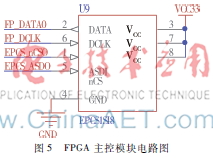

1.4FPGA主控模塊

以FPGA為邏輯控制核心完成16路數(shù)據(jù)的接收和緩存[3],其主控芯片采用靈活性較好的可編程邏輯器件EP1C3T144C8N,,該FPGA芯片完成RS422的發(fā)送和接收,,RS422信號的解碼,、通道的控制和ADC的采集。因?yàn)镕PGA是掉電丟失,,所以配置一顆PROM,,型號為EPCS1N,容量為1 MB,,通過AS配置模式,,可以將程序下載到該P(yáng)ROM中。在系統(tǒng)上電時(shí),,F(xiàn)PGA會自動加載PROM里的程序到內(nèi)部運(yùn)行,。如圖5所示的電路中,F(xiàn)PGA采用48 MHz時(shí)鐘輸入,,由一顆3.3 V供電的有源晶振提供,。

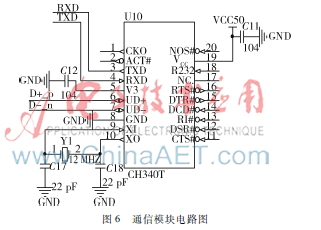

1.5通信模塊

通信采用CH340完成一個USB到串口的轉(zhuǎn)換,使人機(jī)界面模塊通過USB接口與系統(tǒng)硬件連接,。CH340是一個USB總線的轉(zhuǎn)接芯片,,能實(shí)現(xiàn)全速USB設(shè)備接口,兼容USB 2.0,,它有硬件全雙工串口,,內(nèi)置收發(fā)緩沖區(qū),支持通信波特率50 b/s~2 Mb/s,。在采集板上,,該芯片采用5 V供電,通過少量的外圍電路即可構(gòu)成一個高效的傳輸鏈路,。

電路如圖6所示,,C17和C18是起振電容,幫助晶體Y1快速穩(wěn)定地輸出時(shí)鐘信號,。USB信號D+_p和D-_n是一對差分信號,,在PCB布線,保證這兩條線等長,,這樣能提高通信的可靠性,。

1.6電源模塊和電平轉(zhuǎn)換模塊

電源模塊由AC到DC的轉(zhuǎn)換模塊和DC到DC的升壓模塊兩部分組成。ACDC轉(zhuǎn)換模塊將AC 24V轉(zhuǎn)變成DC 12 V,,DCDC升壓模塊將DC 12 V變成DC 12~48 V可調(diào),。采集板采用USB供電,并通過AMS11173.3和AMS11171.5分別產(chǎn)生3.3 V電壓和1.5 V電壓,。整板共有3個電壓,,3.3 V是FPGA的I/O電壓,1.5 V是FPGA的核電壓,5 V是FPGA外圍器件的電壓,。采集板是數(shù)?;旌想娐罚瑸榱诵盘柕耐暾?,數(shù)字電路和模擬電路分圖9Quartus環(huán)境下仿真時(shí)序圖開,,并采用單點(diǎn)接地。

在采集板中,,大量的外設(shè)都用了5 V的電壓,,但是FPGA的I/O電壓為3.3 V,所以在FPGA和外設(shè)的交互過程中,,需要進(jìn)行電平轉(zhuǎn)換,。電平轉(zhuǎn)換芯片SN74ALVC164245有A、B兩路,,共16對信號,,可以完成3.3 V和5 V信號之間的相互轉(zhuǎn)換。

A,、B兩路的信號轉(zhuǎn)換方向和使能都可以單獨(dú)控制,。

2電路仿真和測試

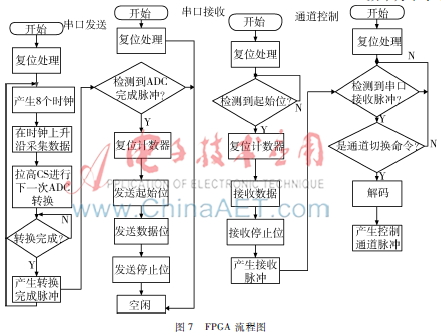

2.1FPGA的控制

FPGA的數(shù)據(jù)交換有串口通信和并口通信,在本設(shè)計(jì)中采用串口通信,,因其簡單且實(shí)時(shí)性好而被采用[4],。FPGA流程圖如圖7所示,,實(shí)現(xiàn)串口發(fā)送,、串口接收和通道控制過程。其FPGA串口控制時(shí)序電路內(nèi)部設(shè)計(jì)如圖8所示,,F(xiàn)PGA串口控制時(shí)序仿真如圖9所示,。

2.2上位機(jī)軟件LabBiew的仿真測試

上位機(jī)軟件主要完成數(shù)據(jù)采集、波形顯示和通道的切換控制,,采用LabView軟件來編寫實(shí)現(xiàn),。LabView提供了非常豐富的圖形界面來進(jìn)行前面板的設(shè)計(jì),在該頁面中實(shí)現(xiàn)了多通道采集的波形以及所有通道采樣的波形的實(shí)時(shí)顯示[5],。運(yùn)行LabView采集軟件,,設(shè)置串口號為USB轉(zhuǎn)串口芯片中被設(shè)置的串口號,然后設(shè)置波特率為115 200 b/s,,點(diǎn)擊串口,,此時(shí)指示燈變綠,表示數(shù)據(jù)已經(jīng)連接上,,并開始接收數(shù)據(jù)并在圖上顯示,。在16路通道選擇下拉菜單中選擇所需要設(shè)置的通道號,然后點(diǎn)擊“設(shè)置通道”按鈕完成通道的選擇,連接好測試線路,,其仿真效果如圖10~13所示,。

在LabView采集軟件下,信號檢測通道數(shù)為16,,采樣頻率為不小于2 MHz,。通過FPGA搭建硬件平臺,與LabView上位機(jī)軟件實(shí)現(xiàn)串口通信,,實(shí)時(shí)調(diào)整采樣波形[6],。從圖10可以看出,給采集板的通道1外加一個具有高,、低電平的方波時(shí),,設(shè)置通道選擇的“通道1”,PC友好地展示了高,、低電平的方波狀態(tài),,可以檢測16路信號的通斷狀態(tài);若設(shè)置其他任意通道,,如圖11的10通道時(shí),,則顯示的是雜亂波形;若給采集板的通道1浮空輸入,,則PC也會出現(xiàn)雜亂波形,;若給采集板的通道1外加一個正常狀態(tài)的三角信號,則其PC也友好地展示了其正常的三角狀態(tài),,如圖12所示,;若給采集板的通道1數(shù)字接地,則PC顯示圖13所示的0信號,??梢姡▓D10通道1的方波過系統(tǒng)性能的測試證明,,所設(shè)計(jì)的電路集成了16路信號的檢測,、示波和人機(jī)交互功能,且能控制各路信號在高電平,、數(shù)字地,、浮空輸入、高電壓輸出4種工作狀態(tài)間轉(zhuǎn)換,,將多路檢測與多路多狀態(tài)控制有效地集成在一起,。

3結(jié)論

本文設(shè)計(jì)了基于FPGA的多路信號智能集成測控系統(tǒng)裝置,通過具體的仿真分析和對實(shí)際電路的測試,,結(jié)果表明該系統(tǒng)通過16路模擬開關(guān)模塊與上位PC中的人機(jī)界面,,完成了對外16路信號的檢測和控制。該系統(tǒng)人機(jī)界面友好,易上手,,方便操作,。在不對外供電時(shí),系統(tǒng)耗電低,,小于10 W,。所設(shè)計(jì)的設(shè)備可應(yīng)用于多路低頻信號(如車載CAN總線)的檢測及多路數(shù)字線路間邏輯關(guān)系的判斷應(yīng)用,以及用于多芯信號線通斷檢測等情況,,有很高的應(yīng)用價(jià)值,。

參考文獻(xiàn)

[1] 孫傳友,,李濤.測控系統(tǒng)原理與設(shè)計(jì)[M].北京:北京航空航天大學(xué)出版社,,2014.

[2] TI.TLC548C,TLC548,TLC549C,TLC549I8BitanalogToDigital Converters,,with serial control[Z].2000.

?。?] 田博,陳分雄,,郭星鋒,,等.基于FPGA的多路無線信道監(jiān)聽系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2014,,40(5):8789,,96.

[4] 侯朝勇,,胡學(xué)浩,,莊童.基于FPGA的多路同步實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)[J].電子技術(shù)應(yīng)用,2009,,35(10):103105.

?。?] 吳建,裴峰.基于Labview的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[J].電子測試,,2013,1(2):5254.

?。?] 梁赫西,,周密,謝虎城,,等.基于FPGA與LabVIEW的DDS任意信號發(fā)生器設(shè)計(jì)[J].微型機(jī)與應(yīng)用,,2015,34(2):2528.