王青,俞建定,袁飛,周彬彬

(寧波大學(xué) 信息科學(xué)與工程學(xué)院, 浙江 寧波 315211)

摘要:近年來,隨著科技和工業(yè)的快速發(fā)展,絕對值編碼器在其通信技術(shù)方面也在逐步地優(yōu)化與完善,其中SSI協(xié)議的輸出方式在絕對值編碼器領(lǐng)域中應(yīng)用比較廣泛。詳細(xì)闡述了SSI協(xié)議的通信方式,設(shè)計出硬件電路,并采用Verilog語言實現(xiàn)了SSI通信協(xié)議。通過測試實驗,證明了該應(yīng)用系統(tǒng)抗干擾性強、性能可靠、通信速度快,具有潛在的市場價值。

關(guān)鍵詞:絕對值編碼器;SSI協(xié)議;Verilog

0引言

近年來,編碼器應(yīng)用比較多,主要應(yīng)用于工業(yè)控制系統(tǒng),比如電機的轉(zhuǎn)速測量、機床位置的測量、起重機上升距離的測量等,同時編碼器在市場上的規(guī)模越來越大,工業(yè)的需要量也逐步增長。在未來的幾十年里,編碼器行業(yè)將會達(dá)到高速發(fā)展的階段,將會有更多的編碼器生產(chǎn)廠商參與這場革命的競爭。

編碼器是將數(shù)據(jù)轉(zhuǎn)換成信號形式的一種設(shè)備,這種信號可以用來通訊、傳輸和存儲[1]。編碼器的原理是把這些物理位移變換成熟知的電信號。按工作性質(zhì)劃分,編碼器可以劃分成兩大類:增量型編碼器和絕對值編碼器[2]。增量型編碼器主要應(yīng)用在那些精度要求不高的儀器上。而針對那些精度要求比較高的行業(yè),一般都是重工業(yè),比如設(shè)備制造業(yè)、電子工業(yè)等,通常會采用絕對值編碼器。因為絕對值編碼器具有啟動速度快、數(shù)字編碼、位置唯一等特點,所以它已經(jīng)被廣泛地應(yīng)用在各種工業(yè)系統(tǒng)中[3]。隨著儀器儀表越來越智能化,人們對編碼器提出功耗低、質(zhì)量好、體積小的要求,希望在絕對值編碼器的領(lǐng)域中有更多類型的輸出方式,讓越來越多的裝置能夠?qū)崿F(xiàn)自動化。

早期的絕對值編碼器的輸出大多采用并行輸出方式,然而隨著科技的進(jìn)步,絕對值編碼器的輸出方式也越來越豐富,出現(xiàn)了比如RS485、PROFIBUSDP、CAN、DeviceNet 等現(xiàn)場總線輸出方式、模擬信號轉(zhuǎn)換輸出方式以及SSI協(xié)議同步串行輸出方式等[4]。這幾種輸出方式都有各自的優(yōu)點和缺點。并行輸出適用于短距離傳輸,其價格比較低廉;現(xiàn)場總線型輸出一般適用于超大規(guī)模的工業(yè)領(lǐng)域中,但是價格比較昂貴;而模擬信號轉(zhuǎn)換輸出方式目前應(yīng)用相對比較少。這幾種輸出方式比較而言,SSI 串行輸出方式的優(yōu)點比較多,比如抗干擾能力強、接線少,因此市場上應(yīng)用比較廣泛。

1工作原理描述

1.1增量型編碼器工作原理

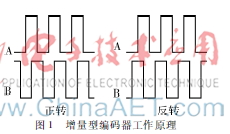

增量型編碼器的工作原理是先將位移變成具有周期性的電信號,然后把這個信號轉(zhuǎn)換成計數(shù)脈沖,通過這樣的轉(zhuǎn)變,位移就可以通過脈沖輸出的多少來測量[5]。如圖1所示,當(dāng)A相超前B相時,表示正轉(zhuǎn),反之則反轉(zhuǎn)。增量型編碼器主要依靠計數(shù)來記憶其位置,但是在突然斷電時,如果編碼器稍微移動,那么再來電時,記憶的零點就會偏移,造成不精確和記憶損失。需要增加參考點,也就是Z相,用參考位置來處理這些問題。但是此類型編碼器每次操作都要先找參考點,抗干擾能力比較差,零點累計時也有誤差。如果選用絕對值編碼器這些問題都可以得到解決。

1.2絕對值編碼器工作原理

絕對值編碼器的碼盤上有很多道光通刻線,它們依次以2線、4線、8線、16線……這樣的方式進(jìn)行排列[6]。這些刻線都有兩面,分別為陰面和陽面,通過讀取每道刻線的通、暗得到一組從20~2n-1的唯一的二進(jìn)制編碼(格雷碼),這就是n位絕對值編碼器[7]。每一個位置對應(yīng)一個具體的數(shù)字,這個數(shù)字是絕對唯一的,只與起始和終止有關(guān),與中間任何過程都沒有關(guān)系。當(dāng)遇到突然斷電,重新啟動時不用重新再找參考點和零點,也不用像增量型編碼器那樣重新記錄脈沖的數(shù)目。任何時候想要知道它的具體位置,都可以去讀取它。這種編碼器的數(shù)據(jù)可靠、不容易受外界影響。

1.3SSI協(xié)議介紹

絕對值編碼器主要是把需要測量的位置信息傳輸給主控制系統(tǒng),然后通過主控制系統(tǒng)來發(fā)出控制信號[8]。以前的絕對值編碼器大多采用并行輸出,在位數(shù)不多的情況下可以適用,一旦位數(shù)越來越多,則并行輸出就不適用了,因為總是出現(xiàn)數(shù)據(jù)不準(zhǔn)確、錯誤等。比如在傳輸過程中,只要有一根數(shù)據(jù)線出現(xiàn)問題,就會影響到最終傳輸?shù)臄?shù)據(jù),從而影響到絕對值編碼器的正常工作。所以根據(jù)實際情況,SSI協(xié)議的輸出方式比較適合。它用串行輸出來替代并行輸出,通過采用差分的方式來提高數(shù)據(jù)在傳輸過程中的可靠性,抗干擾明顯增強,同時為了通信雙方能夠準(zhǔn)確地發(fā)送和接收數(shù)據(jù),故采用同一個波特率。

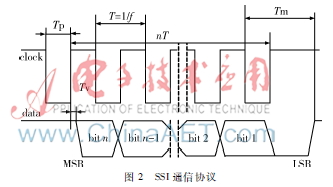

SSI協(xié)議的通信方式如圖2所示。其采用主動讀取和接收的方式,包括同步時鐘信號CLOCK、數(shù)據(jù)信號DATA,其中同步時鐘的頻率決定了數(shù)據(jù)在傳輸過程中的速率。在工業(yè)控制應(yīng)用領(lǐng)域中,通過實際傳輸距離的遠(yuǎn)近來選擇需要的頻率。在同步時鐘信號的控制下,從最高位(MSB)開始傳送[9]。當(dāng)遇到時鐘信號的第一個下降沿時,在Tp這段時間內(nèi),把需要發(fā)送的數(shù)據(jù)進(jìn)行保存,之后遇到時鐘信號的每一個上升沿時就開始發(fā)送數(shù)據(jù),直到所有的數(shù)據(jù)發(fā)送完即結(jié)束。然后把數(shù)據(jù)輸出這一端拉至低電平,延長Tm時間之后再把數(shù)據(jù)輸出端拉至高電平,準(zhǔn)備等待下一個時鐘信號的到來,繼續(xù)發(fā)送數(shù)據(jù)。在不發(fā)送數(shù)據(jù)時,時鐘信號和數(shù)據(jù)端都應(yīng)該保持高電平。圖2SSI通信協(xié)議

其中需要發(fā)送數(shù)據(jù)的位數(shù)決定了發(fā)送同步時鐘的個數(shù)。圖2中參數(shù)定義如下: T為時鐘頻率, Tp為數(shù)據(jù)之間傳輸間隔,Tm為單穩(wěn)觸發(fā)時間,n為傳輸位數(shù),MSB為最高有效位,LSB為最低有效位。

2系統(tǒng)方案設(shè)計

主控制器可以選擇51單片機、RAM微處理器和CPLD邏輯器件。單片機結(jié)構(gòu)簡單,價格便宜,但是運行速度很慢,處理速度有限,抗干擾能力也不是很強;RAM微處理器功能強大,但是開發(fā)周期長,價格昂貴。要想高速傳輸,采用CPLD設(shè)計比較靈活,其處理速度比較快,抗干擾能力也很強,并且設(shè)計時用到大量的時序和邏輯運算。

2.1硬件設(shè)計

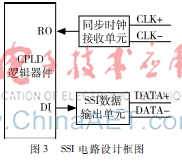

SSI電路的輸入和輸出都采用差分方式,如圖3所示,有4根信號線: CLK+、CLK-、DATA+、DATA-,其中CLK+和CLK-為時鐘輸入端,DATA+和DATA-為數(shù)據(jù)輸出端。時鐘輸入端的接收采用光耦,數(shù)據(jù)端的輸出采用422輸出芯片。圖3SSI電路設(shè)計框圖

2.2軟件設(shè)計

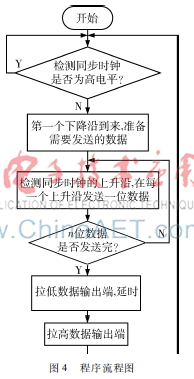

對于軟件部分的設(shè)計,有兩種方法可以實現(xiàn)SSI協(xié)議,一種方法是用單片機模擬SSI通信,另外一種是用CPLD來實現(xiàn)SSI通信。用單片機模擬的關(guān)鍵技術(shù)主要包括兩個方面:同步時鐘信號的準(zhǔn)確獲取和數(shù)據(jù)起始位的準(zhǔn)確判斷[10]。很明顯,這需要輸入端口和輸出端口,另外還需要一個定時器來實現(xiàn)單穩(wěn)態(tài)觸發(fā)器。在輸入端口捕獲時鐘的上升脈沖,遇到時鐘的第一個下降脈沖時定時器開始工作。數(shù)據(jù)傳輸結(jié)束時定時器需要復(fù)位重新開始計數(shù)。軟件流程圖如圖4所示。

用單片機來模擬SSI通信,結(jié)構(gòu)比較簡單,但是通信速度會受到約束。所以要想實現(xiàn)高速通信必須采用CPLD。CPLD的軟件部分設(shè)計可以分為兩個部分,一部分是單穩(wěn)態(tài)觸發(fā)器,在外加脈沖的作用下,可以從一個穩(wěn)定狀態(tài)翻轉(zhuǎn)到一個暫穩(wěn)態(tài)。它的輸入為同步時鐘上升沿,在一段時間內(nèi)如果沒有遇到上升脈沖,則將輸出信號復(fù)位。另一部分是一個并入串出的移位寄存器,在單穩(wěn)態(tài)觸發(fā)器圖4程序流程圖輸出復(fù)位信號后,將需要發(fā)送的數(shù)據(jù)存入寄存器,繼續(xù)等待下一個周期的移位時鐘。并串轉(zhuǎn)換的寄存器用Verilog語言描述如下:

Always@ (posedge clock or posedge load)

Begin

If(load==1.b1)

Out<=indata[24: 0];

Else

Out[24: 0]<=Out{[23: 1], 1.b0}

End

3結(jié)論

本文分別從硬件和軟件兩個方面進(jìn)行研究和設(shè)計,實現(xiàn)了絕對值編碼器的SSI通信協(xié)議,設(shè)計出的SSI通信板,成功與西門子S7300系列PLC配置的SM338模塊進(jìn)行通信,PLC能夠正確讀出碼值。根據(jù)市場分析,在工業(yè)控制領(lǐng)域中,具有SSI協(xié)議的絕對值編碼器實用性比較強,應(yīng)用比較多,因此本文的研究具有潛在的市場價值。

參考文獻(xiàn)

[1] 張麗娟.關(guān)于電氣傳動設(shè)備手動控制增加自動模式方法[J].陰山學(xué)刊(自然科學(xué)版),2013,27(1):8183.

[2] 王仲亮,楊廣,薛秀生,等.基于RS485總線的多編碼器數(shù)據(jù)采集系統(tǒng)研制及改進(jìn)驗證[J].測控技術(shù),2014,33(11):144145,149.

[3] 韋鳳. 淺談光電編碼器的應(yīng)用[J].科技風(fēng),2014(6):97.

[4] 陳志同. 基于SSI協(xié)議的絕對值編碼器通信接口研究[D].天津:天津理工大學(xué),2014.

[5]肖博,李劍鋒,陳洪芳,等.多通道絕對式光電編碼器數(shù)據(jù)采集系統(tǒng)[J].儀表技術(shù)與傳感器,2013(1):2729.

[6] 彭雨. 基于FPGA的絕對式光電編碼器通信接口研究[D].武漢:華中科技大學(xué),2008.

[7] 王文. 基于平臺羅經(jīng)的穩(wěn)定平臺控制系統(tǒng)研究[D].成都:電子科技大學(xué),2009.

[8] 胡東軒. 永磁交流伺服系統(tǒng)多種位置檢測與集成方法研究[D].杭州:浙江理工大學(xué),2014.

[9] 靳紅濤,趙勇進(jìn),陳朝基,等. 一種SSI接口光電編碼器數(shù)據(jù)并行采集設(shè)計方法[J].電子技術(shù),2008,45(5):2325.

[10] 聶旭中. 編碼器用SSI協(xié)議及實現(xiàn)[J].洛陽師范學(xué)院學(xué)報,2010,29(2):7375.